FIFO,先進先出。在FPGA中使用的FIFO一般是指對數據的存儲具有先進先出的緩沖器,FIFO與普通的存儲器的不同在于它沒有讀寫地址線。舉個例子,當FPGA從外部傳感器讀取到一連串數據時,首先被寫入FIFO中,然后FPGA再以UART串口通信依次將數據發送出去。因為傳感器采集數據的速度很快,比如當傳感器使用SPI通信協議,以2M的SPI數據速率讀取時,串口使用9600的波特率肯定跟不上,因此需要先將從傳感器處采集的數據使用FIFO緩存起來,然后再使用串口緩慢發送出去。

01 單時鐘FIFO

單時鐘FIFO具有一個獨立的時鐘端口,所有輸入信號的讀取都是在該時鐘端口信號的上升沿進行的,所有輸出信號的變化也是在該時鐘信號的上升沿的控制下進行的,單時鐘FIFO的所有輸入輸出信號基本都是和時鐘信號同步。

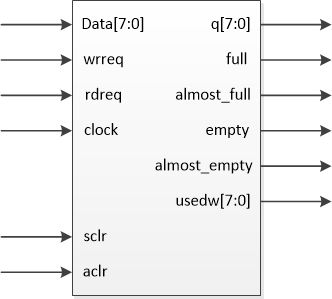

data為寫入的數據,此處為8位。然后wrreq為請求寫操作,rdreq為請求讀操作,clock為時鐘信號。q為輸出端,8位數據的輸出端。full為滿標志,當fifo緩沖器存儲數據溢滿時,full端將輸出高電平。almost_full為接近滿標志信號,當存儲的數據即將要滿時,almost_full端將輸出高電平以阻止寫操作繼續向fifo中寫數據造成數據溢出。empty則為空標志位,當fifo中數據全部讀取完后,empty端便會輸出高電平用來標記,almost_empty便是在fifo即將要空時便會發出高電平,以阻止fifo的讀操作繼續從fifo中讀取數據。usedw為fifo中的字數,sclr為異步清零端口。

02 IP核使用

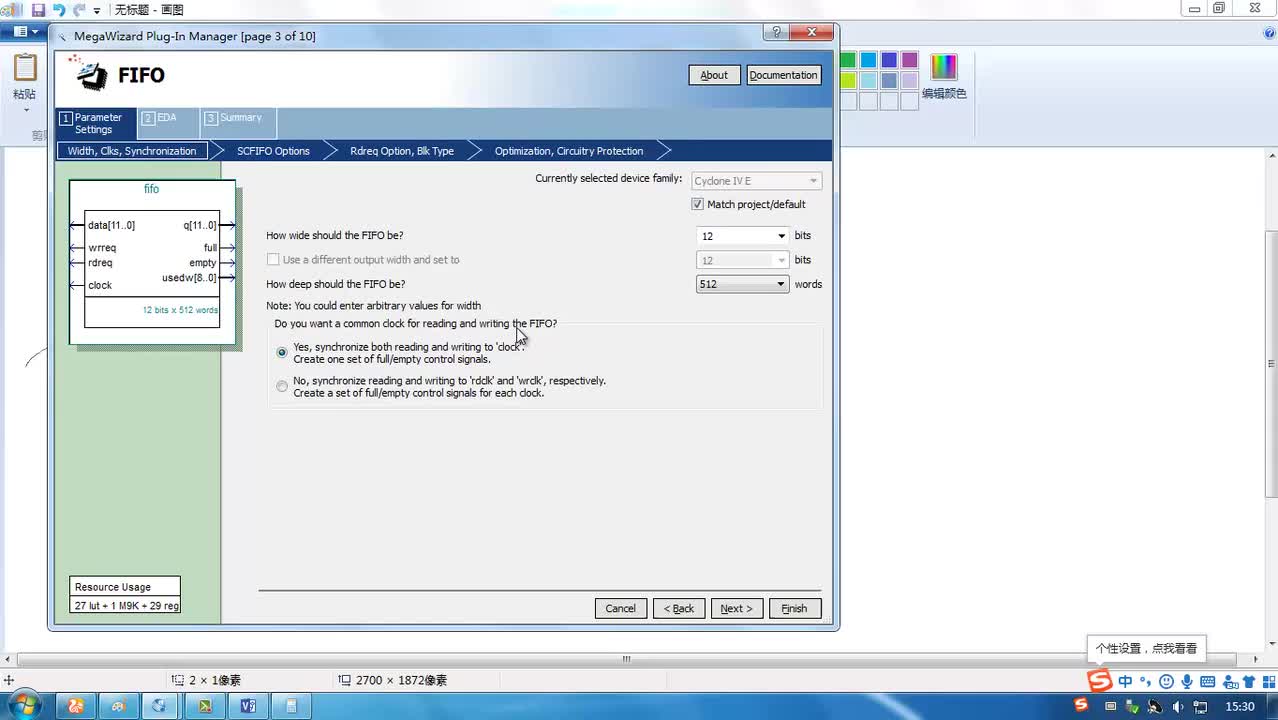

首先創建一個FIFO的工程保持在prj下,并在prj下新建一個ip的文件夾。點擊Tools -> MegaWizard Plug-In Manager。

選擇創建一個新的,然后如下圖,在左邊搜索框輸入FIFO,然后選擇第一項,選擇后在右邊的路徑中輸入地址ip并以fifo.v保持。

接下來如下圖,首先設置數據的位寬及深度,此處設置數據位寬為8位,數據深度為256words(及多少個數據)。

然后接下來設置需要的端口,根據01中的結構圖,這里需要選擇full滿、empty空、以及接近滿almost_full、接近空almost_empty和異步清零端sclr。在接近滿與接近空處需要設置閾值,即到達多少時接近滿端口開始輸出標志信號,這里設置數據寫操作達到254words時接近滿標志開始標記,數據讀操作在usedw為2時接近空端口開始標記。

下圖便是讀操作請求確認信號的兩種模式,一個是普通模式一個是前顯模式。

選擇器件優化方式是面積優先還是速度優先,更換可以看到資源占用率是不一樣的,選擇速度優先必然使用資源會上升。

然后便一直next后finish創建完成。

這時轉回界面便可看到生成ip的fifo.v文件,然后便開始書寫激勵仿真文件。

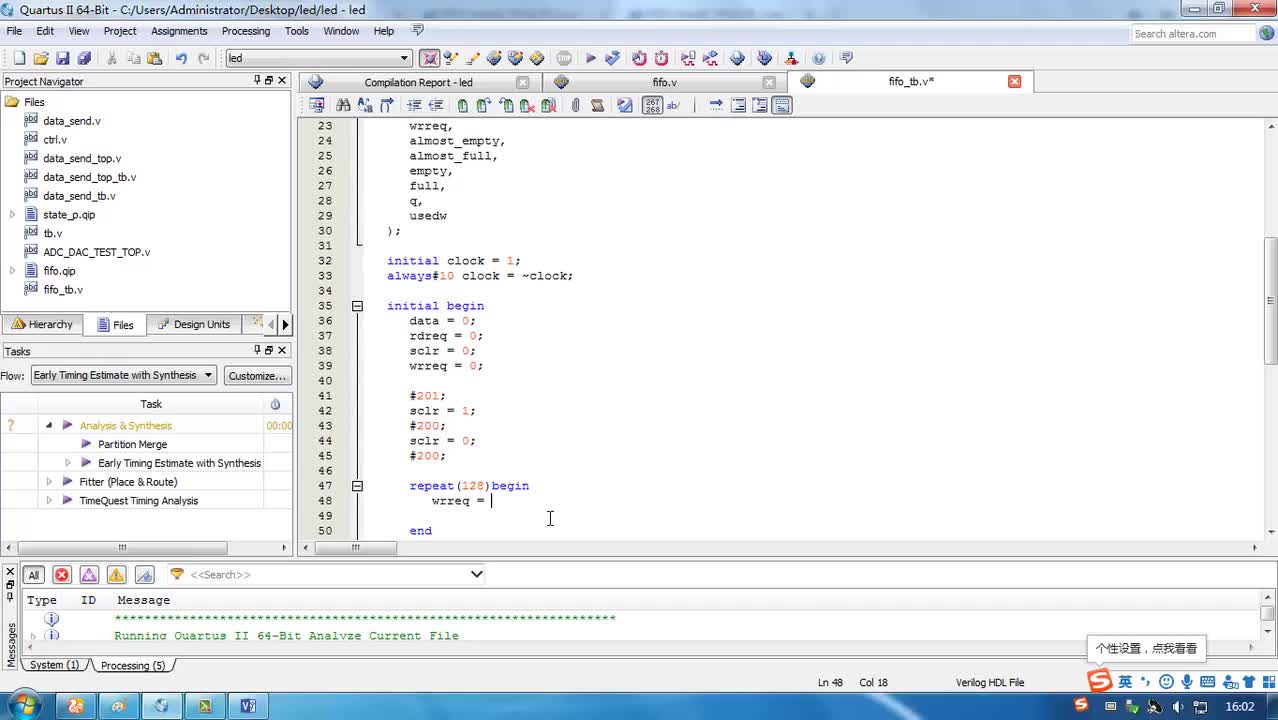

首先還是例化需要仿真的文件,然后仿真時鐘并在仿真文件中與例化程序進行連線。

接下來便是定義常量i,寫一個for循環,i自加寫請求wrreq置1將i的值寫入數據data中,usedw中數據深度開始依次增多,等256個words寫完之后,寫請求關閉,然后開始讀操作,同樣的i從零自加到255,然后將讀請求置1開啟,系統便開始從輸出端q中依次輸出data中的數據,同時usedw中的數據深度也開始一次減少。

接下來看仿真波形圖:

此處是綜合仿真圖,前半部分是寫操作的波形圖,后半部分便是讀操作的波形圖。

上圖這部分為寫操作,圖中可以看到i每個周期自加1,i的值便賦給數據data,然后usedw便是統計此時data中的數據多少即深度,在usedw為2時可以看到almost_empty接近空出現一個下降沿,在data中開始寫入數據時,寫請求wrreq產生高電平。

此處可以看出,在深度usedw自加至254時,接近滿端almost_full便會產生上升沿用來標記,計滿后full端產生上升沿,寫操作結束。

上圖為讀操作,這里隨著i的自加輸出端q開始依次輸出data中的數據,然后usedw隨著data中的數據被讀取便開始自減。

后面可以看出,當深度usedw為2時,接近空端almost_empty產生上升沿,清空后empty也產生上升沿,讀操作結束。

-

傳感器

+關注

關注

2562文章

52504瀏覽量

763282 -

fifo

+關注

關注

3文章

400瀏覽量

44595 -

時鐘

+關注

關注

11文章

1878瀏覽量

132807 -

uart

+關注

關注

22文章

1264瀏覽量

103177 -

IP核

+關注

關注

4文章

338瀏覽量

50427

發布評論請先 登錄

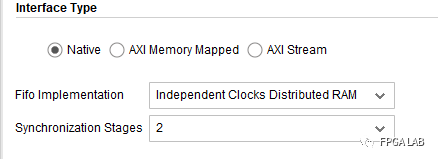

【鋯石A4 FPGA試用體驗】IP核之FIFO(一)創建與配置

XILINX FIFO IP核調用問題

【正點原子FPGA連載】第十三章IP核之FIFO實驗-領航者ZYNQ之FPGA開發指南

FIFO IP核的使用

基于MicroBlaze的AXI總線實時時鐘IP核設計

AXI STREAM FIFO如何設置雙時鐘

講解幾點關于FIFO IP核使用時的注意事項

XILINX FPGA IP之FIFO Generator例化仿真

使用IP核創建單時鐘FIFO

使用IP核創建單時鐘FIFO

評論