文本轉自公眾號系列文章,歡迎關注

《基于“礦板”低成本學習Zynq系列》之四-第一個工程HelloWorld一下 (qq.com)

一.前言

礦板,可能一些器件都不穩定了,比如DDR,所以我們來測試下,做個壓力測試。

這一篇先測試DDR,后面再測試其他的。

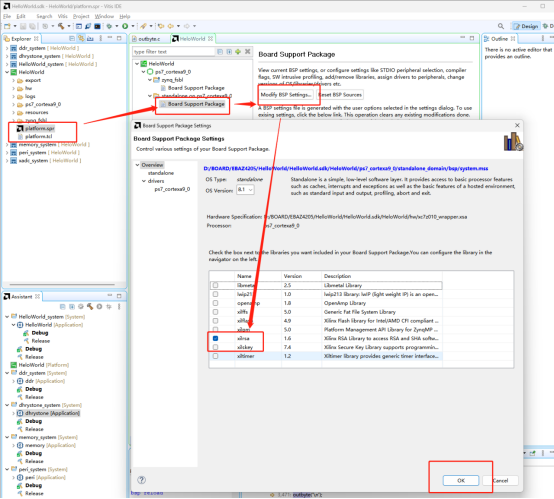

Vitis打開之前的HelloWorld工程

參考https://mp.weixin.qq.com/s/eecigPSyHQGUIx8hwSoAtQ

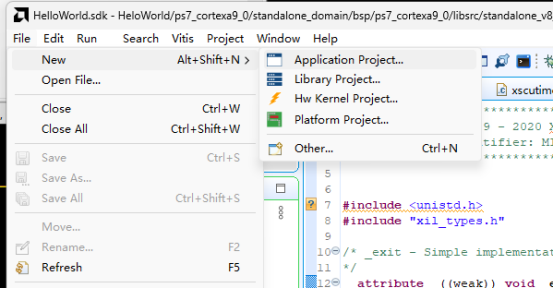

二.創建工程

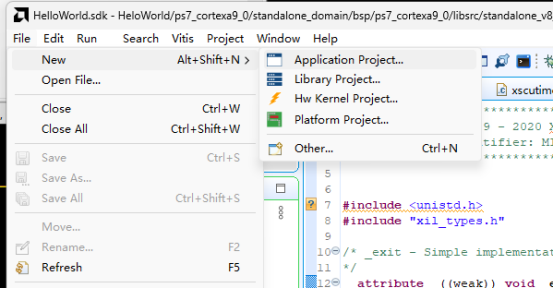

File->New->Application Project...

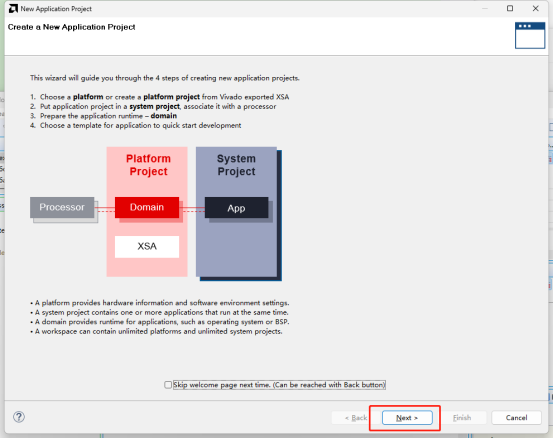

Next

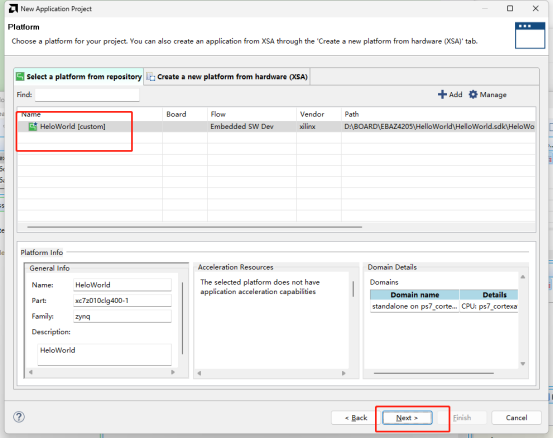

選擇之前創建的平臺,Next

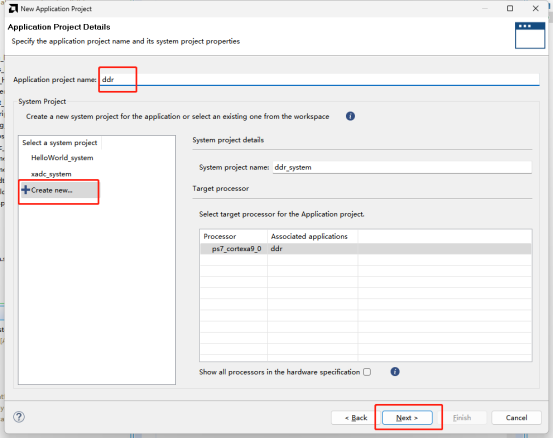

輸入工程名ddr,next

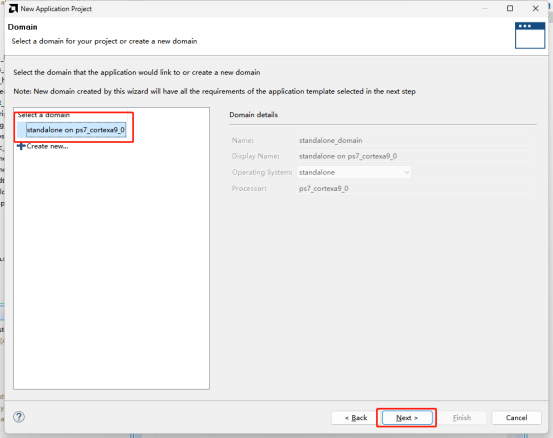

Next

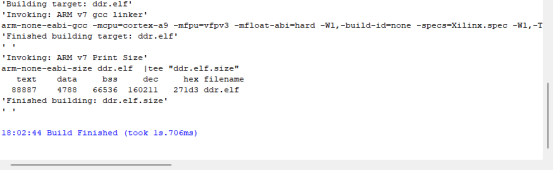

三.編譯

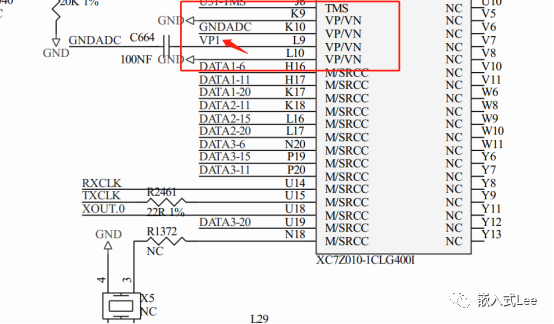

從原理圖可以看出

DDR 256M 16位

EM6GD16EWKG-12H

所以

int bus_width = 32;

改為

int bus_width = 16;

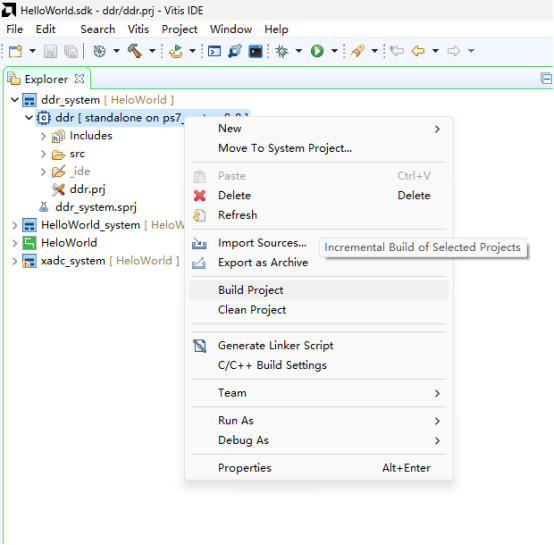

右鍵點擊DDR工程,build project

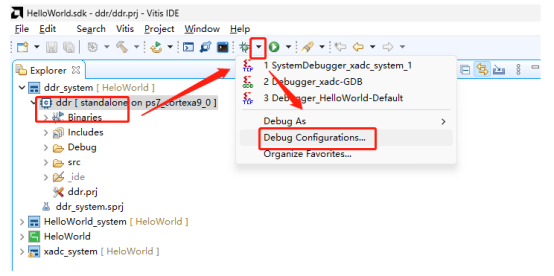

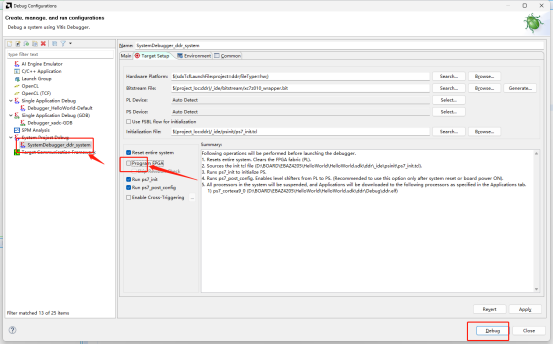

四.仿真運行

五.測試

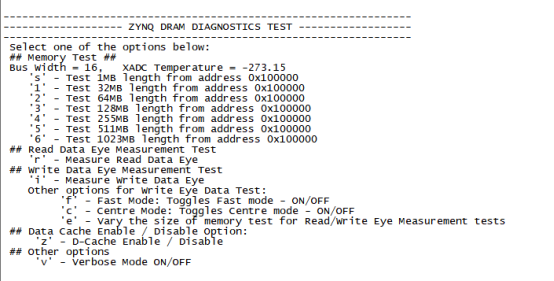

運行后打印如下

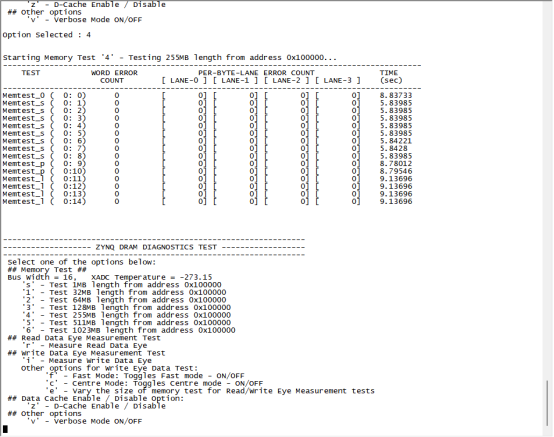

輸入4測試255M的大小

r測試讀眼圖

i測試寫眼圖

六.總結

以上測試,確認DDR目前看還比較可靠,沒有問題。

-

測試

+關注

關注

8文章

5632瀏覽量

128314 -

DDR

+關注

關注

11文章

731瀏覽量

66385 -

眼圖

+關注

關注

1文章

70瀏覽量

21341 -

編譯

+關注

關注

0文章

676瀏覽量

33748 -

Zynq

+關注

關注

10文章

614瀏覽量

48025

發布評論請先 登錄

請問4層板能實現zynq+ddr3嗎?

使用Vitis 在EBAZ4205(ZYNQ)礦機上實現"Hello World!"

如何調試Zynq UltraScale+ MPSoC VCU DDR控制器

低成本 MiniZed Zynq SoC 開發板

DDR PHY 與電路板調試

如何調試 Zynq UltraScale+ MPSoC VCU DDR 控制器?

《基于“礦板”低成本學習Zynq系列》之六-DDR測試

《基于“礦板”低成本學習Zynq系列》之六-DDR測試

評論