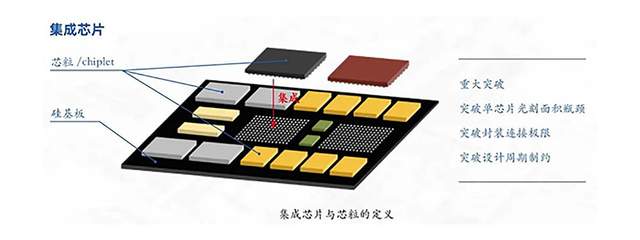

? 在過去的五年里,處理器已經(jīng)從單個硅片變成了一組較小的小芯片,這些小芯片共同作用就像一個大芯片一樣。這種方法意味著 CPU 的功能部件可以使用最適合每個部件的技術(shù)來構(gòu)建。AMD的產(chǎn)品技術(shù)架構(gòu)師Sam Naffziger是這種方法的早期支持者。Naffziger 最近回答了IEEE Spectrum就該主題提出的五個小芯片大小的問題。

問:您認(rèn)為基于小芯片的處理器面臨哪些主要挑戰(zhàn)?

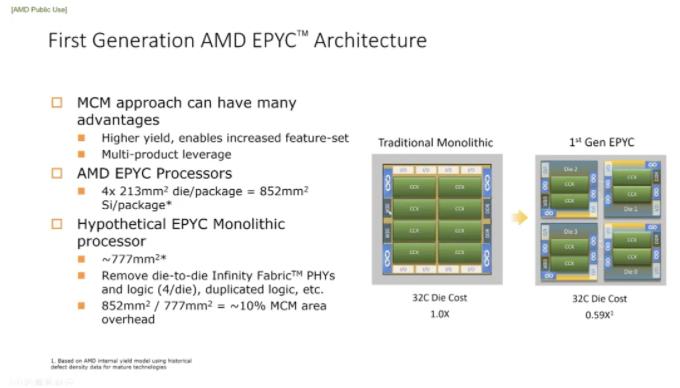

Sam Naffziger:我們五六年前開始推出EPYC和Ryzen CPU 系列。當(dāng)時,我們?nèi)隽艘粡埾喈?dāng)廣泛的網(wǎng)來尋找最適合連接芯片(小硅塊)的封裝技術(shù)。這是一個由成本、性能、帶寬密度、功耗以及制造能力組成的復(fù)雜方程式。提出出色的封裝技術(shù)相對容易,但實際大批量、經(jīng)濟(jì)高效地制造它們卻是完全不同的事情。所以我們在這方面投入了大量資金。

問:小芯片將如何改變半導(dǎo)體制造工藝?

Naffziger:這絕對是該行業(yè)正在努力解決的問題。這就是我們今天所處的位置,也是我們 5 到 10 年后可能達(dá)到的位置。我認(rèn)為今天的技術(shù)基本上都是通用的。它們可以很好地與單片芯片對齊,也可以用于小芯片。有了小芯片,我們就擁有了更專業(yè)的知識產(chǎn)權(quán)。因此,未來人們可以設(shè)想專業(yè)化的工藝技術(shù)并獲得性能優(yōu)勢、成本降低等。但這并不是當(dāng)今行業(yè)的現(xiàn)狀。

問:小芯片將如何影響軟件?

Naffziger:我們架構(gòu)的目標(biāo)之一是讓它對軟件完全透明,因為軟件很難改變。例如,我們的第二代 EPYC CPU 由被計算芯片包圍的集中式 I/O [輸入/輸出] 小芯片組成。當(dāng)我們采用集中式 I/O 芯片時,它減少了內(nèi)存延遲,消除了第一代的軟件挑戰(zhàn)。

現(xiàn)在,借助 [ AMD Instinct] MI300(AMD 即將推出的高性能計算加速器),我們正在集成 CPU 和 GPU 計算芯片。這種集成的軟件含義是它們可以共享一個內(nèi)存地址空間。因為軟件不必?fù)?dān)心管理內(nèi)存,所以編程更容易。

問:有多少架構(gòu)可以分離到小芯片上?

Naffziger:我們正在尋找擴(kuò)展邏輯的方法,但 SRAM 更具挑戰(zhàn)性,而模擬的東西絕對無法擴(kuò)展。我們已經(jīng)采取了將模擬與中央 I/O 小芯片分離的步驟。借助3D V-Cache(一種與計算芯片 3D 集成的高密度緩存小芯片),我們分離出了 SRAM。我預(yù)計未來會有更多此類專業(yè)化。物理學(xué)將決定我們可以做到多細(xì)粒度,但我對此持樂觀態(tài)度。

問:怎樣才能將不同公司的小芯片混合并匹配到同一個封裝中才能成為現(xiàn)實?

Naffziger:首先,我們需要一個關(guān)于接口的行業(yè)標(biāo)準(zhǔn)。UCIe是 2022 年推出的小芯片互連標(biāo)準(zhǔn),是重要的第一步。我認(rèn)為我們將看到這種模式的逐步發(fā)展,因為它對于提供更高水平的每瓦性能和每美元性能至關(guān)重要。然后,您將能夠組裝一個針對特定市場或客戶的片上系統(tǒng)。

-

處理器

+關(guān)注

關(guān)注

68文章

19890瀏覽量

235126 -

amd

+關(guān)注

關(guān)注

25文章

5586瀏覽量

136332 -

chiplet

+關(guān)注

關(guān)注

6文章

459瀏覽量

12994

原文標(biāo)題:關(guān)于Chiplet,AMD的5個經(jīng)驗分享

文章出處:【微信號:AI_Architect,微信公眾號:智能計算芯世界】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

基于AMD Versal器件實現(xiàn)PCIe5 DMA功能

Chiplet與先進(jìn)封裝設(shè)計中EDA工具面臨的挑戰(zhàn)

淺談Chiplet與先進(jìn)封裝

Chiplet技術(shù)在消費電子領(lǐng)域的應(yīng)用前景

Chiplet:芯片良率與可靠性的新保障!

2.5D集成電路的Chiplet布局設(shè)計

解鎖Chiplet潛力:封裝技術(shù)是關(guān)鍵

發(fā)現(xiàn)基于Zen 5架構(gòu)的AMD Threadripper “Shimada Peak” 96核和16核CPU

Chiplet技術(shù)有哪些優(yōu)勢

2035年Chiplet市場規(guī)模將超4110億美元

IMEC組建汽車Chiplet聯(lián)盟

AMD Versal自適應(yīng)SoC CPM5 QDMA的Tandem PCIe啟動流程介紹

國產(chǎn)半導(dǎo)體新希望:Chiplet技術(shù)助力“彎道超車”!

突破與解耦:Chiplet技術(shù)讓AMD實現(xiàn)高性能計算與服務(wù)器領(lǐng)域復(fù)興

關(guān)于Chiplet,AMD的5個經(jīng)驗分享

關(guān)于Chiplet,AMD的5個經(jīng)驗分享

評論