問題描述:

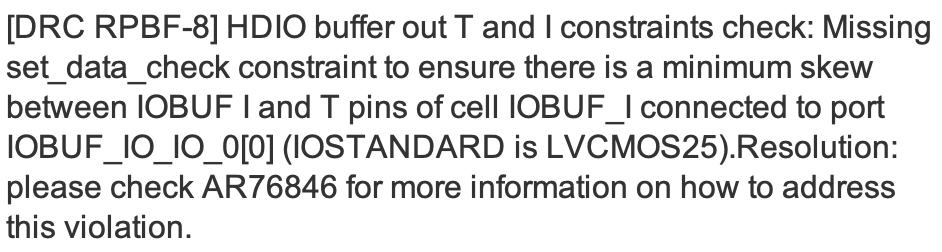

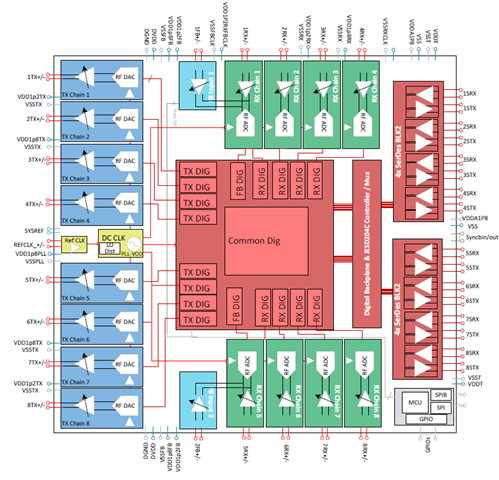

本文著重探討 HDIO OBUFT 和 IOBUF 用例。如果含三態(tài)控制 (OBUFT/IOBUF) 的 HDIO 輸出緩沖器的上電電壓為 3.3 V 或 2.5 V 并且 Data(數(shù)據(jù))控制信號與 Tristate(三態(tài))控制信號的切換時(shí)間彼此相近,則可能會(huì)受到三態(tài)數(shù)據(jù)爭用條件的影響。

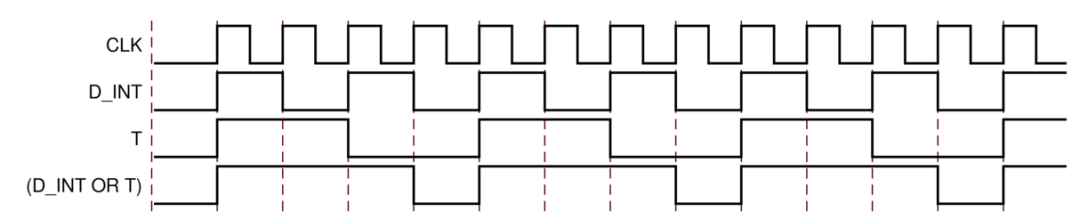

僅當(dāng)三態(tài)和數(shù)據(jù)開關(guān)彼此相反(例如,三態(tài) 0 -> 1 且數(shù)據(jù) 1 -> 0)時(shí),此爭用條件才會(huì)導(dǎo)致問題。當(dāng)三態(tài)和數(shù)據(jù)開關(guān)同向(例如,三態(tài) 0 -> 1 且數(shù)據(jù) 0 -> 1)時(shí),則不會(huì)導(dǎo)致問題。

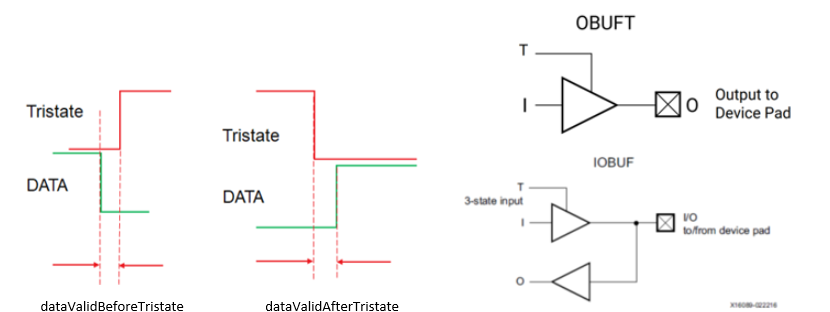

生成的輸出可能會(huì)驅(qū)動(dòng)錯(cuò)誤的焊盤電壓。焊盤可能保持在此錯(cuò)誤電壓下,直至三態(tài)(dataValidBeforeTristate 場景)或數(shù)據(jù)(dataValidAfterTrisate 場景)再次切換為止。

^dataValidBeforeTristate = 550 ps

dataValidAfterTristate = 200 ps^

受影響的器件:除 VSVD1760 外的其他封裝中的 VC1902、VC1802、VM1802、VM1402 和 VM1302。

僅限含 HD bank 的器件才會(huì)受到 HDIO IOBUF 和 OBUFT 用例的影響。VSVD1760 封裝不含 HDIO bank,因此不受影響。

受影響的 IP 核:

雖然 IP 通常并不強(qiáng)制使用 HDIO,但以下 IP 核使用 HDIO 緩沖器的方式很可能使其受此問題影響。此處隨附的 Tcl 腳本可用于幫助調(diào)整諸多場景下的數(shù)據(jù)到三態(tài)布線關(guān)系:

AXI 1G 以太網(wǎng)

AXI QSGMII

三模以太網(wǎng) MAC

AXI QSPI

解決方法:

要解決該問題,請確保在有問題的窗口(dataValidBeforeTristate = 0.550ps 和 dataValidAfterTristate = 0.200ps)中,數(shù)據(jù)和三態(tài)不執(zhí)行切換。

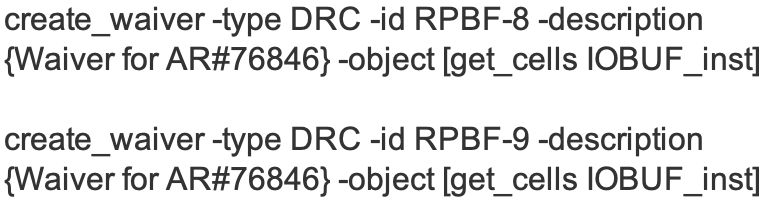

在 Vivado 2021.2 和更高版本中,DRC 將向用戶標(biāo)記此問題:

下列方法可用于確保在有問題的窗口中,數(shù)據(jù)和三態(tài)不執(zhí)行切換:

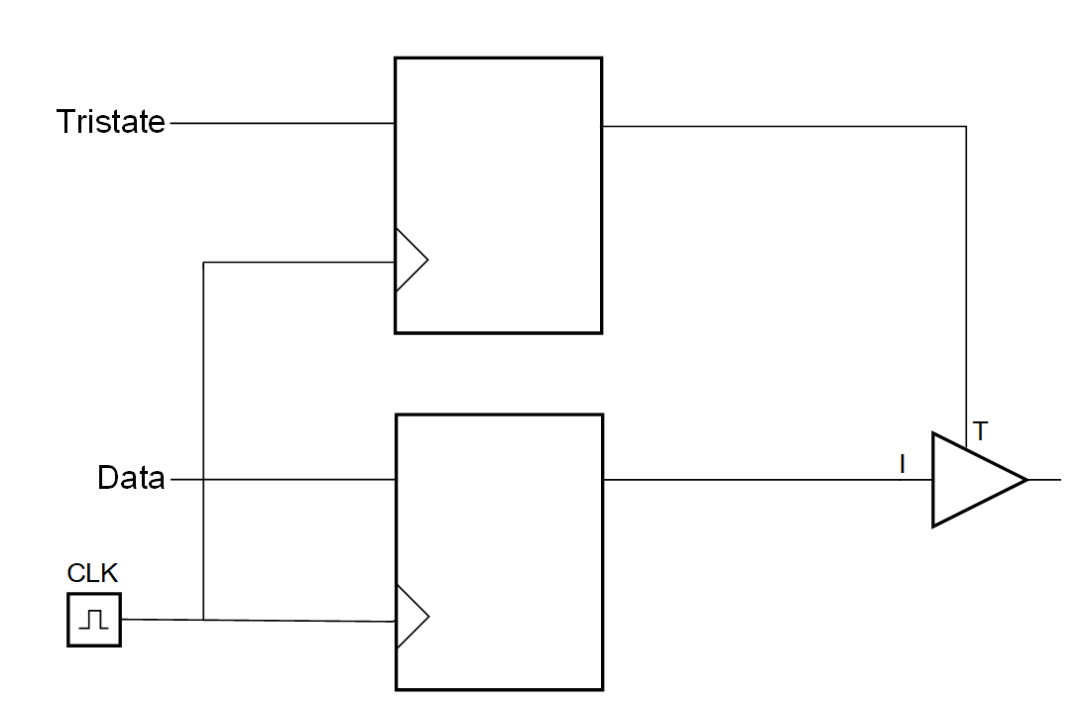

通過設(shè)計(jì)系統(tǒng)將三態(tài)和數(shù)據(jù)切換偏移一個(gè)周期。

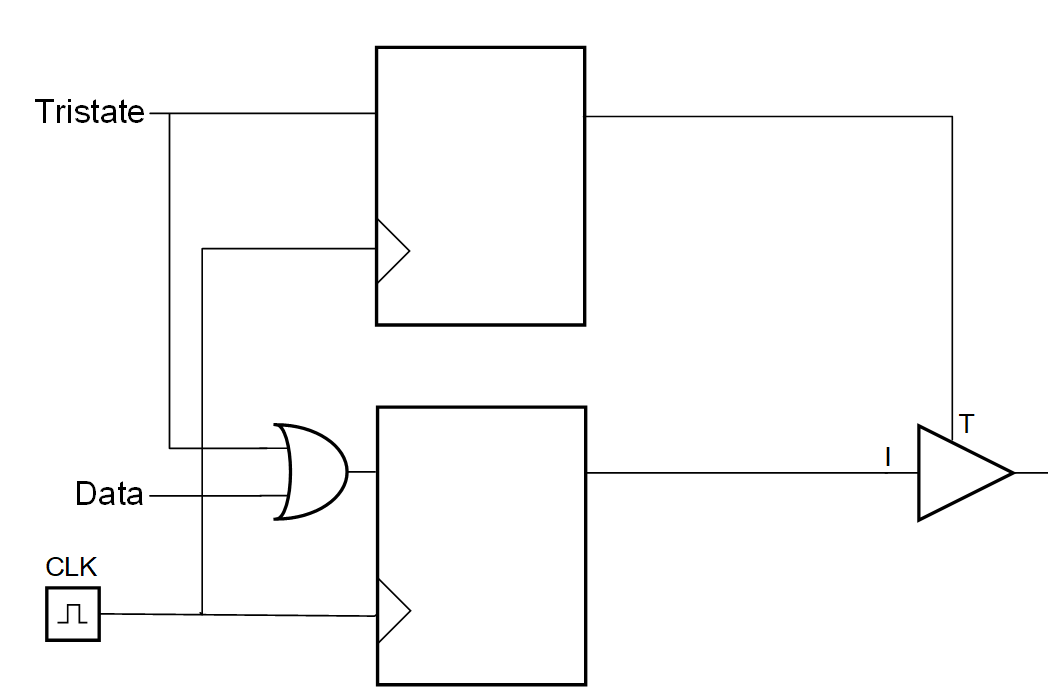

寄存的數(shù)據(jù)和三態(tài)信號可以在 IOL Flop 的 I 輸入中利用數(shù)據(jù)和三態(tài)的邏輯 OR 來避免此問題。

將

替換為

時(shí)序圖示例:

通過 Tcl 腳本使用 set_data_check 約束來確保數(shù)據(jù)和三態(tài)信號線的偏差足以確保數(shù)據(jù)和三態(tài)都能避免出現(xiàn)爭用條件。

注釋:僅當(dāng)數(shù)據(jù)和三態(tài)都發(fā)生切換時(shí),才會(huì)發(fā)生此問題。在 Data 管腳上,Open Drain(開漏)接口保持常量“0”,因此常用 2.5 V 接口和 3.3 V 接口(如 I2C)將不受影響。

僅當(dāng)數(shù)據(jù)或三態(tài)已綁定時(shí),才能通過以下命令豁免 DRC。

對于 Vivado 2022.1 和更低版本,您可使用隨附的 fixHDIO.tcl 腳本來評估影響,并且可能通過布線來修復(fù)此問題。

此腳本將檢查 IOBUF 或 OBUFT 的設(shè)計(jì),并檢查三態(tài)與數(shù)據(jù)之間的延遲,確認(rèn)在有問題的窗口內(nèi)是否發(fā)生切換。

如果發(fā)生了切換,此腳本將通過 set_data_check 置位來取消這些信號線的布線,重新布線,并報(bào)告結(jié)果。

要運(yùn)行該腳本,請打開已實(shí)現(xiàn)的設(shè)計(jì)或 DCP。

在 Tcl 控制臺(tái)中,使用 source 命令找到該腳本:

source -quiet fixHDIO.tcl

找到 Tcl 腳本后,可運(yùn)行多個(gè)過程來分析設(shè)計(jì):

getHDIOTristateBuffers - 列出以 2.5 V 或 3.3 V 上電的 HDIO bank 中含三態(tài)控制的所有緩沖器,這些緩沖器可能會(huì)受到三態(tài)/數(shù)據(jù)爭用問題的影響。

reportHDIOTristateBuffers - 報(bào)告以 2.5 V 或 3.3 V 上電的 HDIO bank 中含三態(tài)控制的所有緩沖器(可能受三態(tài)/數(shù)據(jù)爭用問題影響),并描述用于報(bào)告這些緩沖器的原因的機(jī)制。

validateHDIOTristateBuffers - 該命令將分析設(shè)計(jì),查看是否有足夠的時(shí)序裕度能在尚未運(yùn)行 fixHDIOTristateBuffers 時(shí)就避免出現(xiàn)爭用條件。如果發(fā)生違例,則必須運(yùn)行 fixHDIOTristateBuffers 來解決問題。

waiveHDIOTristateBuffers- 該命令應(yīng)僅用于為下列已寄存的緩沖器豁免 DRC 違例:此類緩沖器在三態(tài)/數(shù)據(jù)管腳之間實(shí)現(xiàn) OR 門控,或者已知不受影響(即,在設(shè)計(jì)中,數(shù)據(jù)和三態(tài)控制已偏移)。運(yùn)行 fixHDIOTristateBuffers 后,應(yīng)自動(dòng)禁止顯示這些緩沖器的 DRC 違例。 僅限在已知不存在問題的緩沖器上運(yùn)行該過程。 fixHDIOTristate 緩沖器將通過更改時(shí)序來解決此問題,應(yīng)將其用于有問題場景的所有緩沖器。

fixHDIOTristateBuffers- 為沒有足夠數(shù)據(jù)和三態(tài)偏差的緩沖器的數(shù)據(jù)和三態(tài)信號線執(zhí)行重新布線。此命令不修復(fù)在三態(tài)/數(shù)據(jù)管腳之間需要 OR 門控的已寄存的緩沖器。此過程結(jié)束時(shí)會(huì)報(bào)告時(shí)序關(guān)系。此過程結(jié)束時(shí),應(yīng)在 Tcl 中運(yùn)行“report_route_status”以驗(yàn)證腳本確實(shí)能夠成功完成信號線的重新布線。 如不執(zhí)行此操作,可能導(dǎo)致該腳本誤報(bào)所有時(shí)序路徑都已滿足。

timeHDIOTristateBuffers- 報(bào)告數(shù)據(jù)與三態(tài)管腳之間的時(shí)序關(guān)系。應(yīng)在 fixHDIOTristateBuffers 插入必要的時(shí)序約束后運(yùn)行此命令。如果該工具能夠找到布線解決方案,那么應(yīng)僅存在正時(shí)序裕量。

分析結(jié)果:

fixHDIOTristateBuffers 和 timeHDIOTrisateBuffers 將報(bào)告所提供的緩沖器上的時(shí)序。裕量值為正表示腳本已成功完成 Data (I) 和 Tristate 控制 (T) 的重新布線。

在此場景下為了正確定時(shí),將對數(shù)據(jù)或三態(tài)給予 1000 ns 的要求。預(yù)計(jì)將有一條信號線存在較大的偏差要求。 只要信號線均為正,就不會(huì)發(fā)生 HDIO 三態(tài)沖突。

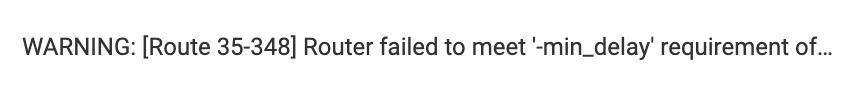

出現(xiàn)如下消息表示,如果 Tcl 腳本無法通過新的布線解決該問題,那么布線器就無法以充足的偏差完成設(shè)計(jì)的重新布線。

注釋:在此場景中,如果報(bào)告的裕量為正值,那么即使出現(xiàn)該警告也沒問題。

該腳本將標(biāo)記 IOB 觸發(fā)器對數(shù)據(jù)和三態(tài)進(jìn)行寄存的情況,但不會(huì)嘗試解決。

這些管腳需實(shí)現(xiàn)與上述邏輯等效的電路更改,并對驅(qū)動(dòng) IOB 數(shù)據(jù)寄存器的輸入管腳的數(shù)據(jù)和三態(tài)信號線執(zhí)行 OR 邏輯。

如果 Tcl 腳本以避免出現(xiàn)該問題的方式成功完成數(shù)據(jù)和三態(tài)管腳的重新布線,則將需要修改設(shè)計(jì)。圍繞此問題常見的修改包括:

寄存數(shù)據(jù)和三態(tài)控制信號,對數(shù)據(jù)控制和三態(tài)控制執(zhí)行 OR 邏輯,如上所述。

調(diào)整設(shè)計(jì),使三態(tài)和數(shù)據(jù)斷言偏移一個(gè)周期。

如果出現(xiàn)該腳本無法解決此問題的罕見情況,請?jiān)u估選項(xiàng) 1“將三態(tài)和數(shù)據(jù)切換偏移一個(gè)周期”和選項(xiàng) 2“對數(shù)據(jù)和三態(tài)執(zhí)行邏輯 OR”,并對設(shè)計(jì)執(zhí)行必要的更改。

審核編輯:劉清

-

以太網(wǎng)

+關(guān)注

關(guān)注

40文章

5582瀏覽量

174778 -

寄存器

+關(guān)注

關(guān)注

31文章

5421瀏覽量

123315 -

緩沖器

+關(guān)注

關(guān)注

6文章

2037瀏覽量

46586 -

DCP

+關(guān)注

關(guān)注

0文章

30瀏覽量

17496 -

QSPI接口

+關(guān)注

關(guān)注

0文章

14瀏覽量

3513

原文標(biāo)題:FPGA:HDIO OBUFT 和 IOBUF 三態(tài)時(shí)序影響

文章出處:【微信號:Hack電子,微信公眾號:Hack電子】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

HDIO OBUFT和IOBUF用例簡析

HDIO OBUFT和IOBUF用例簡析

評論