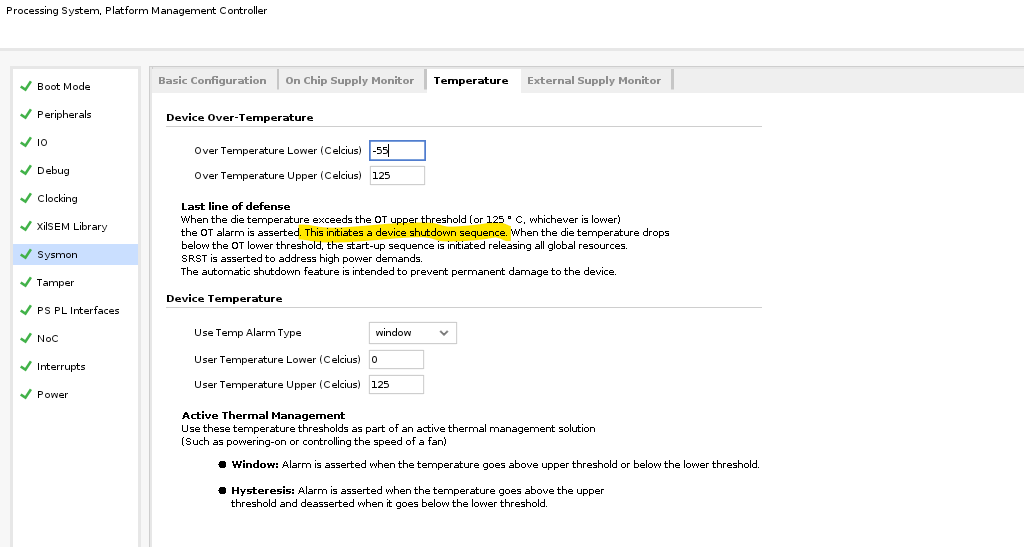

在 CIPS GUI 中已對(duì) Versal System Monitor 過熱 (OT) 告警進(jìn)行了說明。其中聲明當(dāng)“OT Alarm”(過熱告警)斷言有效時(shí),將啟動(dòng)器件關(guān)閉:

但在 Vivado 2021.1.2 及更低的版本中,當(dāng) OT 斷言有效時(shí),Vivado 并不會(huì)自動(dòng)實(shí)現(xiàn)錯(cuò)誤響應(yīng)。

解決方法:

此問題在 Vivado 2021.2 中已得到修復(fù),OT 告警默認(rèn)將通過“Error Management”(錯(cuò)誤管理)發(fā)出 SRST。您也可使用以下 Tcl 命令通過 CIPS 設(shè)置錯(cuò)誤響應(yīng):

set_property CONFIG.PS_PMC_CONFIG {OT_EAM_RESP } $cips

值和對(duì)應(yīng)行為:

0x01-POR

0x02-SRST(默認(rèn))

0x04-ERROUT

0x07-NONE

在低于 Vivado 2021.2 的版本中,您可對(duì)此問題采用如下變通方法,即更新 pmc_data.cdo 文件來手動(dòng)更改錯(cuò)誤響應(yīng)。

1) 在 gen_files 文件夾內(nèi)找到 pmc_data.cdo 文件。

2) 添加以下指令:

em_set_action 0x28104000 0x2 0x8000 #This command is for SysMon OT occurs will issue the srst.

3) 使用以下 Bootgen 命令重新生成 PDI:

bootgen -arch versal -image design_1_wrapper.bif -w -o design.pdi

-

Xilinx

+關(guān)注

關(guān)注

73文章

2182瀏覽量

124331 -

GUI

+關(guān)注

關(guān)注

3文章

676瀏覽量

40738 -

Versal

+關(guān)注

關(guān)注

1文章

167瀏覽量

8005

發(fā)布評(píng)論請(qǐng)先 登錄

【ZYNQ Ultrascale+ MPSOC FPGA教程】第二十七章System Monitor

【ALINX 技術(shù)分享】AMD Versal AI Edge 自適應(yīng)計(jì)算加速平臺(tái)之 Versal 介紹(2)

Placer無法創(chuàng)建RPM怎么辦

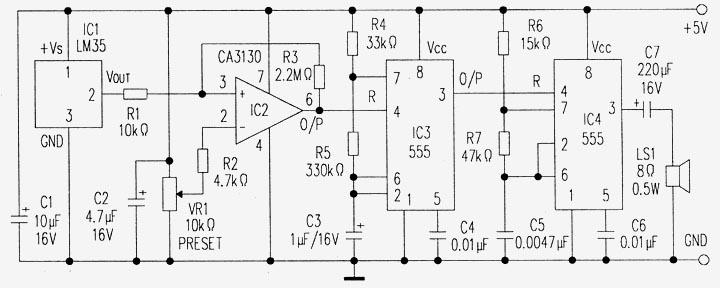

電腦過熱告警器制作資料分享

USB Monitor Control Class Spec

基于入侵行為模式的告警關(guān)聯(lián)

Design of Crimp force Monitor

DS2770,pdf (Battery Monitor an

CCTV MOnitor與PC Monitor的差異及區(qū)別

電腦過熱告警器電路圖

了解系統(tǒng)監(jiān)控儀System Monitor的各種功能

System Monitor配置和構(gòu)建設(shè)計(jì)

Versal Premium SysMon:如何在輔助SLR中對(duì)SysMon寄存器進(jìn)行尋址

MAX20481: Four- to Seven-Input Automotive Power-System Monitor Family Data Sheet MAX20481: Four- to Seven-Input Automotive Power-System Moni

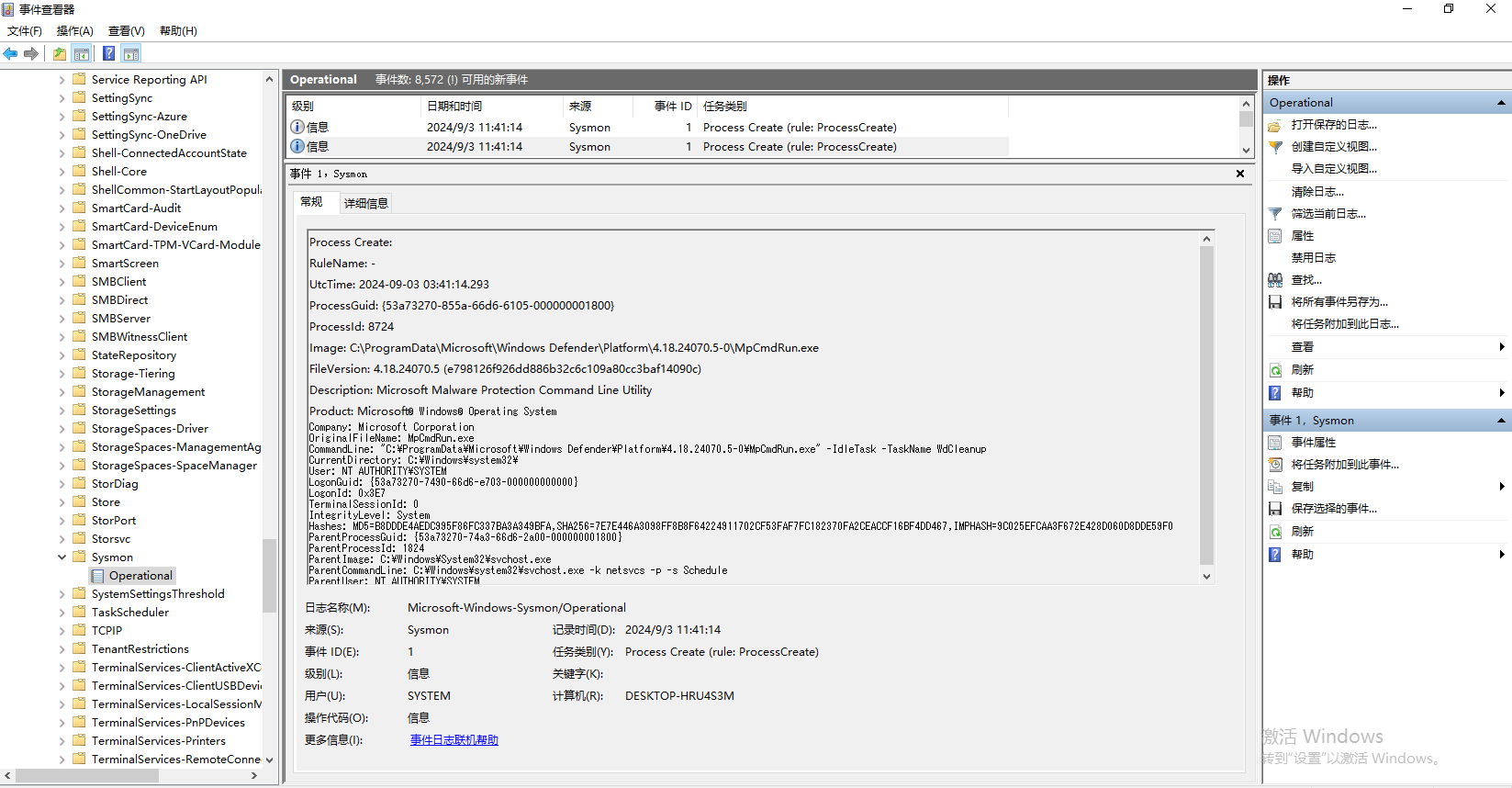

藍(lán)隊(duì)技術(shù)——Sysmon識(shí)別檢測(cè)宏病毒

Versal System Monitor(Sysmon):過熱告警行為

Versal System Monitor(Sysmon):過熱告警行為

評(píng)論