在農(nóng)業(yè)生產(chǎn)領(lǐng)域,無(wú)人機(jī)視覺(jué)追蹤系統(tǒng)運(yùn)用在識(shí)別農(nóng)作物的生長(zhǎng)情況中,進(jìn)行高空灌溉、驅(qū)趕害蟲等自動(dòng)化農(nóng)業(yè)管理;在民用領(lǐng)域,無(wú)人機(jī)通常使用視覺(jué)跟蹤系統(tǒng)識(shí)別人體手勢(shì),讓用戶通過(guò)手勢(shì)操控?zé)o人機(jī)的升降和擺動(dòng);在生物調(diào)研領(lǐng)域,該技術(shù)更多是為了追蹤記錄野生瀕危動(dòng)物的生活習(xí)慣,維護(hù)生態(tài)系統(tǒng)平衡。

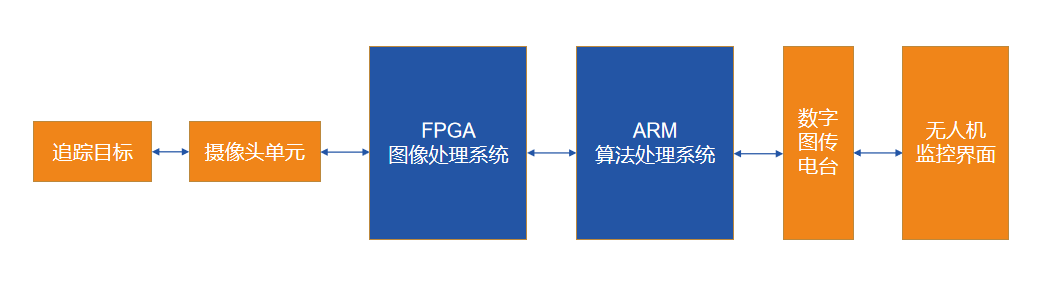

無(wú)人機(jī)跟蹤系統(tǒng)是如何組成的呢?首先,無(wú)人機(jī)通過(guò)高清攝像頭模塊,實(shí)時(shí)采集圖像數(shù)據(jù),系統(tǒng)通過(guò)信號(hào)檢測(cè)模塊和圖像預(yù)處理模塊將圖片信息轉(zhuǎn)變成數(shù)字信息,然后通過(guò)數(shù)據(jù)采集與處理模塊進(jìn)行采樣、量化,并對(duì)各圖片參數(shù)進(jìn)行分析過(guò)濾;將分析結(jié)果與設(shè)定的跟蹤目標(biāo)比較,進(jìn)行圖像識(shí)別跟蹤;跟蹤的圖像信息可以通過(guò)網(wǎng)絡(luò)傳輸?shù)?a target="_blank">手機(jī)和電腦實(shí)時(shí)顯示。

無(wú)人機(jī)視覺(jué)跟蹤流程圖

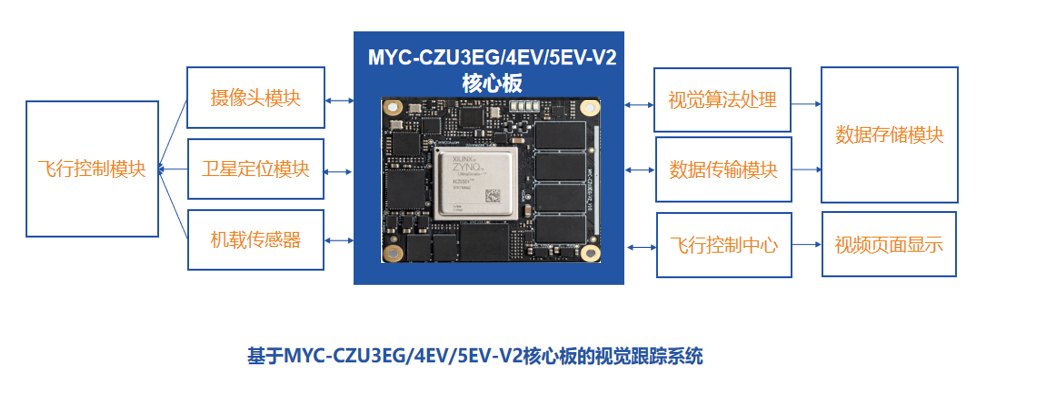

基于米爾電子MYC-CZU4EV/5EV-V2核心板設(shè)計(jì)的無(wú)人機(jī)視覺(jué)跟蹤系統(tǒng),可以分為圖像信號(hào)采集、數(shù)據(jù)處理、信息展示三部分;圖像采集主要通過(guò)攝像頭收集圖像信息,再由FPGA芯片高速采集將圖片信息傳輸?shù)綌?shù)據(jù)處理單元,數(shù)據(jù)處理單元由VCU和MCU組成,負(fù)責(zé)將采集的圖像數(shù)據(jù)通過(guò)算法把設(shè)定好的跟蹤目標(biāo)進(jìn)行標(biāo)注處理;而信息展示部分,則通過(guò)無(wú)線傳輸系統(tǒng)把信息同步顯示到無(wú)人機(jī)控制平臺(tái)和APP上面,實(shí)現(xiàn)實(shí)時(shí)視頻傳輸,掌握遠(yuǎn)程定位追蹤功能。

MYC-CZU3EG/4EV/5EV-V2核心板,搭載功能全面的高規(guī)格Zynq UltraScale+ MPSoC芯片,其中芯片的PS端集成了APU ARM Cortex?-A53處理器,RPU Cortex-R5處理器,頻率高達(dá)667MHz的Arm Mali-400 MP2(GPU)。需要注意的是,4EV/5EV芯片比3EG芯片多了一個(gè)視頻編解碼器單元 (VCU),支持H.264/H.265編解碼。芯片搭載內(nèi)部存儲(chǔ)器,外部存儲(chǔ)器接口(DDR)和外設(shè)接口。這些外設(shè)接口主要包括USB總線接口,以太網(wǎng)接口,SD/eMMC接口,I2C總線接口,CAN總線接口,UART接口,GPIO等。高速接口如 PCIE,SATA,Display Port。

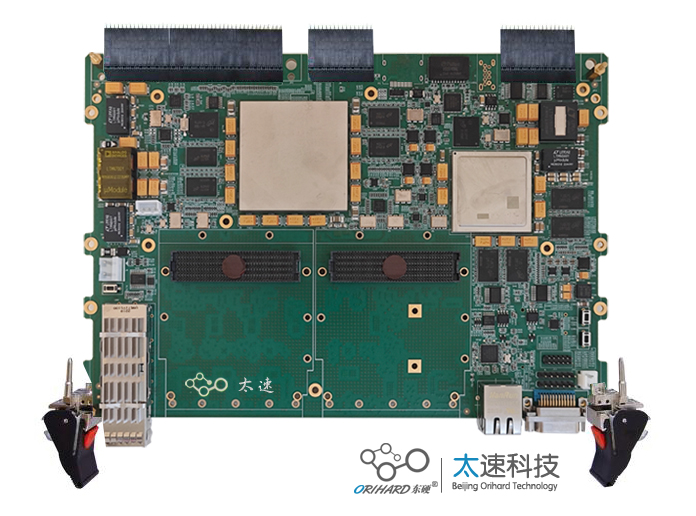

核心板圖片:

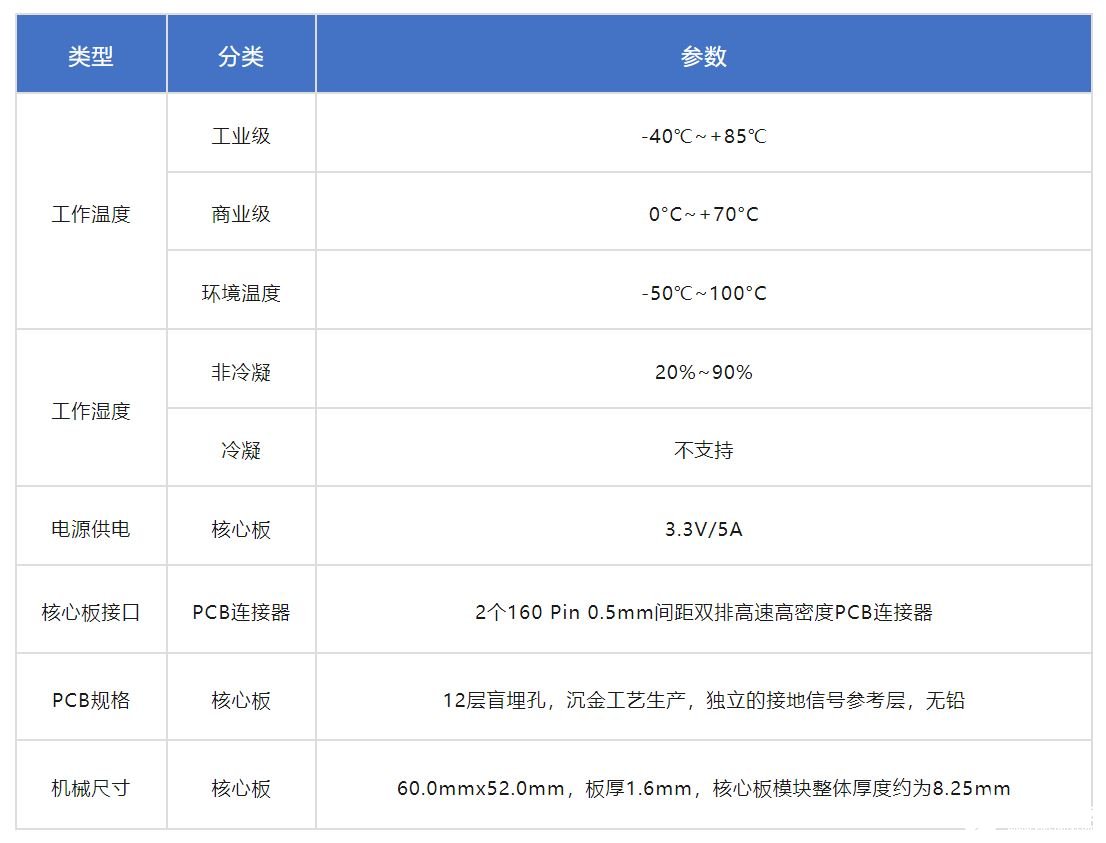

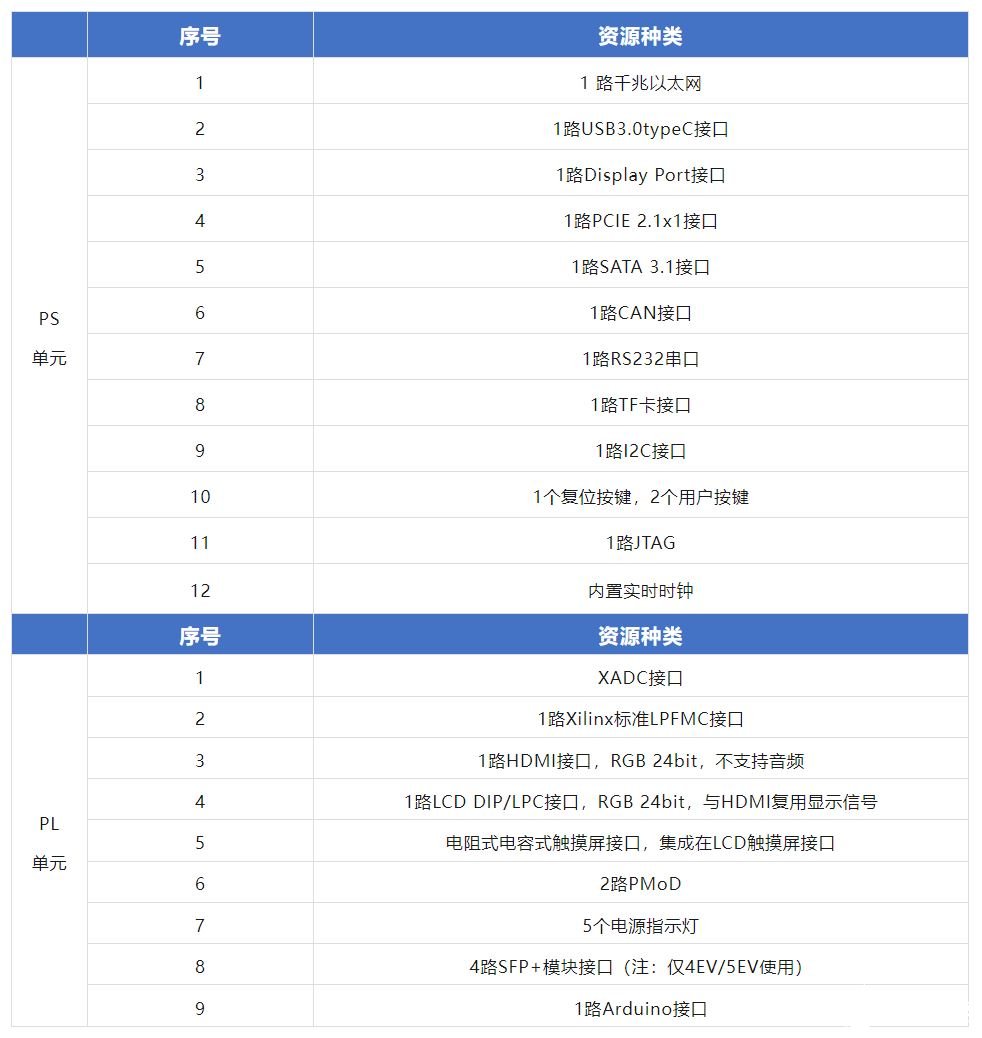

板卡資料:

機(jī)械參數(shù)

底板資源

本文轉(zhuǎn)載自:米爾MYiR微信公眾號(hào)

審核編輯:湯梓紅

-

攝像頭

+關(guān)注

關(guān)注

61文章

4948瀏覽量

97650 -

無(wú)人機(jī)

+關(guān)注

關(guān)注

230文章

10728瀏覽量

185525 -

跟蹤系統(tǒng)

+關(guān)注

關(guān)注

0文章

88瀏覽量

18870 -

核心板

+關(guān)注

關(guān)注

5文章

1105瀏覽量

30628

發(fā)布評(píng)論請(qǐng)先 登錄

XCZU15EG板卡設(shè)計(jì)原理圖:基于 XCZU15EG的雙 FMC通用信號(hào)處理板

請(qǐng)問(wèn)有XCZU9CG-FFVC900的原理圖庫(kù)嗎?

將pkg文件與ibis文件集成到XCZU3EGS-FVA625時(shí)出現(xiàn)問(wèn)題

米爾MYD-CZU3EG搭載Xilinx DPU,具備強(qiáng)大AI計(jì)算能力,你怎么看米爾這款產(chǎn)品?

XCZU15EG板卡學(xué)習(xí)資料第524篇:基于XCZU15EG的FMC+ 高性能通用信號(hào)處理板卡

XCZU4EG-L2FBVB900E系統(tǒng)SOC芯片

XCZU7EG-1FBVB900I系統(tǒng)SOC芯片

XCZU19EG-L2FFVD1760E系統(tǒng)SOC芯片

米爾發(fā)布新品Zynq UltraScale+ MPSoC核心板

MPSOC開發(fā)板教程之HELLO WORLD

XCZU3EG開發(fā)筆記之gpio_emio?

無(wú)人機(jī)視覺(jué)跟蹤系統(tǒng)解決方案-米爾基于XCZU3EG/XCZU4EV/XCZU5EV核心板

XCZU15EG設(shè)計(jì)原理圖:523(ZCU102E的pin兼容替代卡) 基于 XCZU15EG的雙 FMC通用信號(hào)處理板

基于6U VPX XCVU9P+XCZU7EV的雙FMC信號(hào)處理板卡

高速圖像處理卡設(shè)計(jì)原理圖:527-基于3U VPX XCZU15EG+TMS320C6678的信號(hào)處理板

基于XCZU3EG/XCZU4EV/XCZU5EV核心板的無(wú)人機(jī)視覺(jué)跟蹤系統(tǒng)解決方案

基于XCZU3EG/XCZU4EV/XCZU5EV核心板的無(wú)人機(jī)視覺(jué)跟蹤系統(tǒng)解決方案

評(píng)論