功能ECO與時(shí)序ECO的關(guān)系

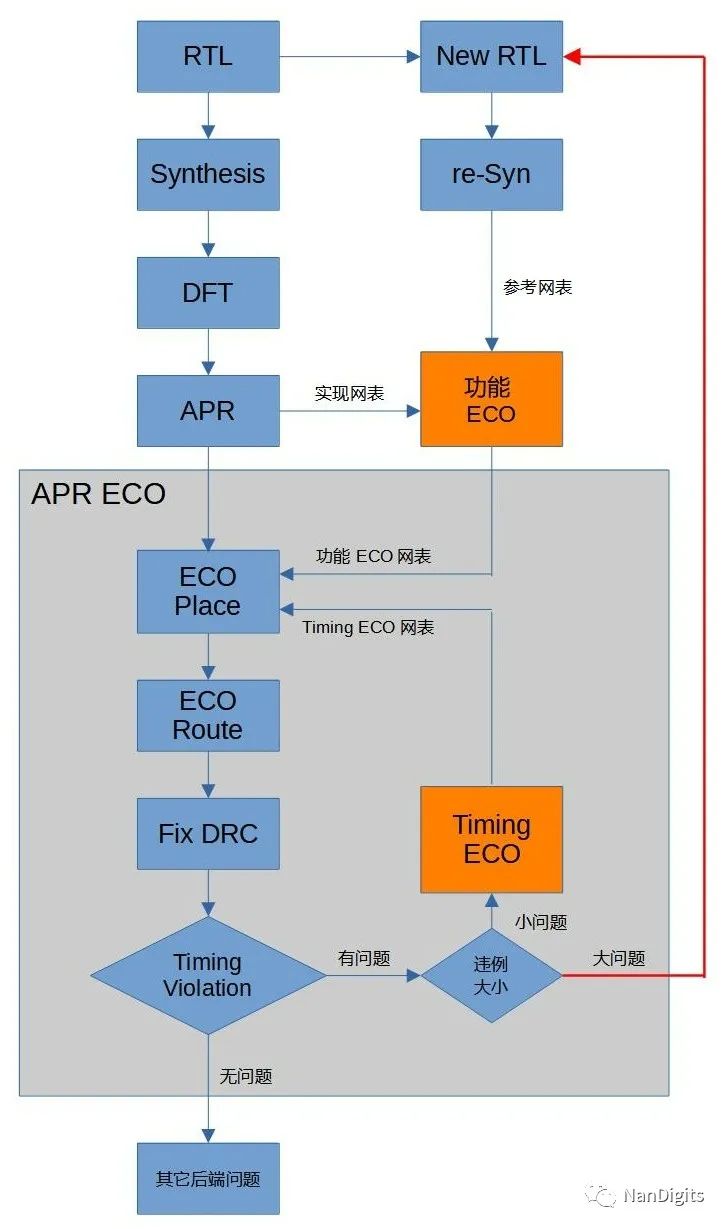

功能ECO主要指當(dāng)RTL更新后對(duì)后端APR網(wǎng)表做的功能方面的改動(dòng)。功能ECO可以由手工或者自動(dòng)化工具完成,得到ECO網(wǎng)表。再由后端布局布線工具(如ICC2、Innovus)讀入ECO網(wǎng)表,進(jìn)行ECO Place和ECO Route。

時(shí)序ECO主要指為了解決后端ECO Route時(shí)的setup和hold時(shí)序違例,可以用后端工具指令、外部工具(本廠或者第三方)、人工替換Cell、優(yōu)化DRC等方法完成。

從上圖可以看出,功能ECO主要是由前端工程師做,時(shí)序ECO主要是由后端工程師做。前端工程師做完一版功能ECO后,需要對(duì)ECO網(wǎng)表進(jìn)行LEC檢查,確認(rèn)ECO網(wǎng)表與新RTL等價(jià),之后再把驗(yàn)證無誤的ECO網(wǎng)表交給后端工程師。

后端工程師拿到ECO網(wǎng)表后,到ICC2/Innovus里做后端實(shí)現(xiàn),并解決DRC、時(shí)序等問題。在PostMask ECO時(shí),ECO網(wǎng)表的很小的改動(dòng)都可以可能引起DRC和時(shí)序的違例,原因可能是:Cell太遠(yuǎn)、連線太長、驅(qū)動(dòng)能力不夠、繞線擁擠等。遇到時(shí)序問題,首先是利用后端工具來優(yōu)化。小時(shí)序問題可以手工或者用Timing ECO工具優(yōu)化過去,大時(shí)序問題就需要前端工程師進(jìn)行返工。

前端工程師返工時(shí),有哪些辦法呢?一是,挑選距離近的sparecell;二是,盡量復(fù)用現(xiàn)有stdcell,減少改動(dòng)的連線的根數(shù);三是,從RTL層面簡化修改方案,能不新加DFF就不加,能復(fù)用現(xiàn)成的信號(hào)就復(fù)用現(xiàn)成的信號(hào)。四是,與項(xiàng)目經(jīng)理、產(chǎn)品經(jīng)理、市場部一起對(duì)BUG進(jìn)行排序,優(yōu)先解決影響客戶使用的BUG,軟件繞不過去的BUG,放棄一些次要的BUG。

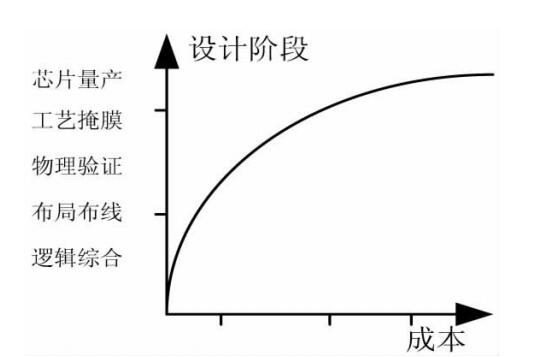

所以功能ECO常常需要迭代好幾次,才能得到一個(gè)折中的結(jié)果。當(dāng)然如果必須要解決的BUG太多,或者后端無法實(shí)現(xiàn),那么就只能走Full layer Tapeout,但芯片交付客戶也會(huì)多晚幾個(gè)月。現(xiàn)在芯片市場競爭異常激烈,你的產(chǎn)品不行,別人頂上,客戶可能就沒了。

NanDigits GOF ECO的方案

我們一直在思考如何才能減少功能ECO的迭代次數(shù),讓前端工程師在做功能ECO時(shí)就能夠提早看到時(shí)序的影響,并在功能ECO的同時(shí)就解決掉時(shí)序問題。我們嘗試、實(shí)踐、并成功開發(fā)出多個(gè)方案。

第一,是前端邏輯層面,自研了LEC(邏輯等價(jià)性)算法,利用這個(gè)算法能夠精準(zhǔn)找到新RTL與老APR網(wǎng)表的差異,這會(huì)大大縮小ECO的范圍。

第二,原創(chuàng)了RTL Patch ECO,在APR網(wǎng)表里寫RTL,這種方法可以找到更精準(zhǔn)的修改點(diǎn),彌補(bǔ)了算法在少數(shù)案例中表現(xiàn)不佳的情況。

第三,自研了在APR網(wǎng)表中查找RTL等價(jià)net的功能。由于綜合優(yōu)化、后端優(yōu)化,人工在網(wǎng)表中查找rtl等價(jià)net是非常麻煩的事情。點(diǎn)一下按鈕或者一個(gè)命令,GOF ECO就會(huì)通過分析網(wǎng)表、兩根net做LEC等方式找到等價(jià)net。這對(duì)手工ECO網(wǎng)表、網(wǎng)表不等價(jià)debug等提供了便利。

第四,GOF ECO支持讀入DEF/LEF,從中得到每個(gè)cell的物理信息。在spare cell映射時(shí)考慮這些cell位置信息,挑選出修改點(diǎn)附近更合適的spare cell。當(dāng)附近沒有某個(gè)cell時(shí),會(huì)做等價(jià)變換,用附近的其它c(diǎn)ell代替。

第五,GOF ECO實(shí)現(xiàn)了spare cell類型的約束,前端工程師可以根據(jù)當(dāng)前spare cell的類型和數(shù)量,來指導(dǎo)工具實(shí)現(xiàn)更優(yōu)化的方案。

第六,最新發(fā)布的GOF ECO實(shí)現(xiàn)了類似PT的report_timing的功能,這樣前端工程師在功能ECO的同時(shí)就可以評(píng)估時(shí)序,不需要等后端同事迭代,就能夠提前知道當(dāng)前功能ECO結(jié)果在后端實(shí)現(xiàn)的難度和風(fēng)險(xiǎn)。也可以同時(shí)評(píng)估多個(gè)ECO方案,擇優(yōu)提供給后端。另外,前端工程師還可以利用GOF API來提前解決一部分時(shí)序問題,不需要全部丟給后端。不但減輕了后端的壓力,還減少了ECO迭代次數(shù),縮短了ECO時(shí)間,加速了芯片交付客戶的進(jìn)度。

審核編輯:劉清

-

RTL

+關(guān)注

關(guān)注

1文章

389瀏覽量

61109 -

DRC

+關(guān)注

關(guān)注

2文章

155瀏覽量

37121 -

ECO

+關(guān)注

關(guān)注

0文章

52瀏覽量

15188 -

apr

+關(guān)注

關(guān)注

0文章

11瀏覽量

6610

原文標(biāo)題:時(shí)序(Timing)對(duì)功能ECO有多重要

文章出處:【微信號(hào):處芯積律,微信公眾號(hào):處芯積律】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

ENOB是什么? ENOB對(duì)于選擇示波器有多重要?

內(nèi)存時(shí)序究竟有多重要呢?究竟該如何去選擇內(nèi)存條呢?

嵌入式架構(gòu)有多重要?

單片機(jī)中的系統(tǒng)時(shí)鐘有多重要?

嵌入式架構(gòu)有多重要

單片機(jī)中的系統(tǒng)時(shí)鐘有多重要?

【時(shí)序約束資料包】培訓(xùn)課程Timing VIVADO

AppleID是什么 蘋果官方科普有多重要

ECO技術(shù)在SoC芯片設(shè)計(jì)中的應(yīng)用

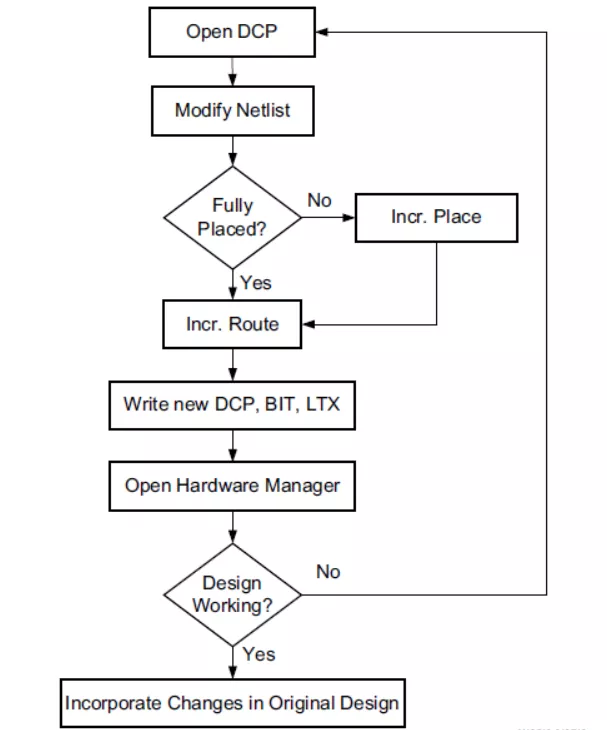

詳解Xilinx FPGA的ECO功能

什么是時(shí)序路徑timing path呢?

時(shí)序分析基本概念介紹—Timing Arc

時(shí)序(Timing)對(duì)功能ECO有多重要

時(shí)序(Timing)對(duì)功能ECO有多重要

評(píng)論