今天我們要介紹的時(shí)序分析概念是 時(shí)序路徑 (Timing Path)。STA軟件是基于timing path來(lái)分析timing的。那什么是timing path呢?

Timing Path根據(jù)起點(diǎn)和終點(diǎn)可以分為以下四種:

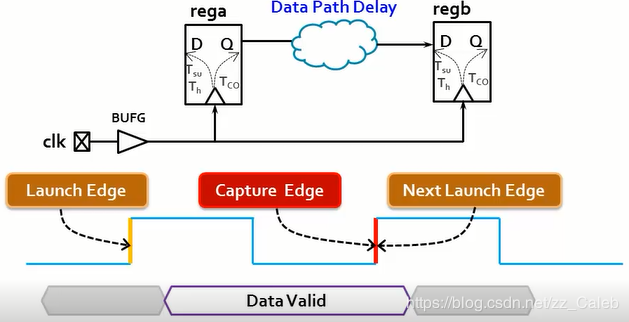

- 由Flip-Flop時(shí)鐘輸入端到Flip-Flop數(shù)據(jù)輸入端,即**reg2reg **path,如下圖1

- 由主要輸入到Flip-Flop數(shù)據(jù)輸入,即**in2reg **path,如下圖2

- 由Flip-Flop時(shí)鐘輸入端到主要輸出,即**reg2out **path,如下圖3

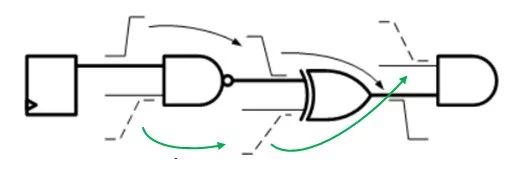

- 由主要輸入到主要輸出,即**in2out **path,如下圖4

圖1

圖2

圖3

圖4

-

時(shí)序分析

+關(guān)注

關(guān)注

2文章

127瀏覽量

22823 -

STA

+關(guān)注

關(guān)注

0文章

52瀏覽量

19227 -

時(shí)序分析器

+關(guān)注

關(guān)注

0文章

24瀏覽量

5340 -

時(shí)序路徑

+關(guān)注

關(guān)注

0文章

12瀏覽量

1443

發(fā)布評(píng)論請(qǐng)先 登錄

FPGA案例之時(shí)序路徑與時(shí)序模型解析

時(shí)序分析的基本概念及常規(guī)時(shí)序路徑的組成

FPGA時(shí)序約束之時(shí)序路徑和時(shí)序模型

【時(shí)序約束】關(guān)于設(shè)置FALSE PATH

Vivado下顯示指定路徑時(shí)序報(bào)告的流程

Timing Groups and OFFSET Const

Path-Specific Timing Constrain

基于FALSE PATH的設(shè)置

靜態(tài)時(shí)序分析基礎(chǔ)與應(yīng)用

如何判斷路徑的timing exception約束

AOCV時(shí)序分析概念介紹

時(shí)序分析基本概念介紹—Timing Arc

什么是時(shí)序路徑timing path呢?

什么是時(shí)序路徑timing path呢?

評(píng)論