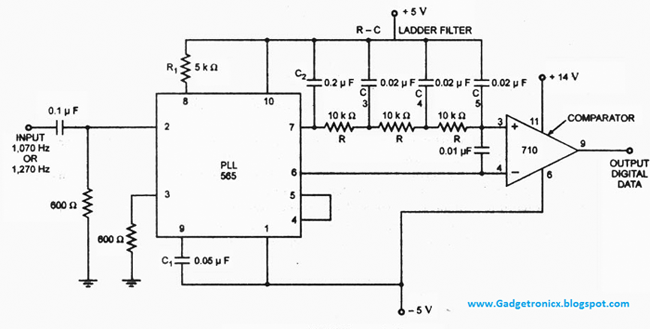

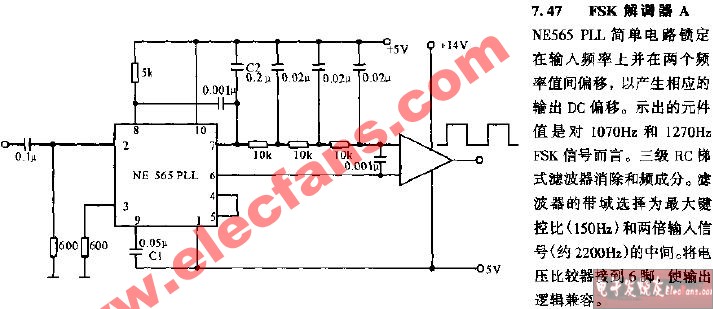

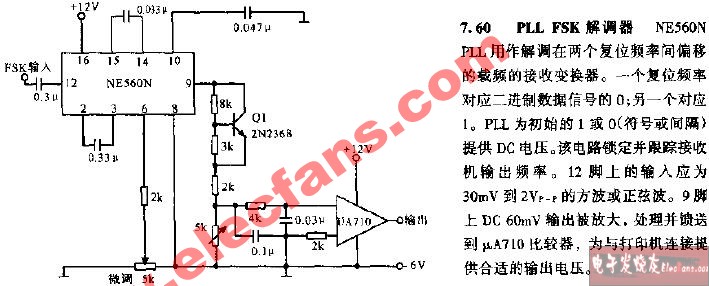

使用 PLL 565 電路的 FSK 解調器幫助我們以最少的組件輕松生成 FSK 信號。

在PLL

565中,頻移通常通過用接收到的二進制數(shù)據(jù)信號驅動壓控振蕩器來完成。因此,該解調器電路的輸出對應于輸入邏輯0或1信號。下面簡要討論了該電路的工作原理。

加工:

該PLL的工作方式是鎖定輸入信號頻率,并在兩個可能的頻率之間跟蹤該頻率,并在該IC的輸出端進行直流偏移。電阻R1和C1確定PLLIC內部VCO的自由運行頻率。您可以在下圖中看到各種引腳的功能。VCO比較器輸出被饋入相位比較器輸入,以執(zhí)行信號頻率的鎖定操作。

電路中使用了三級RC濾波器,用于從IC的輸出信號中去除總和頻率分量。選擇R1來調整VCO頻率以均衡引腳6和引腳7獲得的電壓。如果輸入頻率低,則數(shù)字化輸出將獲得高電壓電平,當輸入頻率為高電平時輸出將達到高電平(14

V)1070赫茲。如果輸入頻率為5,1 HZ,則輸出將被驅動至低狀態(tài)(-270V)。

-

解調器

+關注

關注

0文章

309瀏覽量

26362 -

FSK

+關注

關注

14文章

115瀏覽量

58942

發(fā)布評論請先 登錄

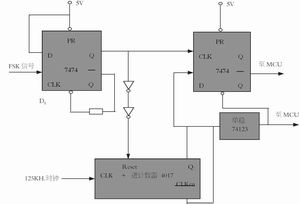

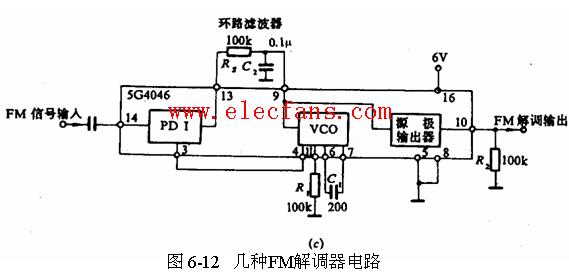

FSK信號的解調原理 自適應解調FSK原理

基于DSP的2FSK調制解調器的設計

基于73M223的FSK制式調制解調器電路設計

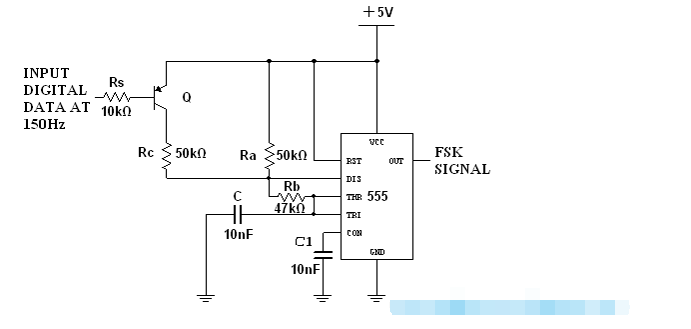

使用IC555和PLL565的無線調制解調器設計

使用PLL565電路的FSK解調器

使用PLL565電路的FSK解調器

評論