芯片異構集成的概念已經在推動封裝技術的創新。

混合鍵合支持各種可能的芯片架構,主要針對高端應用,包括高性能計算 (HPC)、人工智能 (AI)、服務器和數據中心。隨著技術的成熟,消費類應用、包括高帶寬存儲器 (HBM) 在內的存儲器件以及移動和汽車應用預計將進一步增長,這些應用可受益于高性能芯片間連接。

異構集成的背景故事

玩積木的樂趣之一就是可以用看似無限的方式將它們組合在一起。想象一下,將這一概念應用于半導體行業,您可以采用不同類型的芯片并將它們像塊一樣組合起來以構建獨特的東西。首先為半導體產品確定性能、尺寸、功耗和成本目標,然后通過將不同類型的芯片組合到單個封裝中來滿足要求。這種芯片異構集成的概念已經在推動封裝技術的創新。

最近,封裝中異構集成的采用不斷加速,以滿足對更復雜功能和更低功耗日益增長的需求。異構集成允許 IC 制造商在單個封裝中堆疊和集成更多硅器件。這可以包括來自不同晶圓、不同半導體技術和不同供應商的芯片的組合。異構集成還使小芯片集成能夠克服大型芯片的產量挑戰以及掩模版尺寸限制。

隨著 2.5D、3D 和扇出封裝技術的發展,銅微凸塊已在單個集成產品中提供了所需的垂直金屬器件到器件互連。銅微凸塊的間距通常為 40μm(凸塊尺寸為 25μm,間距為 15μm),現已縮小至 20μm 和 10μm 間距,以提高封裝密度和功能。然而,低于 10μm 的鍵合間距,微凸塊開始遇到產量和可靠性的挑戰。因此,雖然傳統的銅微凸塊將繼續使用,但新技術也正在開發中,以繼續提高互連密度。混合鍵合技術正在成為互連間距為 10μm 及以下的高端異構集成應用的可行途徑。

什么是混合鍵合?

混合鍵合是在異質或同質芯片之間創建永久鍵合的過程。“混合”是指在兩個表面之間形成電介質-電介質和金屬-金屬鍵。使用緊密嵌入電介質中的微小銅焊盤可提供比銅微凸塊多 1,000 倍的 I/O 連接,并將信號延遲驅動至接近零水平。其他優點包括擴展的帶寬、更高的內存密度以及更高的功率和速度效率。

混合鍵合技術

關鍵工藝步驟包括預鍵合層的準備和創建、鍵合工藝本身、鍵合后退火以及每個步驟的相關檢查和計量,以確保成功鍵合。

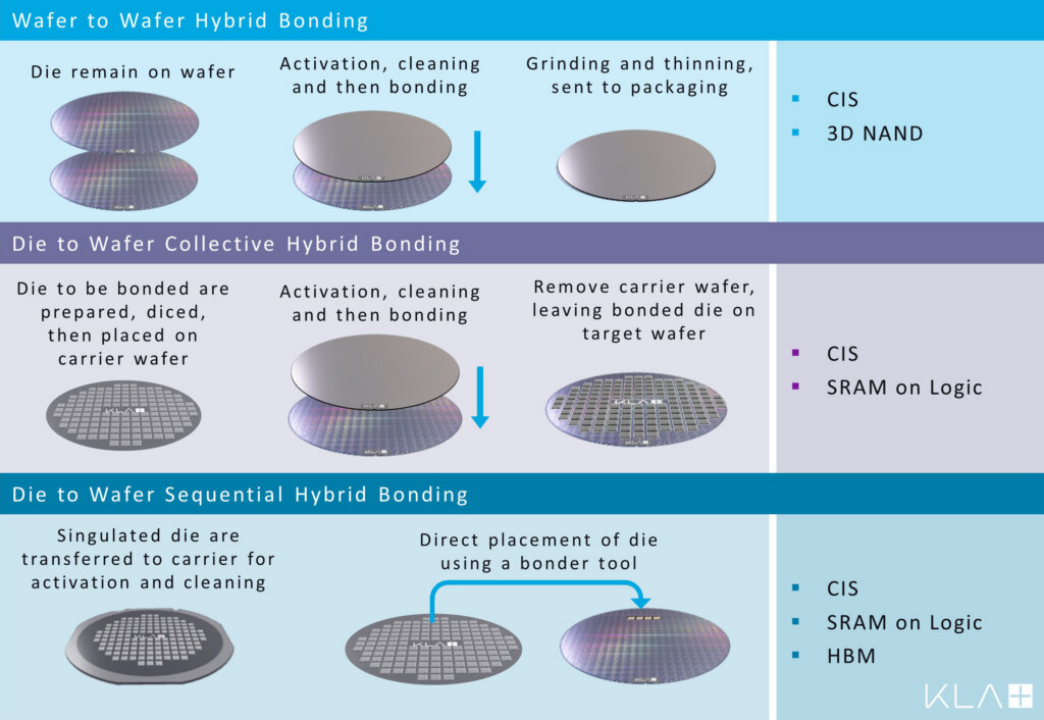

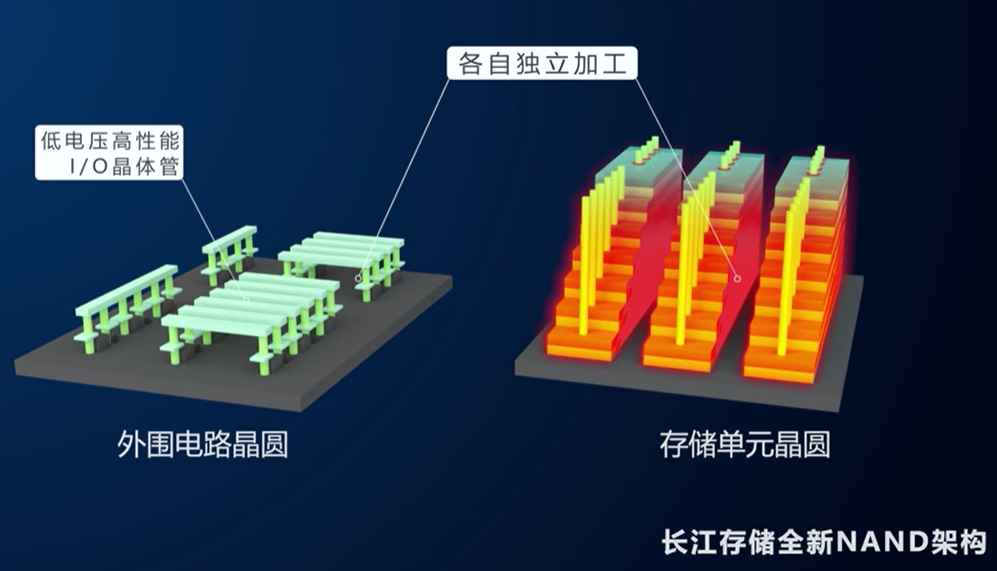

有兩種方法可以實現混合鍵合:晶圓到晶圓 (W2W) 和芯片到晶圓 (D2W) 。

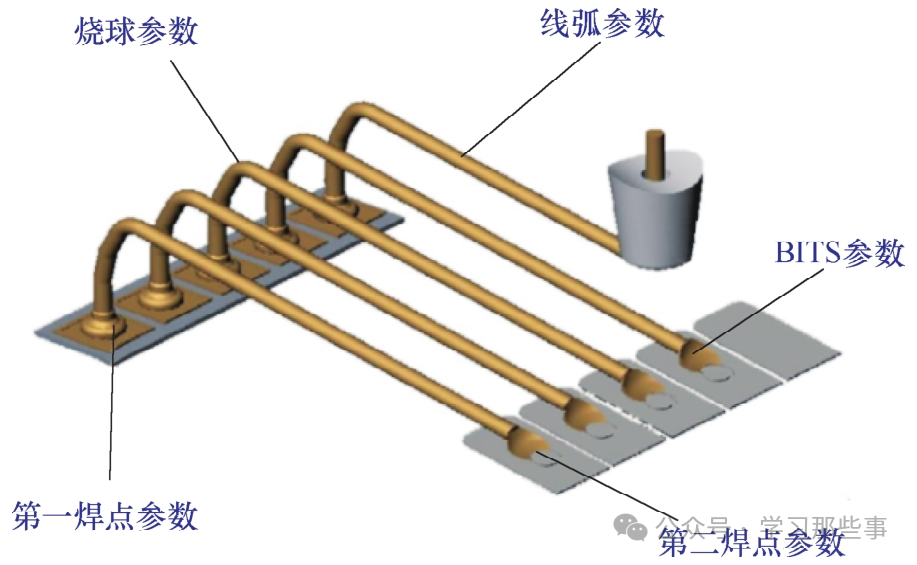

圖 2:W2W 和 D2W 混合鍵合技術和應用。

D2W 是異構集成中混合鍵合的主要選擇,因為它支持不同的芯片尺寸、不同的晶圓類型和已知的良好芯片,而所有這些對于 W2W 方案來說通常是不可能的。對于每種芯片,首先在半導體工廠中制造晶圓,然后利用混合鍵合工藝垂直堆疊芯片。

混合鍵合將封裝轉向“前端”

由于涉及先進的工藝要求和復雜性,混合鍵合發生在必須滿足污染控制、工廠自動化和工藝專業知識要求的環境中,而不是像許多其他封裝集成方法那樣在典型的封裝廠中進行。為了準備用于鍵合的晶圓,需要利用額外的前端半導體制造工藝在晶圓上創建最終層以連接芯片。這包括電介質沉積、圖案化、蝕刻、銅沉積和銅 CMP。半導體工廠擁有混合鍵合工藝所需的環境清潔度、工藝工具、工藝控制系統和工程專業知識。

需要已知良好的模具

使用 D2W 混合鍵合將多個芯片異構集成到一個封裝中,從而產生高性能、高價值的器件。當您考慮到包含一個壞芯片可能會導致整個封裝報廢時,風險就很高。為了保持高產量,需要僅使用已知良好的模具。需要優化工藝并實施敏感的工藝控制步驟,以實現芯片完整性,以增加可用芯片的數量,并提供在進入 D2W 等工藝之前將好芯片從壞芯片中分類所需的準確信息。

無空洞鍵合,實現高產量

無空隙鍵合取決于電介質區域和銅焊盤的成功鍵合。在鍵合過程中,初始鍵合發生在室溫、大氣條件下的電介質與電介質界面處。隨后,通過退火和金屬擴散形成銅金屬到金屬連接。

混合鍵合表面必須超級干凈,因為即使是最微小的顆粒或最薄的殘留物也可能會擾亂工藝流程并導致設備故障。需要進行高靈敏度檢查來發現所有缺陷,以驗證芯片表面是否保持清潔,以實現成功的無空隙接合。

SiCN 已被證明比 SiN 或 SiO2等替代電介質具有更高的結合強度。最近的開發工作已證明 SiCN 的等離子體增強化學沉積 (PECVD) 溫度足夠低,足以滿足任何臨時條件的限制。粘合層(<200 °C )。薄膜的特性還包括所需的穩定性,以避免在去除臨時粘合層后隨著隨后的銅退火溫度升高(> 350°C)而解吸氫氣或碳氫化合物(這可能導致形成空隙)。

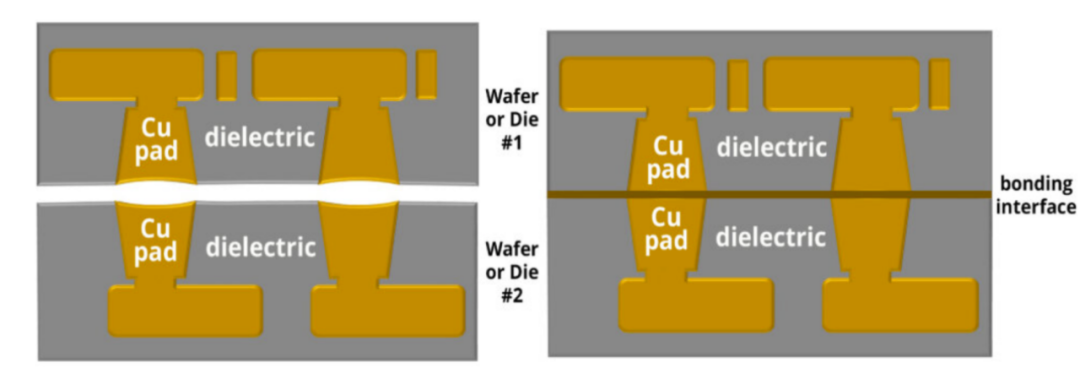

在混合鍵合之前,銅焊盤必須具有最佳的碟形輪廓,以允許銅在金屬鍵合過程中膨脹。

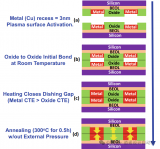

圖 3:描繪所需銅焊盤凹陷輪廓的預鍵合晶圓(或芯片)圖像(左)和顯示成功的芯片到芯片連接的鍵合后圖像(右)。

為了實現無空隙接合,需要淺且均勻的銅凹槽。在這里,高分辨率計量可用于監控和驅動過程控制和改進。

等離子切割可實現更清潔、更堅固的芯片

在每個工藝步驟中,必須仔細控制許多潛在的空隙、缺陷和不均勻性來源。即使是小至 100 納米的顆粒也可能導致數百個連接失敗和有缺陷的堆疊封裝。例如,在 D2W 混合鍵合中,單個芯片在被轉移并鍵合到第二個完整晶圓之前被切割,傳統的切割方法(例如機械鋸或激光開槽/切割)可能會引入顆粒或表面缺陷,特別是在模具邊緣,這會干擾后續的混合鍵合過程。等離子切割是一種替代方法,已在特定應用中的大批量生產中得到驗證,其中每個晶圓更多芯片或增強芯片強度等優勢超過了任何增加的加工成本。在混合鍵合的情況下,等離子切割工藝會產生極其干凈的芯片表面和邊緣,沒有與刀片切割相關的顆粒污染或邊緣碎片,也沒有激光碎片/重鑄/激光凹槽裂紋。在混合鍵合之前進行等離子切割芯片將導致更一致的鍵合、更低的缺陷率和更高的器件良率。

混合鍵合工藝控制

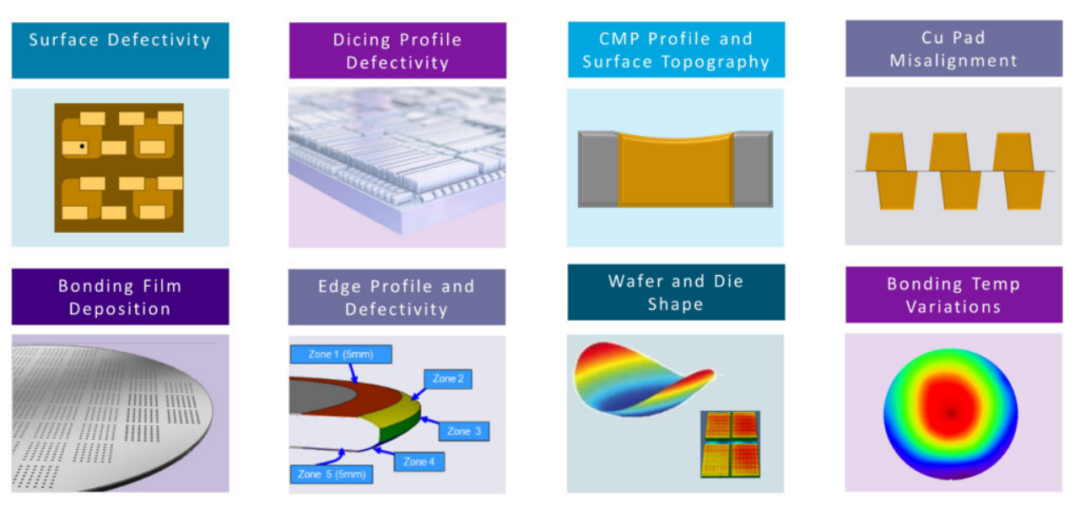

為了使混合鍵合成功過渡到高產量的大批量制造 (HVM),工藝控制至關重要。晶圓上的預鍵合不均勻性、空隙和其他缺陷會在鍵合過程中直接干擾銅互連并降低產品產量。影響鍵合的其他不均勻性來源包括 CMP 輪廓和表面形貌、銅焊盤未對準、晶圓形狀以及鍵合溫度的變化。這些問題中的每一個都必須從源頭仔細衡量和控制。

圖 4:可能對產品質量產生不利影響的因素示例

混合鍵合的一些關鍵工藝控制要求包括:

薄膜厚度和均勻性:必須仔細控制芯片內、整個晶圓以及晶圓與晶圓之間形成最終預粘合層的電介質膜厚度。

覆蓋對準:為了成功地以非常小的間距(目前約為 1-10μm)粘合表面,需要嚴格控制接合焊盤對準,以確保要接合的銅焊盤完美對齊,從而推動對覆蓋計量精度的需求不斷增加和芯片焊接控制。

缺陷率:混合鍵合中的直接電介質對電介質鍵合和銅對銅鍵合需要更清潔的表面,不含顆粒和殘留物,以最大限度地減少界面處的空洞。與傳統的焊料凸塊接口相比,這推動了等離子切割等優化工藝的采用,以及顯著更高的檢測靈敏度和嚴格的缺陷減少工作。

輪廓和粗糙度:成功的鍵合需要將表面輪廓和粗糙度控制在納米級,需要更精確的計量技術來幫助開發和控制 HVM 環境中預鍵合表面的制備。在鍵合之前,銅焊盤必須具有特定的碟形輪廓。

形狀和弓形:W2W 和 D2W 混合鍵合對晶圓形狀和弓形都很敏感,因此對晶圓級和芯片級形狀計量的需求日益增加,以進行表征和控制。

在實際鍵合工藝之后還需要額外的工藝和工藝控制步驟,例如 D2W 鍵合中的芯片間間隙填充,其中電介質沉積在單獨鍵合芯片之間和頂部上方。通過適當的應力控制措施,PECVD 可以使用 TEOS 前驅體生產極厚、無裂紋的 SiO,并且能夠承受后續步驟,例如 CMP 和光刻。

審核編輯:劉清

-

存儲器

+關注

關注

38文章

7632瀏覽量

166376 -

CMP

+關注

關注

6文章

152瀏覽量

26494 -

HPC

+關注

關注

0文章

332瀏覽量

24196 -

HBM

+關注

關注

1文章

404瀏覽量

15102

原文標題:混合鍵合將異構集成提升到新的水平

文章出處:【微信號:ICViews,微信公眾號:半導體產業縱橫】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

芯片晶圓堆疊過程中的邊緣缺陷修整

閃存沖擊400層+,混合鍵合技術傳來消息

將2.5D/3DIC物理驗證提升到更高水平

ADS1298將SPI提升到更高頻率將無法讀取任何信息,為什么?

三維堆疊封裝新突破:混合鍵合技術揭秘!

混合鍵合技術:開啟3D芯片封裝新篇章

混合鍵合將異構集成提升到新的水平

混合鍵合將異構集成提升到新的水平

評論