來源:芯系半導體

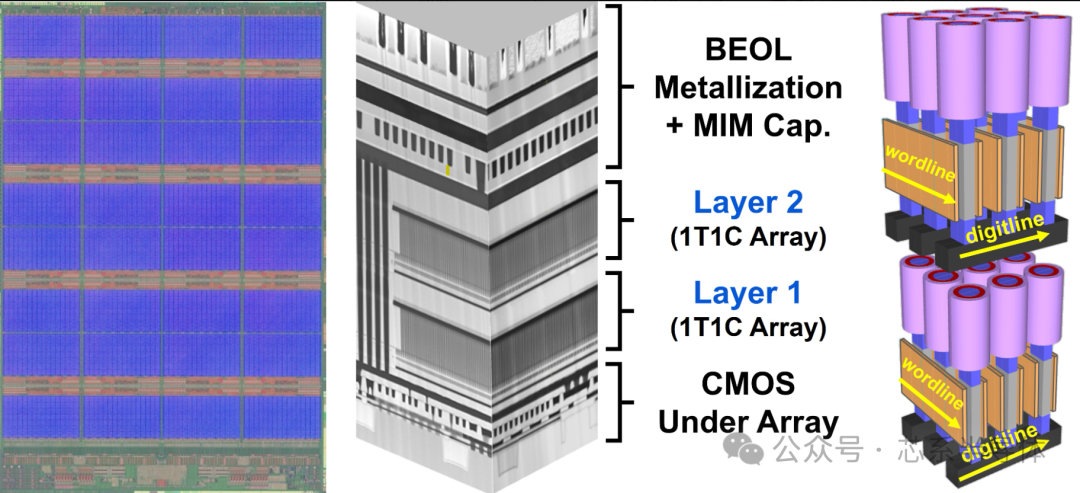

使用直接晶圓到晶圓鍵合來垂直堆疊芯片,可以將信號延遲降到可忽略的水平,從而實現更小、更薄的封裝,同時有助于提高內存/處理器的速度并降低功耗。目前,晶圓堆疊和芯片到晶圓混合鍵合的實施競爭異常激烈,這被視為堆疊邏輯與內存、3D NAND,甚至可能在高帶寬存儲(HBM)中的多層DRAM堆疊的關鍵技術。垂直堆疊使得芯片制造商能夠將互連間距從35μm的銅微凸點提升到10μm甚至更小。

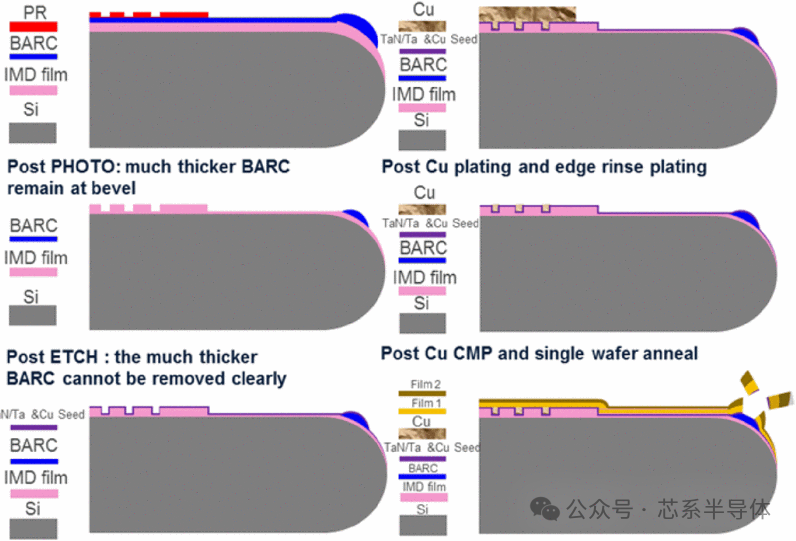

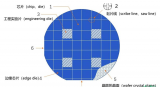

然而,垂直堆疊也伴隨著成本問題,這使得芯片制造商急于尋找減少晶圓邊緣缺陷的方法。這些缺陷顯著影響了晶圓上所有芯片的良率,而晶圓鍵合需要極為平坦、無缺陷的300mm晶圓。為了更好地控制整個晶圓加工過程中的晶圓邊緣缺陷,以及在融合和混合鍵合過程中,工程師們正在微調新舊工藝。這些工藝包括一系列技術,涉及晶圓邊緣的濕法和干法蝕刻、化學機械拋光(CMP)、邊緣沉積和邊緣修整步驟。

性能和功率效率的提升是顯著的,先進封裝正在通過芯片堆疊實現更高的處理速度和能力,將內存更接近CPU和GPU,將信息傳輸的線路縮短,從而加速計算。數據傳輸仍然占據芯片成本的很大一部分,通常需要進行幾十到幾百次內存訪問,也許你只有兩到四個周期來獲取你需要的值。系統如果能將內存更靠近處理器,將大大提升性能。而且,通過垂直堆疊發送信號,相比將信號從芯片傳輸到外部內存再返回的長距離傳輸,能顯著節省能量消耗。

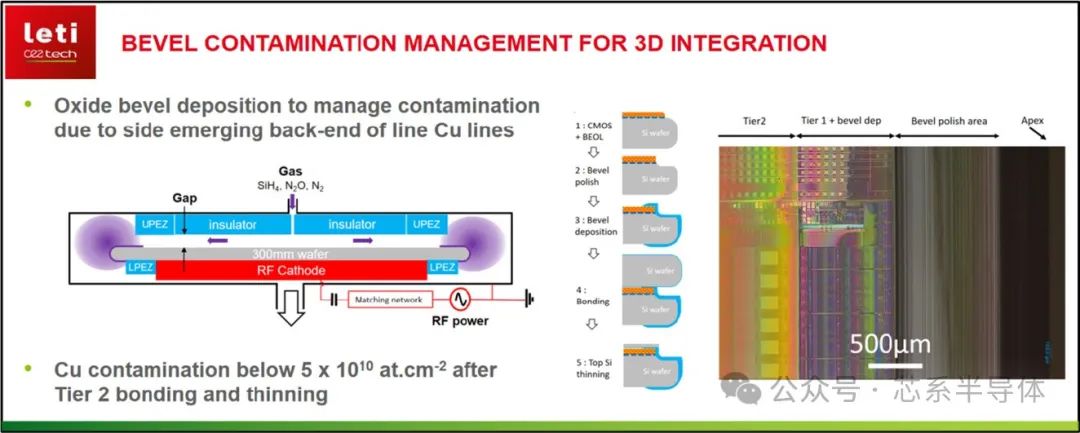

工藝也在針對先進封裝的特定需求進行優化。例如,Lam Research與其合作伙伴CEA-Leti優化了一種面向先進封裝應用的邊緣沉積工藝,該工藝已于去年推出。在晶圓薄化之前,對鍵合晶圓的邊緣進行沉積,可以提供增強支撐。這些結構需要材料來填補邊緣的空隙,因此沉積的薄膜作為支撐層起作用。否則,在CMP過程中,由于去除速度在邊緣更快,設備晶圓可能會在邊緣發生開裂,導致形成缺口,這種缺口最終可能導致晶圓間隙接近零。如果沒有邊緣沉積,晶圓在薄化過程中可能會發生邊緣開裂,嚴重影響良率。

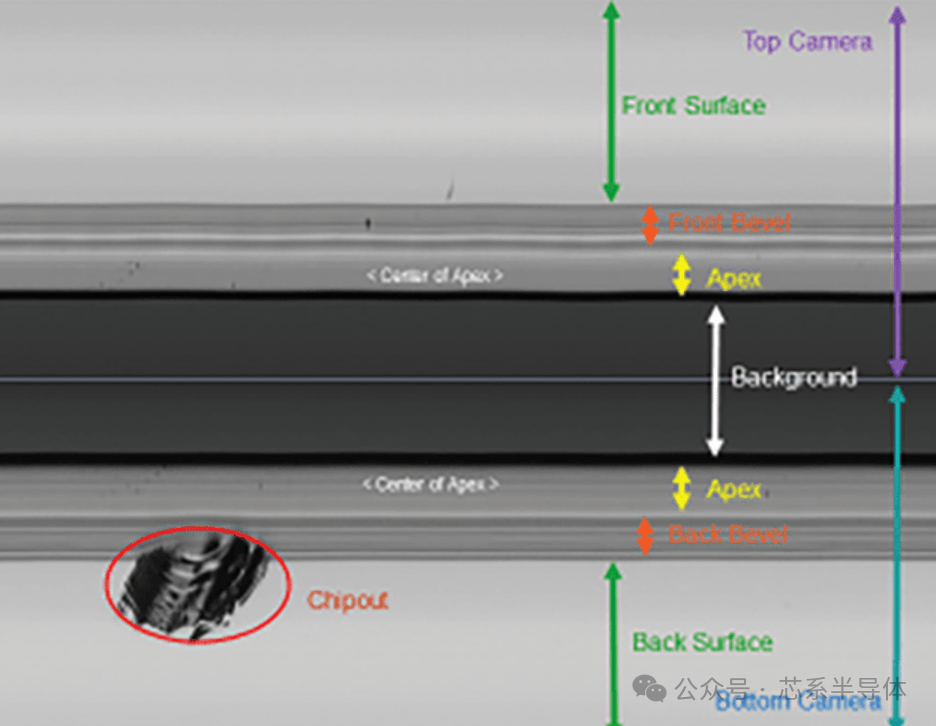

使用基于人工智能的先進工藝控制(APC)軟件,工程師可以提高整個晶圓以及堆疊中晶圓之間的均勻性分析。 APC涵蓋等離子體限制、薄膜均勻性、光刻工藝的均勻性等方面的分析 。準備進行混合鍵合的晶圓必須滿足嚴格的工藝規格,以確保高良率的混合鍵合,例如極為平坦(<1nm的中心到邊緣非均勻性)、無顆粒的晶圓、出色的晶圓/晶圓或芯片/晶圓對準、<200nm的芯片放置精度等。晶圓邊緣缺陷包括顆粒、崩邊、劃痕、薄膜剝離、晶圓處理過程中造成的損傷,這些缺陷可能會脫落并成為影響產品良率的缺陷。

CMP挑戰

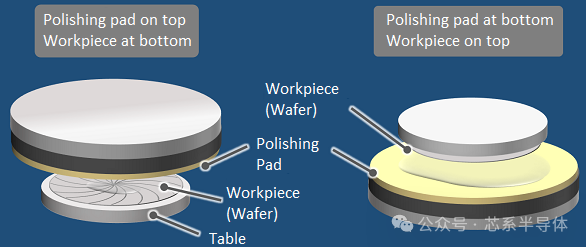

CMP(化學機械平坦化)最早由IBM在1980年代末期為引入銅大馬士革互連技術而開發,它為平整化晶圓并在更薄的封裝中增加更多功能提供了巨大的支持。晶圓平整度、控制邊緣滾落以及減少顆粒是CMP的關鍵目標。如今,除了在平整化淺溝槽隔離、介電材料和BEOL互連中的銅時使用外,晶圓研磨和CMP還在優化過程中被用于在鍵合后顯著薄化300mm硅晶圓的背面。

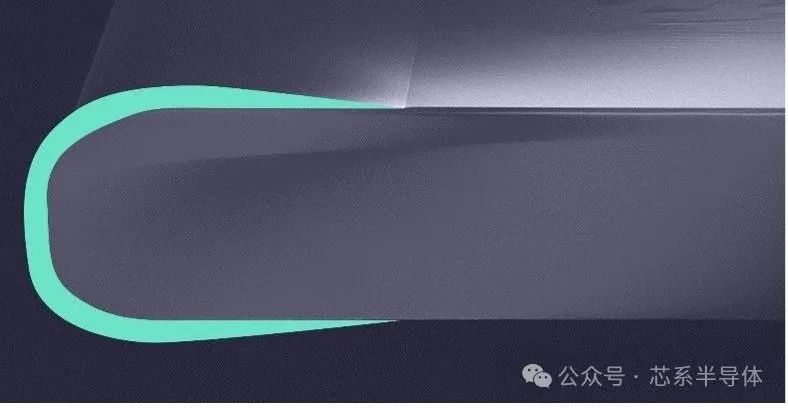

器件晶圓的質量也取決于起始硅的質量,晶圓邊緣的處理一直是一個問題。因為邊緣沒有鄰近材料,所以會發生不連續性或突變,改變了這些區域的物理特性。在裸硅晶圓的拋光過程中已經采取了一些措施來彌補這種變化,例如使用保持環。在這個CMP過程中,保持環支持晶圓在拋光夾具中,而晶圓邊緣僅與保持環接觸的部分非常小,裸硅晶圓邊緣本質上被塑造成三個部分——一個錐形部分、更鈍的邊緣,再一個錐形部分,這被證明是理想的設計,有助于提高CMP性能,相比之下,圓形邊緣的效果較差。

通量對所有晶圓工藝至關重要,如果CMP操作過快,就會引入非均勻性,并且有更高的機械損傷風險。因此,必須在最大化去除速率和保持均勻性、缺陷控制之間找到一個非常微妙的平衡。CMP設備供應商,如應用材料(Applied Materials)、江森自控技術(Ebara Technologies)和Axus Technology,與墊片和化學液體供應商一起,針對每個應用優化晶圓和晶圓間的均勻性,為目標工藝應用設計整個方案(化學試劑、拋光片、修整盤、P-CMP清潔劑)。

化學和機械工程師會考慮化學試劑、拋光片、修整盤的組合,控制CMP墊片的各種特性,包括剛性或硬度。顆粒的大小、分布和組成極為重要,因為這些特性部分決定了去除速率在晶圓之間的變化情況,表面圖案工程和優化的拋光墊技術也被采用,同時還會使用實時傳感和反饋技術,以便用戶在CMP過程中及時調整并進行修正。CMP和濕法/干法蝕刻工藝都在專用設備上優化,以去除晶圓邊緣的缺陷。

干法與濕法刻蝕

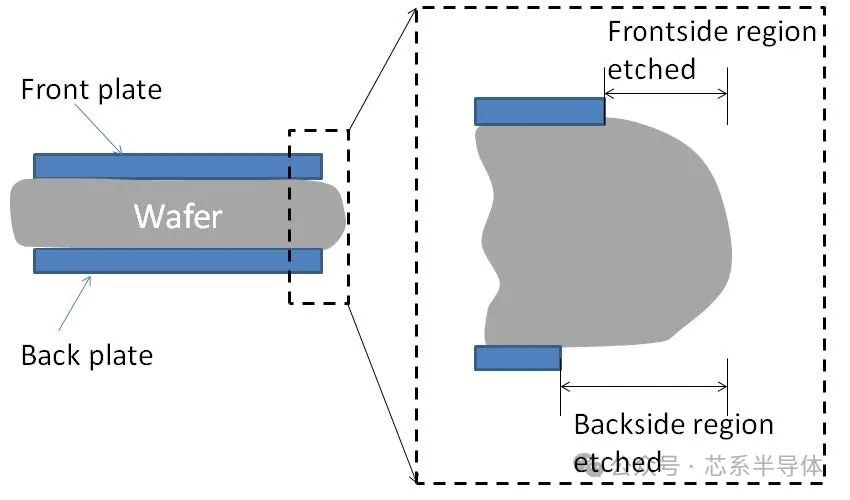

倒角刻蝕已投入生產約15年,旨在通過去除任何不需要的材料,如會損壞晶圓或從倒角移動到晶圓中心的顆粒缺陷來提高良率,需要在整個生產線上實施倒角刻蝕,因為工藝流程中有些環節會積聚這些材料。刻蝕設備經過優化,可去除晶圓邊緣上的任何類型薄膜,無論是介電材料、金屬還是有機物。在倒角的反應離子刻蝕(RIE)過程中,晶圓被上、下兩塊板固定,以確保只有晶圓的邊緣、倒角部分和背面邊緣暴露在外。

刻蝕過程根據客戶和具體工藝流程的不同有不同的使用方式,一些客戶等到積累了多層薄膜后,再清理至硅表面;而有時他們只是去除一層,比如用于深刻蝕NAND流程的厚碳硬掩模,這種碳掩模也是導電的,可能導致RIE腔室內的電弧,倒角刻蝕可以解決這些潛在的污染問題。

盡管濕法和干法清潔工藝各有其優勢,但設備制造商通常會根據高產量生產選擇其中一種。隨著技術節點的縮小,這個問題變得更加重要,因為人們希望從晶圓邊緣獲得更多的良品。目前我們有一個2毫米的邊緣排除要求,而客戶更希望是1毫米,所以晶圓邊緣的缺陷變得越來越重要。

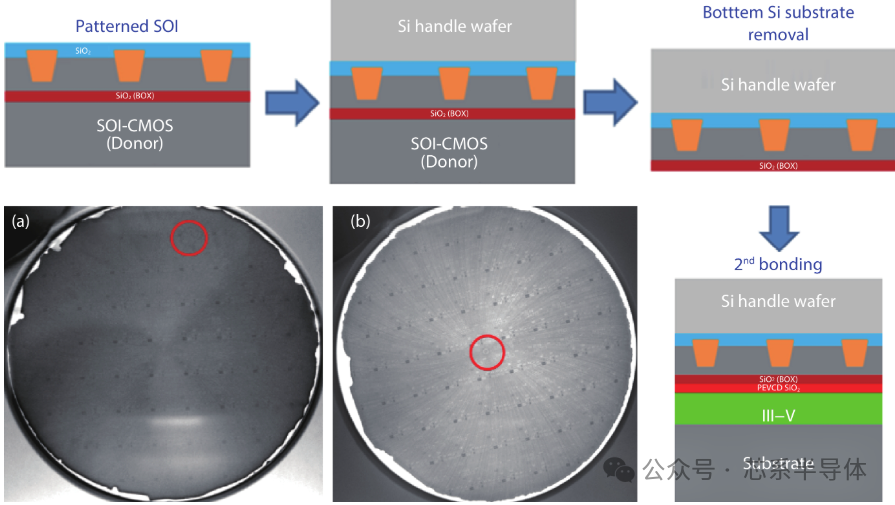

為了成功處理這些薄晶圓,在最終研磨/薄化步驟期間及之后,設備晶圓首先會與一片符合半導體行業標準的玻璃晶圓或硅載體晶圓進行鍵合。在鍵合步驟之前,這些晶圓將至少經過一步CMP處理步驟、隨后的CMP后處理清潔步驟和鍵合過程本身。如果這些步驟不能達到關鍵質量要求,鍵合晶圓的邊緣可能會出現空洞,甚至可能影響整個接合面。

例如,如果你有一層硅氮氧化物薄膜,可能會因為倒角處粘附力較弱而發生剝離。如果是像氮化鈦(TiN)這樣的材料,由于熱應力也可能會發生剝離,因此可以用SC1清潔,而且對于去除背面聚合物也有類似的應用。經過等離子刻蝕后的薄膜,背面會有聚合物附著在邊緣。CMP后也可能會有剝離現象。你需要去除這些,以防止剝離部分重新沉積在晶圓前面,造成缺陷并影響器件。

由于薄晶圓的處理和加工是一項挑戰,大多數芯片制造商使用暫時鍵合技術,將晶圓鍵合到玻璃晶圓上,以便在加工過程中提供支持。對于這些非常薄的應用,尤其是當晶圓的厚度被薄化到僅為200μm時,客戶使用Tyco環來固定晶圓,因為彎曲是最大的難題。

干法沉積

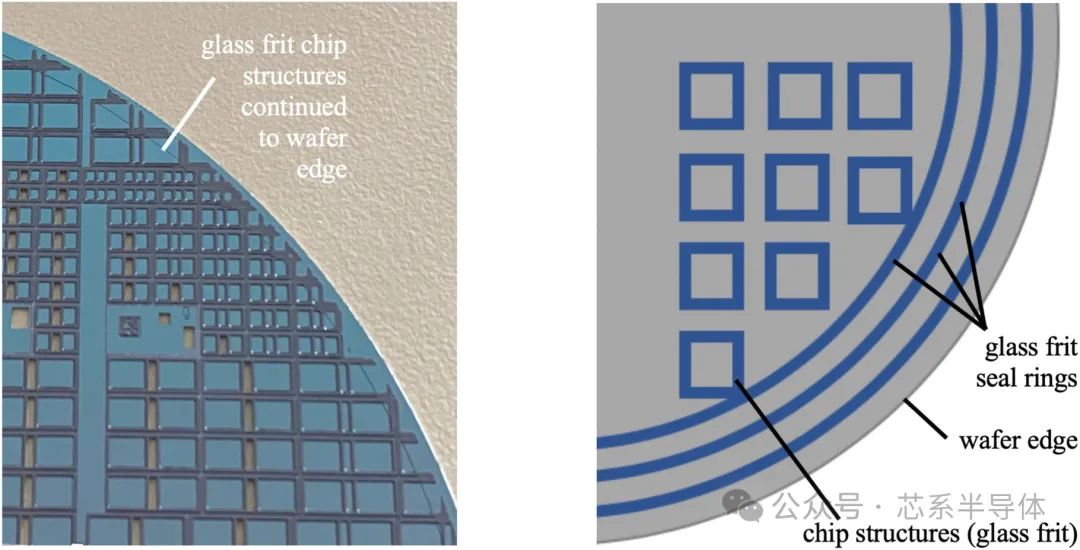

NAND設備是Lam公司首次開發倒角沉積的關鍵應用。倒角沉積系統沉積保護性的二氧化硅層,最早開始為3D NAND設備進行邊緣沉積,現在它已經擴展到其他應用,其中最有趣的用途之一是支持3D封裝的鍵合晶圓應用。沉積可以發生在正面、倒角或背面上的前幾個毫米,從幾百埃的厚度到幾微米的材料。

另一個目前處于研發階段的新應用是沉積薄的氮化硅薄膜,以控制銅污染。對于現有的應用,Lam公司的工程師預計每一步的良率提升將在0.2%到0.5%之間。

晶圓薄化與邊緣修整

用于先進器件的基底硅晶圓薄化會引入顯著的應力,當將其薄化時,基底硅變得越來越薄,因此會揭示出多個熱應力和機械應力,表現為變形。例如,對于NAND和先進邏輯器件來說,剩下的硅幾乎沒有了,剩余的全是金屬堆疊,而這些金屬層會增加應力。

為了更好地理解去除的硅量,可以考慮原始晶圓的厚度。對于300毫米硅晶圓,原始厚度為775微米,經過所有器件加工后,薄化至35到50微米。尤其是當你開始考慮‘內存計算’的概念時,你將邏輯芯片直接堆疊在非常高性能、高帶寬的內存之上,這樣就涉及到完全不同的器件和完全不同的力和應力,這些應力存在于兩者之間。

邊緣修整過程是一種濕法工藝,可以去除晶圓外緣的1到1.5毫米,可以在預粘接或粘接步驟時進行。但假設你正在進行融合粘接,每個晶圓都有CMP滾落,然后基本上就是倒角。所以如果你將它們粘接在一起,始終會有一個區域沒有完全填充。基本上會有一個非常非常小的間隙,慢慢地變為零。如果你現在開始研磨它,那個區域會變得非常脆弱,因為修整過程就像用刀修邊。因此,如何控制這個邊緣并管理它,目前是一個熱門話題。

在芯片到晶圓的粘接中,芯片邊緣的凸點非常容易受到應力的影響。如果設計人員無法改變應力分布,就必須調整設計規則,將I/O引腳移到芯片的中心。在晶圓到晶圓的粘接中,比如用于HBM時,晶圓邊緣的凸點最容易受到應力影響。你會發現邊緣有倒角,這很難控制,而且可能會有應力放大的邊緣損傷。人們正在尋找不同的方法來解決這一問題。晶圓邊緣修整在晶圓到晶圓的粘接、批量硅去除和CMP之前進行。許多傳統的CMP供應商提供邊緣修整工藝。

結論

晶圓邊緣缺陷是制造中面臨的重要挑戰,正在通過CMP、干濕刻蝕、邊緣沉積和晶圓邊緣修整等方式加以解決。盡管一些領先的器件制造商已經在生產中使用了混合粘接技術,但它仍然是一個相對不成熟且成本較高的過程。通過專門為晶圓堆疊優化這些工藝,更多行業領域將能夠使用這一賦能技術。

-

處理器

+關注

關注

68文章

19811瀏覽量

233599 -

堆疊

+關注

關注

0文章

37瀏覽量

16813 -

芯片晶圓

+關注

關注

0文章

6瀏覽量

8000 -

先進封裝

+關注

關注

2文章

463瀏覽量

515

原文標題:芯片晶圓堆疊過程中的邊緣缺陷修整

文章出處:【微信號:wc_ysj,微信公眾號:旺材芯片】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

晶圓級多層堆疊技術及其封裝過程

什么是3D芯片堆疊技術3D芯片堆疊技術的發展歷程和詳細資料簡介

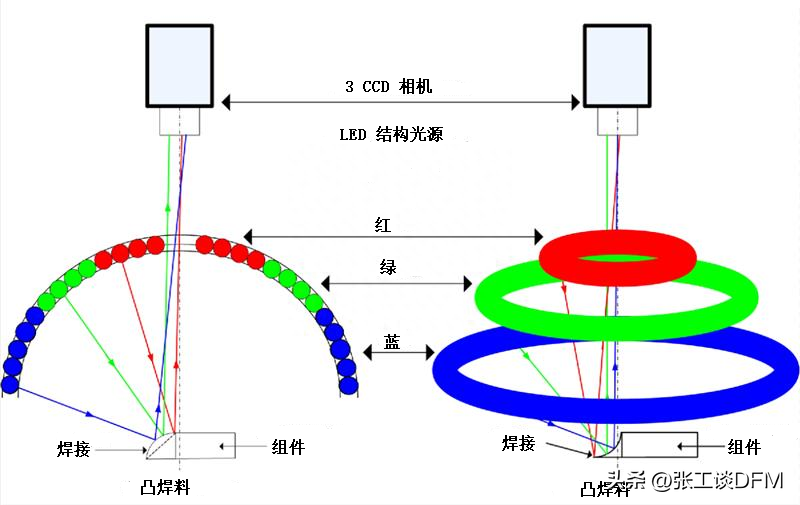

LED封裝過程中的存在缺陷檢測方法介紹

芯片晶圓里TaN薄膜是什么?TaN薄膜的性質、制備方法

五彩斑斕的芯片晶圓:不僅僅是科技的結晶

芯片晶圓堆疊過程中的邊緣缺陷修整

芯片晶圓堆疊過程中的邊緣缺陷修整

評論