Gating Cell

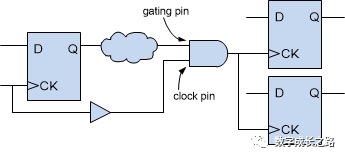

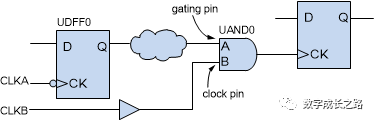

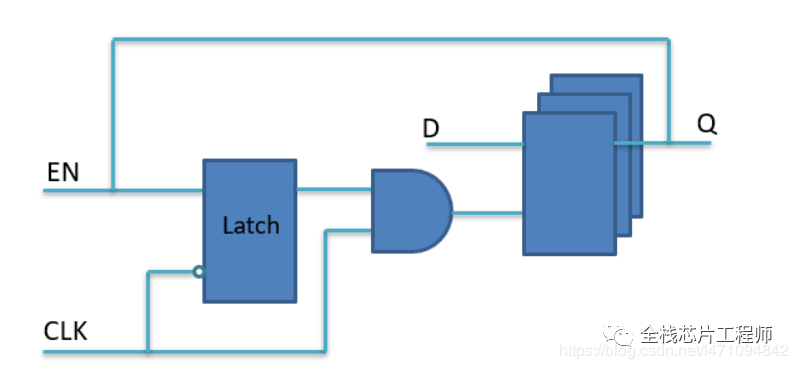

一個(gè)cell的一個(gè)輸入為clock信號(hào),另一個(gè)輸入為gating信號(hào),并且輸出作為clock使用,這樣的cell為gating cell。圖1中的and gate為gating cell。

圖1 gating cell

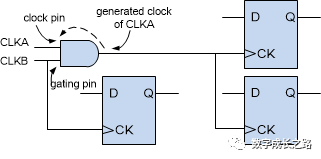

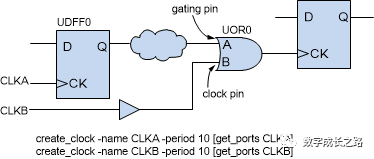

其中這個(gè)clock信號(hào)需要穿過(guò)gating cell,并且gating cell的fanout需要滿足以下任意一點(diǎn):1. 連接到register的ck pin;2. 連接到output pin或inout pin;3. 作為generated clock的master clock。gating信號(hào)不能是clock,或者是一個(gè)clock,但是不能穿過(guò)gating cell。圖2中CLKA與CLKB均為clock,但是and gate的輸出端定義了generated clock,master clock是CLKA,CLKB不會(huì)穿過(guò)and gate,這種情況下,PT工具會(huì)對(duì)and gate進(jìn)行clock gating check。

圖2 兩個(gè)clock輸入的gating cell

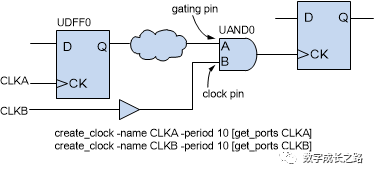

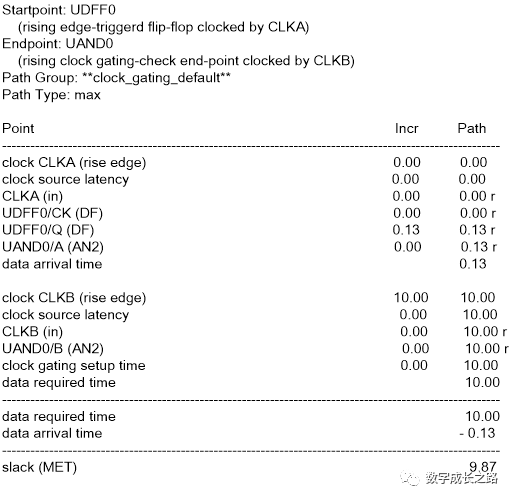

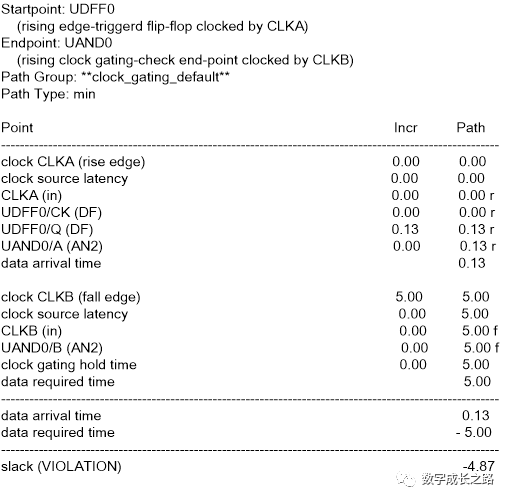

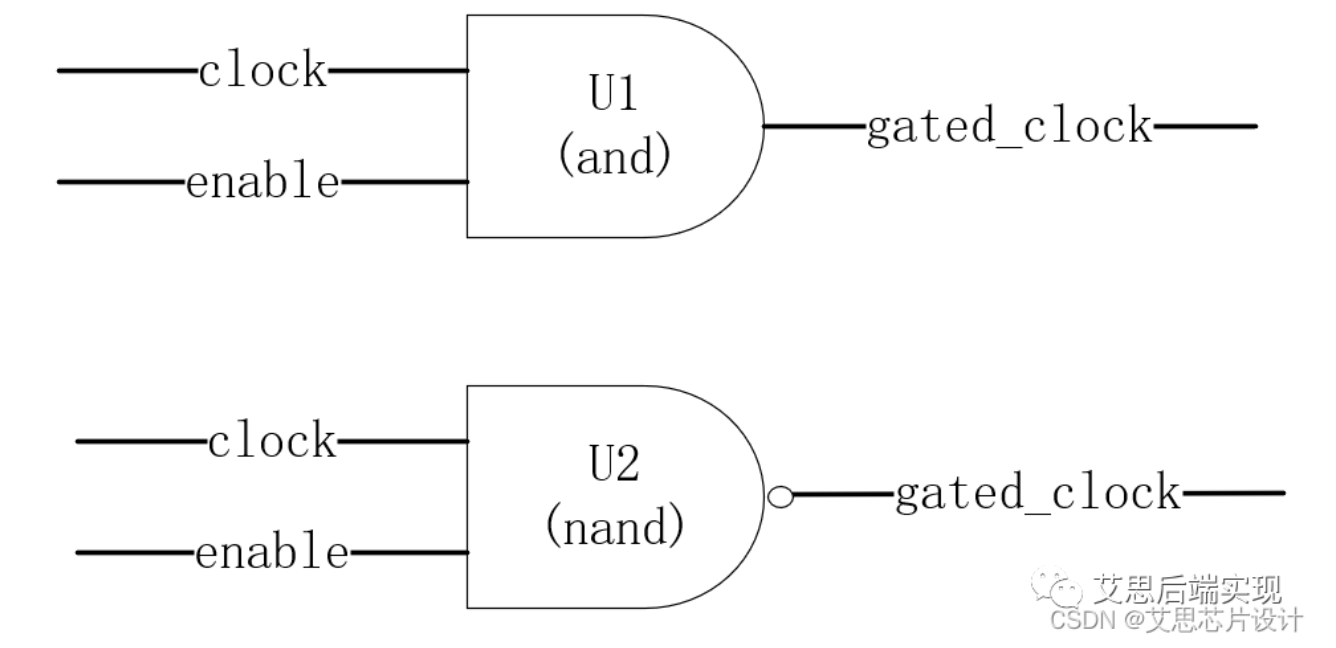

AND GATE的clock gating check

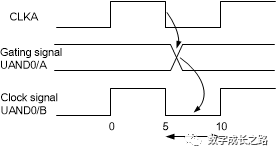

在and gate與nand gate上,PT工具會(huì)進(jìn)行active-high clock gating check, gating信號(hào)為高時(shí),clock能通過(guò)gating cell;同時(shí)gating信號(hào)的變化需要在clock信號(hào)為低時(shí)進(jìn)行,否則將會(huì)產(chǎn)生glitch。下面將會(huì)對(duì)and gate作為gating cell的timing關(guān)系進(jìn)行分析。

圖3 gating cell為and gate

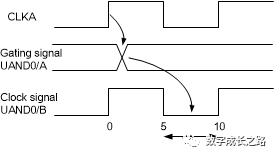

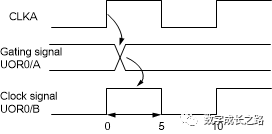

由圖4可以看出,UAND0的gating信號(hào)需要在CLKB為低時(shí)變化。即UAND/A的信號(hào)的變化窗口為5-10ns, clock gating setup check時(shí)需要UAND0/A在CLKB上升沿之前變,clock gating hold check時(shí)需要UAND0/A在CLKB下降沿之后變。PT工具在進(jìn)行setup/hold gating check時(shí),如果library中沒有定義gating cell的setup和hold time,工具會(huì)將setup與hold設(shè)置為0。我們也可以使用set_clock_gating_check指令設(shè)置setup與hold值。圖5與圖6分別是clock gating check setup與hold的timing報(bào)告。由于UAND0/A變得太快,在CLKB為高時(shí)變化,hold gating check有violation。

圖4 上升沿產(chǎn)生gating信號(hào)時(shí)序圖

圖5 上升沿產(chǎn)生gating信號(hào)setup check report

圖6 上升沿產(chǎn)生gating信號(hào)hold check report

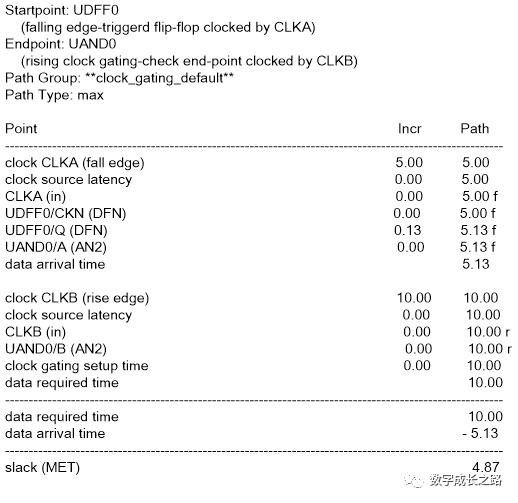

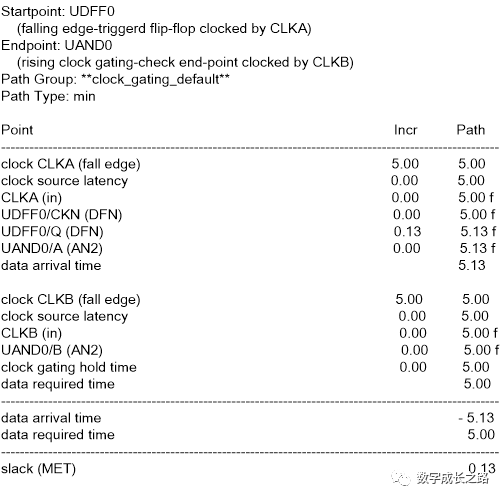

如果UDFF0采用下降沿觸發(fā),如圖7~圖10,setup與hold gating checks都能滿足要求。

圖7 gating 信號(hào)下降沿產(chǎn)生

圖8 下降沿產(chǎn)生gating信號(hào)時(shí)序圖

圖9 下升沿產(chǎn)生gating信號(hào)setup check report

圖10 下升沿產(chǎn)生gating信號(hào)hold check report

OR GATE的clock gating check

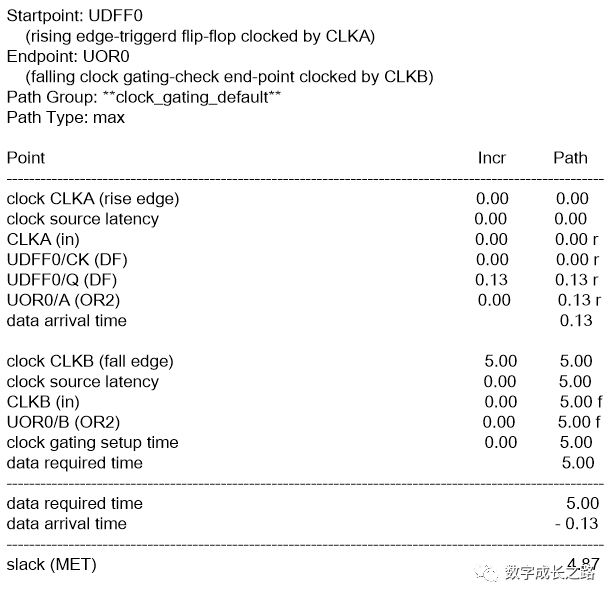

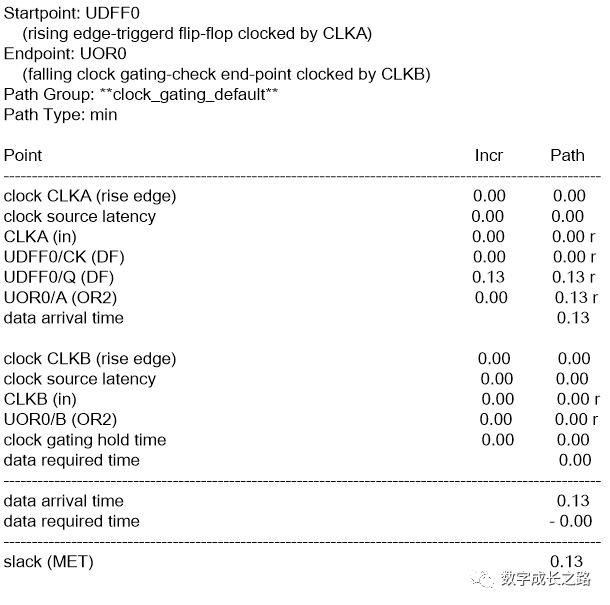

or gate與nor gate上PT工具會(huì)進(jìn)行active-low clock gating check, gating信號(hào)為低時(shí),clock能通過(guò)gating cell;同時(shí)gating信號(hào)的變化需要在clock信號(hào)為高時(shí)進(jìn)行,否則將會(huì)產(chǎn)生glitch。下面將會(huì)對(duì)or gate作為gating cell的timing關(guān)系進(jìn)行分析。如圖11~圖14,UDFF0是上升沿觸發(fā)寄存器,使用or gate作為gating cell, setup與hold gating check均滿足timing要求。

圖11 gating cell為or gate

圖12 gating cell為or gate時(shí)序圖

圖13 or gate setup gating check report

圖14 or gate hold gating check report

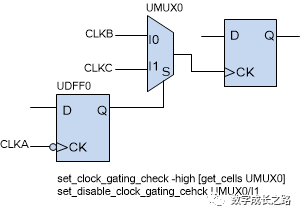

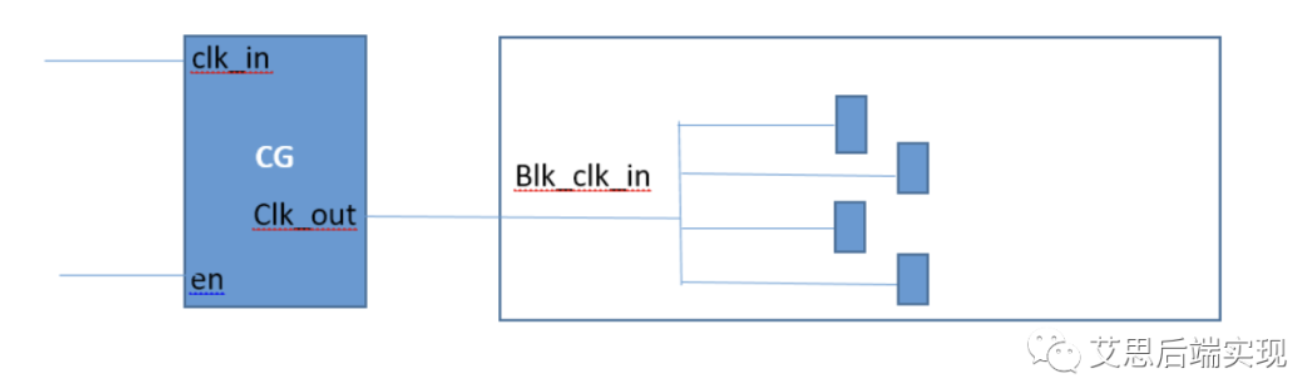

Clock Gating with a MUX

PT工具識(shí)別到and gate與or gate這種簡(jiǎn)單功能的cell為gating cell時(shí),會(huì)自動(dòng)進(jìn)行clock gating check。但是像mux或者xor這種復(fù)雜功能的cell,PT工具會(huì)給出一個(gè)warning, no clock gating check inferred。除非我們?cè)O(shè)置set_clock_gating_check指令。如果設(shè)置了指令, cell不符合gating cell的功能,PT工具也會(huì)給出一個(gè)warning。

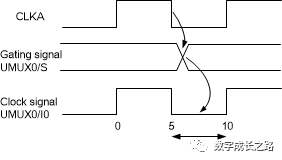

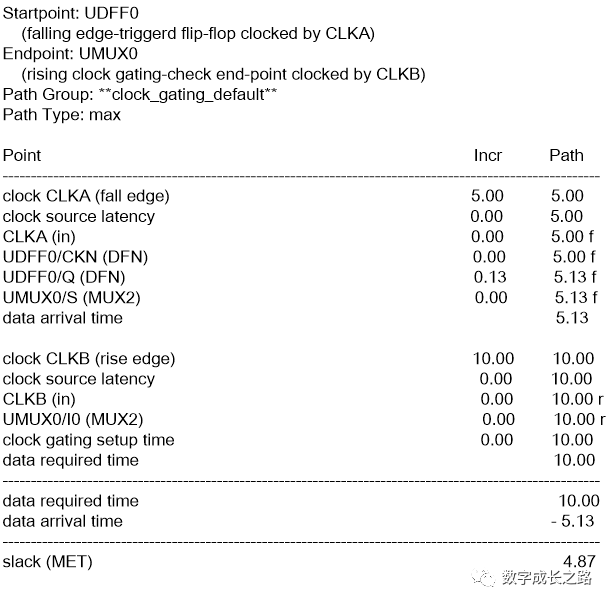

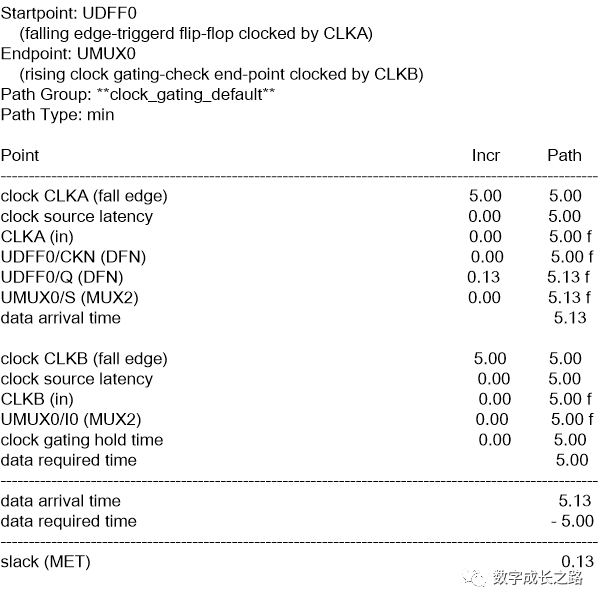

圖15中,CLKA與CLKB是周期為10,duty cycle為50%的時(shí)鐘,當(dāng)UMUX0/S變化時(shí),需要保證CLKC已經(jīng)關(guān)上了,CLKB處于低。類似active-high clockgating check。我們不關(guān)心的pin,UMUX0/I1,可以將clock gating check關(guān)掉。圖17~圖18為mux setup/hold gating check report。

圖15 mux做gating cell

圖16 mux切換時(shí)序

圖17 mux setup gating check report

圖18 mux hold gating check report

-

寄存器

+關(guān)注

關(guān)注

31文章

5421瀏覽量

123306 -

連接器

+關(guān)注

關(guān)注

99文章

15210瀏覽量

139275 -

觸發(fā)器

+關(guān)注

關(guān)注

14文章

2032瀏覽量

61870

發(fā)布評(píng)論請(qǐng)先 登錄

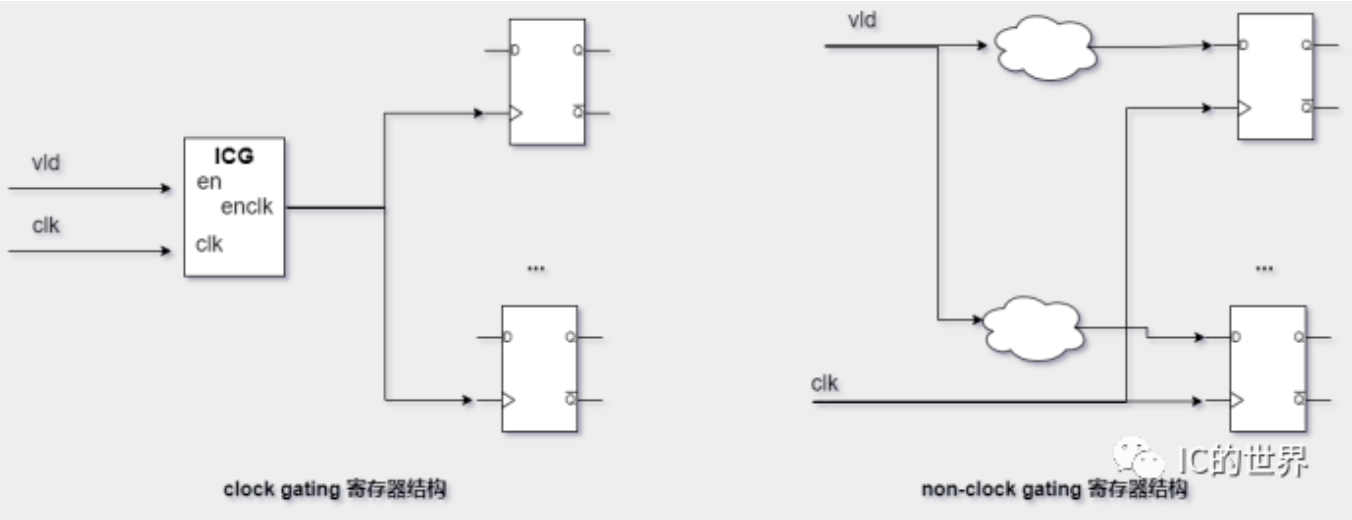

clock-gating的綜合實(shí)現(xiàn)

淺析clock gating模塊電路結(jié)構(gòu)

電動(dòng)汽車用鋰離子電池技術(shù)的國(guó)內(nèi)外進(jìn)展簡(jiǎn)析

PCB線路板電鍍銅工藝簡(jiǎn)析

EPON技術(shù)簡(jiǎn)析

鼠標(biāo)HID例程(中)簡(jiǎn)析

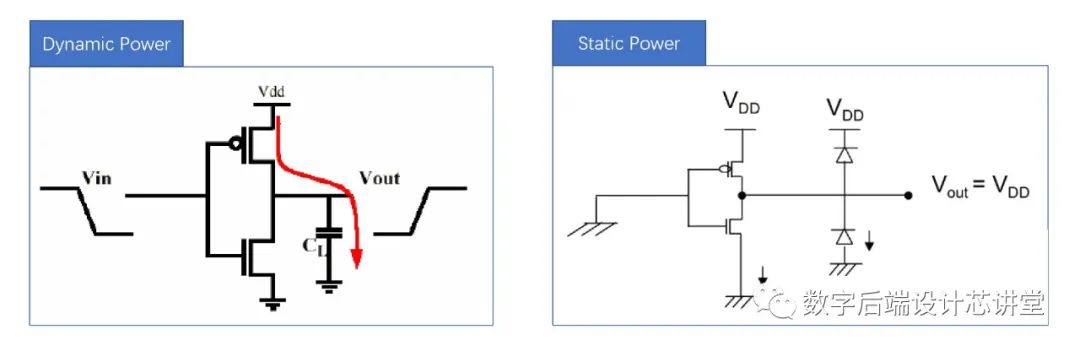

低功耗設(shè)計(jì)基礎(chǔ):Clock Gating

低功耗之門控時(shí)鐘設(shè)計(jì)

clock gate時(shí)序分析概念介紹

ASIC的clock gating在FPGA里面實(shí)現(xiàn)是什么結(jié)果呢?

AND GATE的clock gating check簡(jiǎn)析

AND GATE的clock gating check簡(jiǎn)析

評(píng)論