Delay值是多少才算合格呢?這一篇開始講解路徑(Path)的概念,以及衡量Path Delay是否合格的標(biāo)準(zhǔn)----建立時(shí)間(setup time)和保持時(shí)間(hold time)。最后會(huì)用實(shí)際的例子來介紹同一條path在物理設(shè)計(jì)的不同階段的變化,在什么階段會(huì)修setup,什么時(shí)候會(huì)開始修hold等實(shí)踐知識(shí)?

四種路徑

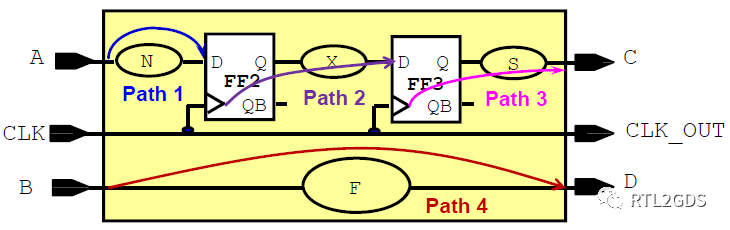

STA是基于路徑(Path Based)進(jìn)行檢查的,一般路徑的起點(diǎn)(Startpoint)和終點(diǎn)(Endpoint)都是存儲(chǔ)單元,即使是輸入輸出相關(guān)的路徑,我們也是假設(shè)存在一個(gè)虛擬的外部寄存器作為時(shí)序路徑的起點(diǎn)或者終點(diǎn)。然而,按照一般的分法,路徑分為四種類型,如圖所示:

上圖中,四類Path的起點(diǎn)和終點(diǎn)如下表所示:

當(dāng)然,設(shè)計(jì)中也可能有一些到clock gate的path,或者跟memory相關(guān)的path,暫時(shí)都把這些當(dāng)成寄存器來分類就可以。在編寫時(shí)序約束文件(SDC)時(shí),要照顧到每一種類型的path,避免遺漏。現(xiàn)在的后端流程一般會(huì)把這四類path進(jìn)行分組(Path Group),分別為IN2REG (Path 1),REG2REG (Path 2),REG2OUT (Path 3), IN2OUT (Path 4),方便工具按照不同的權(quán)重對(duì)它們分別優(yōu)化,避免相互影響。標(biāo)準(zhǔn)的SDC命令是“group_path”,各家工具都支持。

Setup/Hold Time

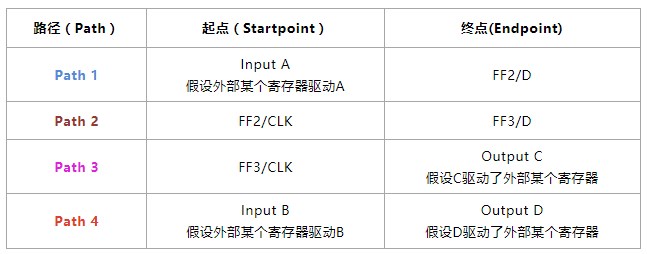

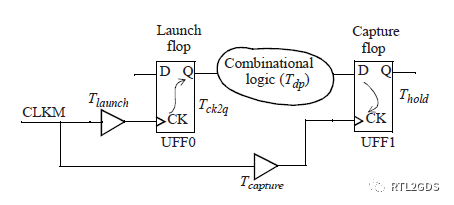

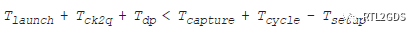

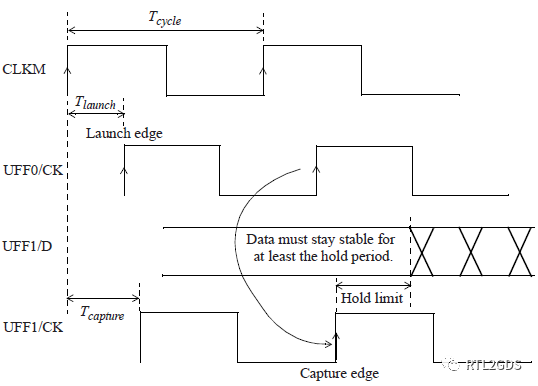

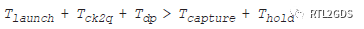

為什么會(huì)有setup time,hold time的要求呢?這與時(shí)序單元的工作方式有關(guān),數(shù)據(jù)從發(fā)送寄存器(Launch flop)傳輸?shù)浇邮占拇嫫鳎–apture flop),它是在時(shí)鐘沿采樣的(上升或者下降沿),數(shù)據(jù)是以流水線的方式一個(gè)周期往后打一拍,所以保證采樣時(shí)刻數(shù)據(jù)的正確性至關(guān)重要,setup就是要求在采樣時(shí)刻數(shù)據(jù)已經(jīng)正確且穩(wěn)定,hold就是要求下一個(gè)數(shù)據(jù)傳來之前在上一個(gè)數(shù)據(jù)已經(jīng)完成采樣,不會(huì)把上一個(gè)數(shù)據(jù)覆蓋。下圖非常清楚地解釋了setup和hold的概念,真的是“一盜圖值千言”。

Path示例

Setup概念圖示

Hold概念圖示

這里經(jīng)常有個(gè)奇怪的面試問題: 是setup重要還是hold重要? 大概是考驗(yàn)大家的實(shí)際項(xiàng)目經(jīng)驗(yàn)吧,setup不滿足還可以通過降低頻率來測(cè)試,hold不滿足就沒什么辦法了。但是項(xiàng)目中,由于hold修復(fù)方法比較簡(jiǎn)單直接,一般是在setup可控的前提下再修復(fù),所以一般在布局階段只考慮setup,而在建立時(shí)鐘樹后再去考慮hold。把hold放在后面去修復(fù),并不代表不重要,只是體現(xiàn)了修復(fù)的難易程度罷了。

實(shí)例分析

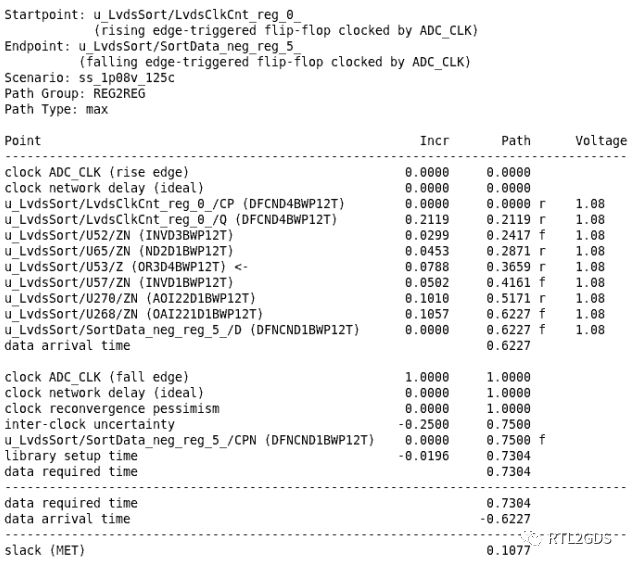

上面說過,數(shù)據(jù)采樣可以是上升沿,也可以是下降沿,下面以一條半周期的path為例,展示它在整個(gè)物理設(shè)計(jì)過程中可能的變化過程,也借此提供一個(gè)分析時(shí)序問題的縱向比較的方法學(xué):

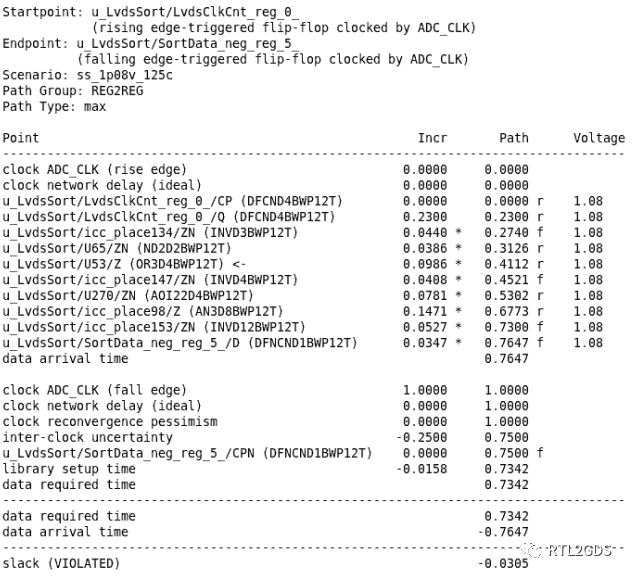

布局(place)之前:

這條path的詳細(xì)介紹如下,其中clock周期是2ns:

- “ Startpoint ”是LvdsClkCnt_reg_0_,它是“ADC_CLK”的上升(r)沿采樣的

- “ Endpoint ”是SortData_neg_reg_5_,它是“ADC_CLK”的下降(f)沿采樣的

- “ Scenario ”代表了這條path上所用的cell的工作的PVT

- “ Path Group ”表示path的類型分組,在上一節(jié)介紹過

- “ Path Type ”表示path類型,可能是max(表示setup),min(表示hold),或其它。

- clock network delay是ideal的,因?yàn)闆]有建立時(shí)鐘樹

- 從“ADC_CLK” clock的源頭到LvdsClkCnt_reg_0_/CP(正沿),再到SortData_neg_reg_5_/D的整個(gè)path每一級(jí)的delay加總起來是0.6227ns(叫做arrival time),這一段叫 launch path

- 從“ADC_CLK” clock的源頭到SortData_neg_reg_5_/CPN(負(fù)沿),加上clock reconvergence pessimism ( CRPR ),clock uncertainty,以及capture寄存器庫(kù)自帶的setup time等,形成了required time(0.7304ns),這一段叫 capture path

- **slack ** = required time - arrival time 不小于0表示setup合格

可以看出此時(shí)的path,setup time還是滿足的。

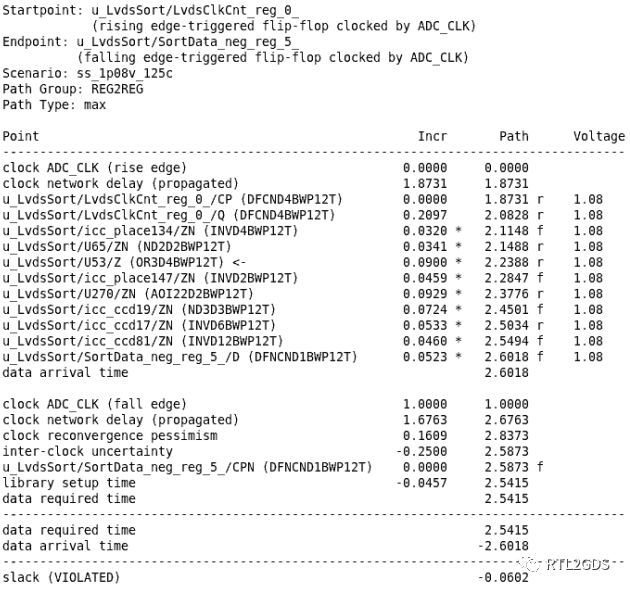

剛剛布局(place)之后,但還沒有建立時(shí)鐘樹(cts):

可以看出在path中,有些stdcell被優(yōu)化了,也多了一些inverter,這是工具的行為,但是最終slack為負(fù)數(shù),說明setup time不達(dá)標(biāo)了。

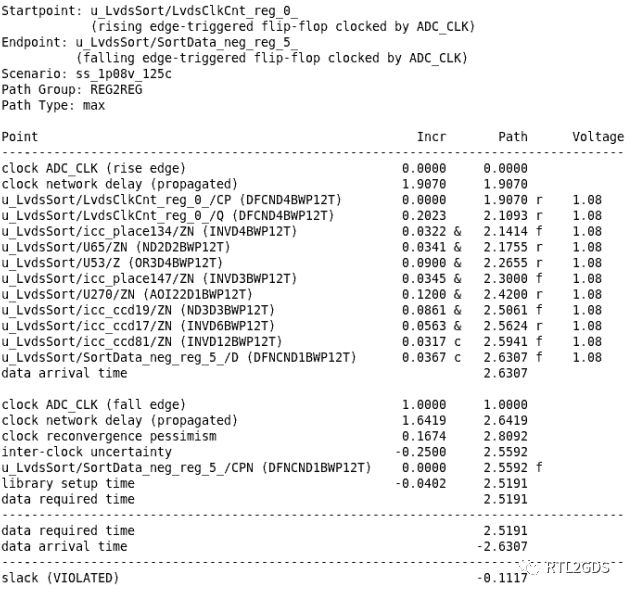

建立時(shí)鐘樹(cts)之后,布線(route)之前:

此時(shí)的path中已經(jīng)有了真實(shí)的clock tree,所以clock network delay從ideal變成了propagated,delay值也從0變?yōu)?.8731ns,而且到兩個(gè)寄存器的clock pin的delay也不一樣,差值就叫clock skew,這條path的skew對(duì)setup time是有害的,不過此時(shí)的CRPR也不是0了,而是0.1609ns,抵消掉部分clock skew的影響。這個(gè)階段工具其實(shí)又做了一些優(yōu)化,比如icc_place134這個(gè)cell,從原先的INVD3BWP12T變大到INVD4BWP12T(sizeup)等等。

布局(place)+ 建立時(shí)鐘樹(cts)+ 布線(route)之后:

此時(shí)的path相比之前,有了真實(shí)的繞線,Net Delay會(huì)更差,而且也會(huì)引入串?dāng)_噪聲,工具會(huì)進(jìn)一步進(jìn)行優(yōu)化,比如icc_place147和U270等,都變大了。不過最終的slack還是負(fù)數(shù),并沒有達(dá)標(biāo)。

對(duì)于實(shí)踐方面,大概率(80%以上)還有一個(gè)面試問題:“項(xiàng)目中有沒有碰到timing/routing比較難的設(shè)計(jì),你是怎么解決的?”,必須要結(jié)合項(xiàng)目經(jīng)歷準(zhǔn)備,可以思考上面的path最后setup還是沒滿足,有怎么解決辦法?

-

寄存器

+關(guān)注

關(guān)注

31文章

5421瀏覽量

123307 -

CPN

+關(guān)注

關(guān)注

0文章

6瀏覽量

10352 -

時(shí)鐘樹

+關(guān)注

關(guān)注

0文章

56瀏覽量

10964 -

SDC

+關(guān)注

關(guān)注

0文章

49瀏覽量

15812 -

ADC采樣

+關(guān)注

關(guān)注

0文章

134瀏覽量

13122

發(fā)布評(píng)論請(qǐng)先 登錄

UCB_SWAP配置信息共16條,寫入一條有效配置后,上一條需寫1使配置無效是為什么?

AD9敷銅時(shí)如何一條一條網(wǎng)絡(luò)的敷銅

怎么在LABVIEW中實(shí)現(xiàn)讓程序按照數(shù)據(jù)庫(kù)中的數(shù)據(jù)一條一條的按步進(jìn)順序程序走?

DSP執(zhí)行一條語(yǔ)句的時(shí)間

請(qǐng)問gps接收數(shù)據(jù)是每接收一條解析一條嗎?

怎樣在同一條CAN總線上連接兩個(gè)不同的微控制器呢

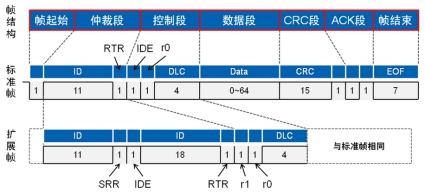

一條CAN報(bào)文到底有多少位?

如何做一條合格的path?同一條path在物理設(shè)計(jì)不同階段的變化

如何做一條合格的path?同一條path在物理設(shè)計(jì)不同階段的變化

評(píng)論