4. 異步FIFO(先進先出)

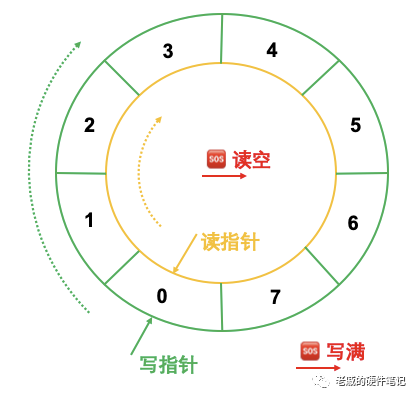

圖<6>是深度(depth)為8的異步FIFO的示意圖。其中,0~7代表8個寄存器,他們組成了一個環(huán)。

綠色的外圈代表寫操作,按照順時針方向(地址遞增),依次寫入不同的寄存器;寫完所有的寄存器,再從寄存器#0開始,循環(huán)不斷;寫指針(wrtie pointer)代表當(dāng)前寫入寄存器的地址;寫操作是寫時鐘的同步電路。

橙色的內(nèi)圈代表讀操作,按照順時鐘方向(地址遞增),依次讀取不同的寄存器,讀完所有8個寄存器,再從寄存器#0開始,循環(huán)不斷;讀指針(read pointer)代表當(dāng)前讀取寄存器的地址;寫操作是讀時鐘的同步電路。

圖<6>

對于特定寄存器,F(xiàn)IFO必然是先寫后讀;FIFO內(nèi)部,讀指針在不斷追趕寫指針。當(dāng)寫指針跑的太快,比如已經(jīng)超越讀指針一圈,這種狀態(tài)就是寫滿(FIFO full),這時候繼續(xù)寫入就會把覆蓋(overwrite)未被讀取的寄存器(上溢,overflow),造成數(shù)據(jù)的丟失;另一種情況,讀指針等于寫指針,這種狀態(tài)就是讀空(FIFO empty),指向的寄存器還沒有被寫入,這時候繼續(xù)讀,讀出來的是空的或者是上一個循環(huán)已經(jīng)讀取過的數(shù)據(jù)(下溢,underflow)。

寫滿(Full):讀指針 = 寫指針 + FIFO深度;

讀空(Empty):讀指針 = 寫指針;

寫滿和讀空是兩種邊界狀態(tài),更多情況下,F(xiàn)IFO處于寫滿和讀空之間的中間狀態(tài)。讀指針和寫指針之間的差值形成了水位圖(watermark),代表著FIFO的實際使用率。

異步FIFO的實現(xiàn)有很多技術(shù)考量,最重要的是跨時鐘域(CDC)問題:寫指針和寫滿信號屬于寫時鐘的時鐘域;讀指針和讀空信號屬于讀時鐘的時鐘域。有很多文獻討論異步FIFO的實現(xiàn)細節(jié),有興趣的可以參考文獻<1>。

異步FIFO的設(shè)計已然成熟,經(jīng)過封裝后成為異步FIFO模塊(或者IP),比如圖<7>。我們可以直接調(diào)用而不必顧慮內(nèi)部的細節(jié)。

圖<7>

圖<7>中,左側(cè)是寫操作,右側(cè)是讀操作,讀寫操作工作在各自的時鐘域,互不影響。只要沒有寫滿信號,寫操作就可以一直持續(xù);只要沒有讀空信號,讀操作也可以一直持續(xù)。數(shù)據(jù)源源不斷從左側(cè)流向右側(cè)。

5. RX彈性緩存(Elastic Buffer)

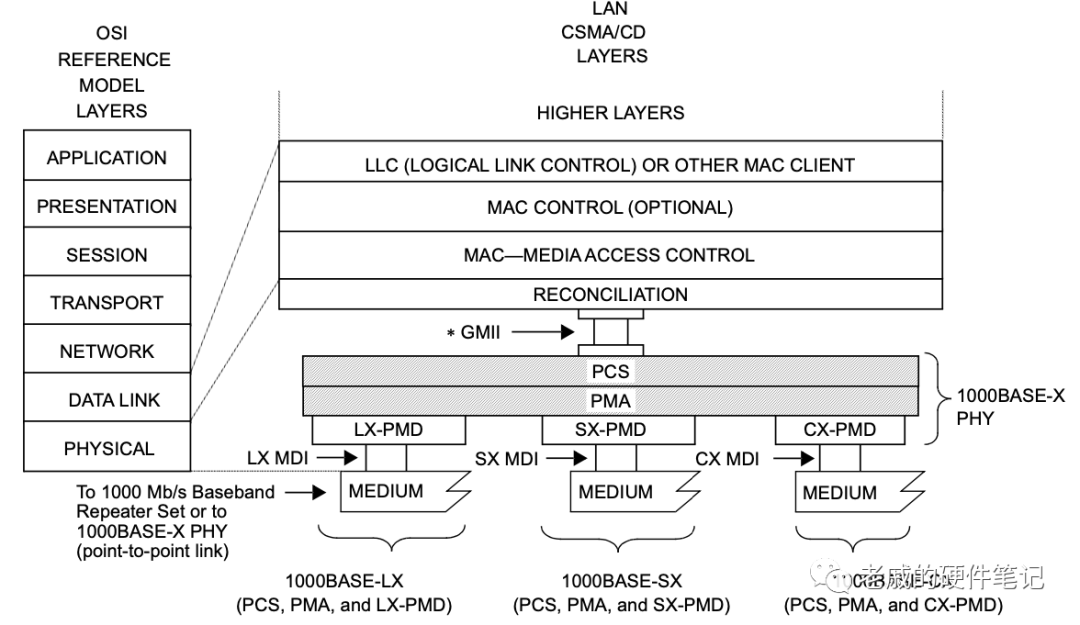

在以太網(wǎng)的接收端,PCS層使用彈性緩存來補償時鐘的PPM頻率差異。

10b編碼經(jīng)過異步FIFO,從RX時鐘的時鐘域轉(zhuǎn)換到本地時鐘域。

802.3標(biāo)準(zhǔn)沒有提供異步FIFO的實現(xiàn)細節(jié),老戚從Xilinx的用戶手冊找了一個1000Base-X設(shè)計例子做為參考。

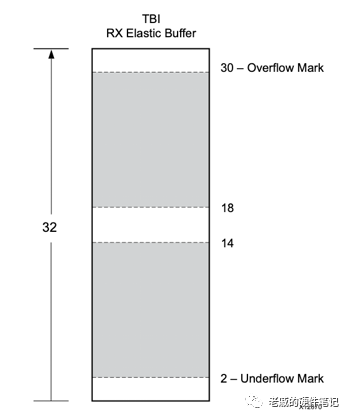

這是一個深度為32的異步FIFO。計算讀指針和寫指針的差距,形成了圖<8>的水位圖。

圖<8>

當(dāng)水位上升時,意味著FIFO讀取的速度大于寫入的速度;反之,則意味著FIFO讀取的速度小于寫入的速度。

上篇說到,PCS和PMA之間(TBI)的10b編碼是連續(xù)的。讀寫時鐘(本地時鐘 VS RX時鐘)的頻率差異會導(dǎo)致水位或者上升到上溢,或者下降到下溢。

RX彈性緩存能夠識別10b碼型,然后根據(jù)水位來相應(yīng)的插入或者刪除特定的10b碼型。

當(dāng)水位上升到上半部灰色區(qū)間時,就刪除IDLE碼;

當(dāng)水位下落到下半部灰色區(qū)間時,就插入IDLE碼;

當(dāng)水位處于中間區(qū)域時,既不刪除也不插入。

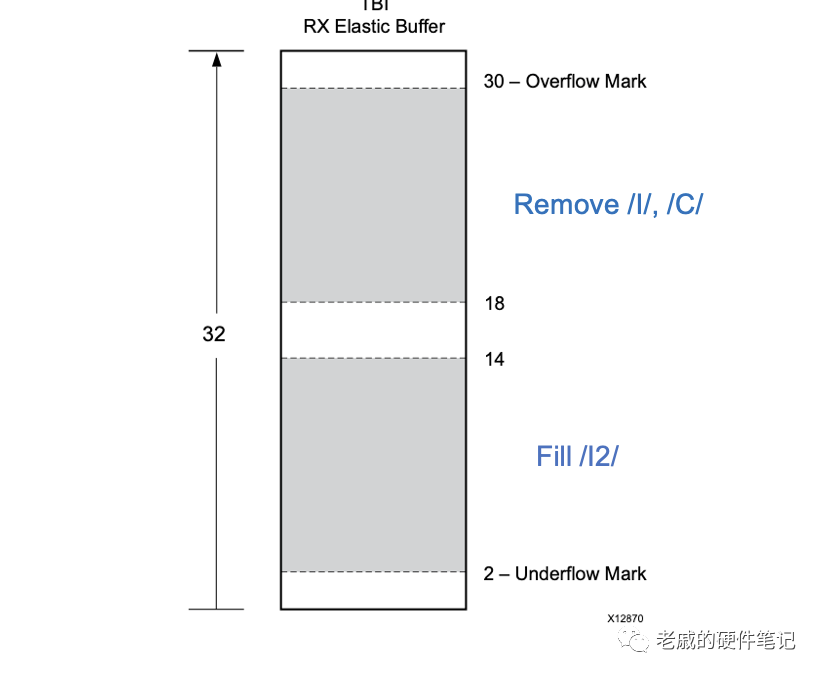

圖<9>

MAC層的以太網(wǎng)幀之間的間隙(IPG)最小是12字節(jié)(Octets);而在PCS層,最小IPG轉(zhuǎn)換成10b碼型:/T/,/R/,5/I/*。(見上篇)

由于不能刪除幀內(nèi)數(shù)據(jù),MAC幀越長,頻差積累的影響就會越大。

假設(shè)RX時鐘頻率為正偏100PPM,本地時鐘頻率為負偏100PPM,考慮最長的Jumbo幀:

9216 Byte * (1.0001 / 0.9999 - 1) = 1.84 Byte

或者說,刪除一個/I/(/I2/ = /K28.5/D16.2/)就足以補償最大時鐘PPM偏差。

如果RX的時鐘慢于本地時鐘,那么就需要插入IDLE碼。

理想的水位是中間,比如16,這也意味著數(shù)據(jù)經(jīng)過FIFO的時候會有16x 10b (128ns)的延時。

6. 為什么還會丟包?

RX時鐘慢于本地時鐘的情況下,在RX的10b數(shù)據(jù)中插入IDLE碼,IPG變大,不會造成問題;反過來,會刪除部分的/I/,結(jié)果可能導(dǎo)致以太網(wǎng)幀的IPG被削減到標(biāo)準(zhǔn)之下,雖然并不損失正常數(shù)據(jù),但是在MAC層可能成為問題。

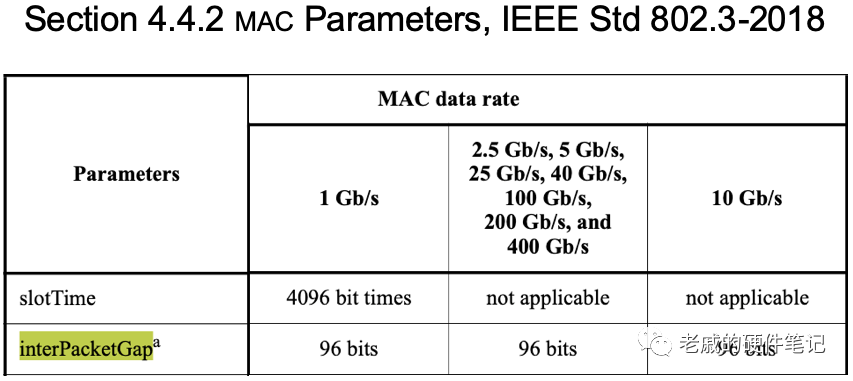

圖<10>

通常而言,交換芯片(點擊進入:可編程交換芯片)的內(nèi)部帶寬會大于接口的帶寬,所以入口(Ingress)側(cè)也不會丟包;在出口(Egress)側(cè),MAC卻必須嚴格按照802.3標(biāo)準(zhǔn)恢復(fù)12字節(jié)的最小幀間隙,這會減緩發(fā)送的速度。可以想象,長時間的飽和流量會導(dǎo)致出口側(cè)的緩存(packet buffer)越積越滿。這種情況持續(xù)發(fā)生,最終會導(dǎo)致出口丟包。

圖<11>

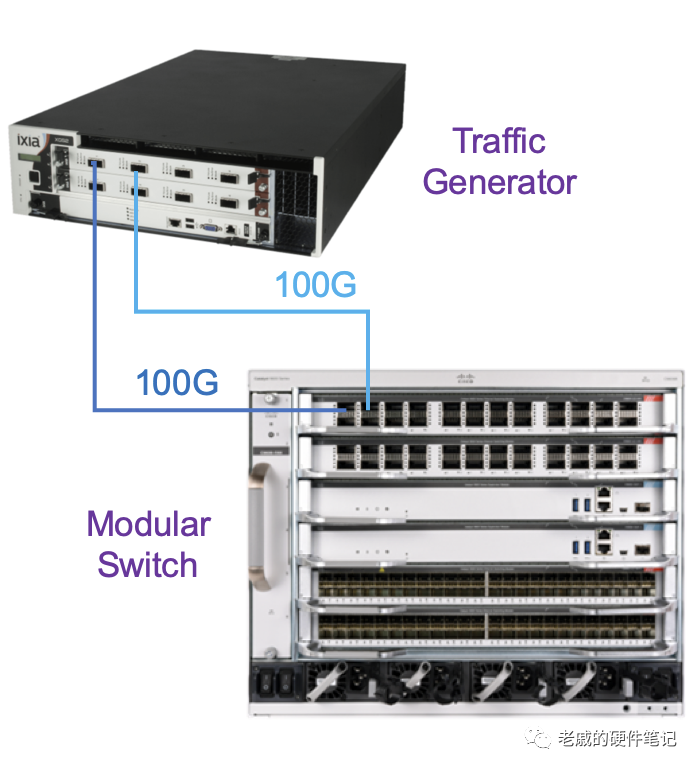

對于交換機產(chǎn)品,端口之間互相打包(轉(zhuǎn)發(fā)包)是最基本的驗證測試項目(圖<11>)。我們期望線速(line rate,utilization 100%,最小IPG)不丟包,然而,經(jīng)常會看到99.9999%就丟包了,丟的數(shù)量不多,短時間甚至看不出來;調(diào)到99.99%變好了;或者下調(diào)發(fā)包儀器(traffic generator)的參考時鐘,比如-10PPM,丟包問題就消失了。當(dāng)然,也有很多交換機按照100%速率轉(zhuǎn)發(fā)包沒有任何問題。究其原因,就是PPM時鐘頻率偏差引起的。

一個有意思的推論就是,雖然PCS能夠補償時鐘的頻率差異,同步以太網(wǎng)(Synchronized Ethernet)時鐘驅(qū)動的時鐘域,至少要包含MAC層,而不僅僅是PCS PHY。(SYNC-E下次聊)

部分以太網(wǎng)交換機的廠商會使用中心頻率正偏25PPM的參考時鐘,使得交換機的本地時鐘處在相對高位,從而避免頻差引起的丟包。但是,交換機之間的背對背連接呢?只要頻率是本地產(chǎn)生的,總是會有高有低,這樣做不能從根本上解決問題。

實際上,對于以太網(wǎng)的應(yīng)用來說,PPM時鐘偏差的影響并不大。不像SDH/SONET這種時分復(fù)用的系統(tǒng),以太網(wǎng)包交換(packet switching)的優(yōu)勢在于帶寬動態(tài)復(fù)用(或者統(tǒng)計復(fù)用,Statistical Multiplexing),企業(yè)級交換機(Enterprise Class Ethernet Switch)使用大緩存(packet buffer)來起到削峰填谷的作用。在MAC層,802.3X流控(flow control)協(xié)議定義了Pause Frame,可以用來通知對端暫停發(fā)送一段時間。更上層,TCP支持出錯重傳,還有QoS等等。

以上的討論都是基于1000Base-X。當(dāng)以太網(wǎng)的端口速率上升到10G以上,8b10b編碼就被64b66b替代了,降低了額外帶寬開銷,前提是PMA層的CDR的技術(shù)提升(僅僅要求66b保證最少一次01轉(zhuǎn)換);PCS層的IDLE碼換了形式繼續(xù)存在;8b10b檢錯變成了AM控制碼攜帶的BIP(Bit Interleaving Parity)。總的來說,形式變了,原理沒有變。而且,不僅是以太網(wǎng),PCIe、SAS、SATA、USB等等也有類似的功能。

小結(jié)一下:物理層(physical layer)的物理編碼子層(PCS - Physical Coding Sublayer)對解決時鐘PPM問題起了關(guān)鍵作用,PCS借助FIFO處理跨時鐘域,通過刪除或插入IDLE碼組,來補償接收數(shù)據(jù)和本地時鐘的有限頻差,這就是彈性緩存(Elastic buffer)。彈性緩存加上包緩存,對突發(fā)(burst)數(shù)據(jù)流量有完美的效果,卻不能解決長時間線速(line rate)流量下的丟包問題。當(dāng)然,通過802.3X流控或者更上層協(xié)議避免長時間線速。

-

以太網(wǎng)

+關(guān)注

關(guān)注

40文章

5579瀏覽量

174669 -

寄存器

+關(guān)注

關(guān)注

31文章

5417瀏覽量

123231 -

fifo

+關(guān)注

關(guān)注

3文章

400瀏覽量

44595 -

時鐘

+關(guān)注

關(guān)注

11文章

1878瀏覽量

132809 -

PPM

+關(guān)注

關(guān)注

0文章

47瀏覽量

17391

發(fā)布評論請先 登錄

以太網(wǎng)應(yīng)用關(guān)鍵技術(shù)及設(shè)計方案集錦

德州儀器(TI)工業(yè)以太網(wǎng)解決方案

設(shè)計坊第三期:靈活的工業(yè)以太網(wǎng)解決方案

基于標(biāo)準(zhǔn)的汽車以太網(wǎng)解決方案的優(yōu)勢有哪些?

工業(yè)以太網(wǎng)方案選擇指南

高速以太網(wǎng)引動超大規(guī)模計算技術(shù)革新,時鐘方案是實現(xiàn)高速以太網(wǎng)的關(guān)鍵

Linux以太網(wǎng)解決方案的介紹

半導(dǎo)體車用以太網(wǎng)解決方案

100G以太網(wǎng)光模塊解決方案

以太網(wǎng)時鐘的PPM頻率偏差的解決方案(上)

數(shù)據(jù)中心市場的關(guān)鍵以太網(wǎng)解決方案

MMWAVEPOEEVM以太網(wǎng)供電解決方案用戶指南

TOSUN 車載以太網(wǎng)仿真測試解決方案

以太網(wǎng)時鐘的PPM頻率偏差的解決方案(下)

以太網(wǎng)時鐘的PPM頻率偏差的解決方案(下)

評論