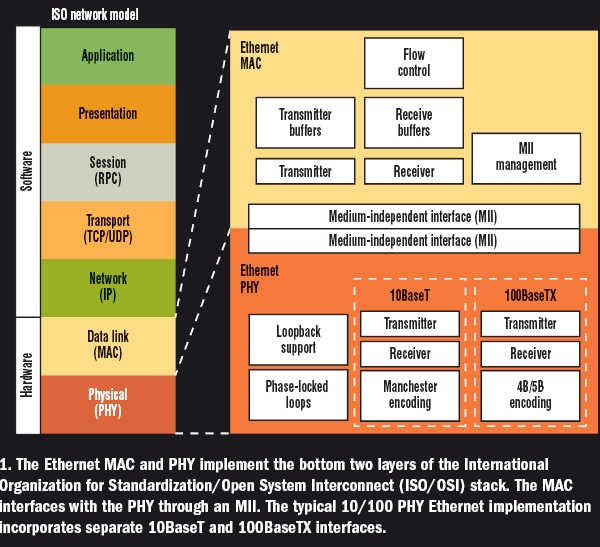

網卡(Network Interface Card,簡稱NIC),也稱網絡適配器,是電腦與局域網相互連接的設備。只要連接到局域網就需要網卡。一個網卡主要包括OSI的最下面兩層,物理層和數據鏈路層。物理層的芯片稱之為PHY,數據鏈路層的芯片稱之為MAC控制器。本文旨在學習以太網基礎MAC和PHY的知識,總結系統框架和物理硬件組成原理,了解各種接口。

PHY & MAC & MII

PHY

PHY 是物理接口收發器,它實現物理層。包括 MII/GMII (介質獨立接口) 子層、PCS (物理編碼子層) 、PMA (物理介質附加) 子層、PMD (物理介質相關) 子層、MDI 子層。定義了數據傳送與接收所需要的電與光信號、線路狀態、時鐘基準、數據編碼和電路等,并向數據鏈路層設備提供標準接口。物理層的芯片稱之為PHY。

MAC

MAC 是 Media Access Control 的縮寫,即媒體訪問控制子層協議。該協議位于 OSI 七層協議中數據鏈路層的下半部分,主要負責控制與連接物理層的物理介質。在發送數據的時候,MAC 協議可以事先判斷是否可以發送數據,如果可以發送將給數據加上一些控制信息,最終將數據以及控制信息以規定的格式發送到物理層;在接收數據的時候,MAC 協議首先判斷輸入的信息是否發生傳輸錯誤,如果沒有錯誤,則去掉控制信息發送至 LLC 層。以太網 MAC 由 IEEE-802.3 以太網標準定義。

MII

MII即媒體獨立接口,也叫介質無關接口。它是IEEE-802.3定義的以太網行業標準。它包括一個數據接口,以及一個MAC和PHY之間的管理接口。數據接口包括分別用于發送器和接收器的兩條獨立信道。每條信道都有自己的數據、時鐘和控制信號。MII數據接口總共需16個信號。管理接口是個雙信號接口:一個是時鐘信號,另一個是數據信號。通過管理接口,上層能監視和控制PHY。 由此可見,MAC 和 PHY,一個是數據鏈路層,一個是物理層;兩者通過 MII 傳送數據。

由此可見,MAC 和 PHY,一個是數據鏈路層,一個是物理層;兩者通過 MII 傳送數據。

系統組成

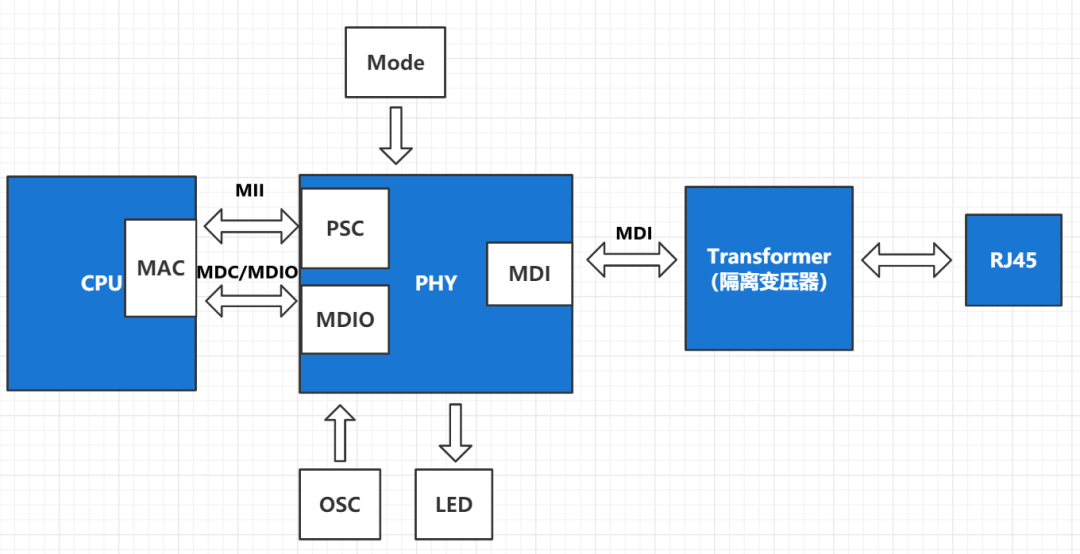

從硬件的角度來分析,以太網的電路接口一般由CPU、MAC(Media Access Control)控制器和物理層接口PHY組成: 對于上述三部分,并不一定都是獨立的芯片,主要有以下幾種情況:

對于上述三部分,并不一定都是獨立的芯片,主要有以下幾種情況:

(1)CPU內部集成了MAC和PHY,難度較高;(2)CPU內部集成MAC,PHY采用獨立芯片(主流方案);(3)CPU不集成MAC和PHY,MAC和PHY采用獨立芯片或者集成芯片(高端采用)。PHY整合了大量模擬硬件,而MAC是典型的全數字器件,芯片面積及模擬/數字混合架構的原因,是將MAC集成進微控制器而將PHY留在片外的原因。更靈活、密度更高的芯片技術已經可以實現MAC和PHY的單芯片整合。以常用的CPU內部集成MAC,PHY采用獨立的芯片方案為例,虛線內表示CPU和MAC集成在一起,PHY芯片通過MII接口與CPU上的MAC互聯。

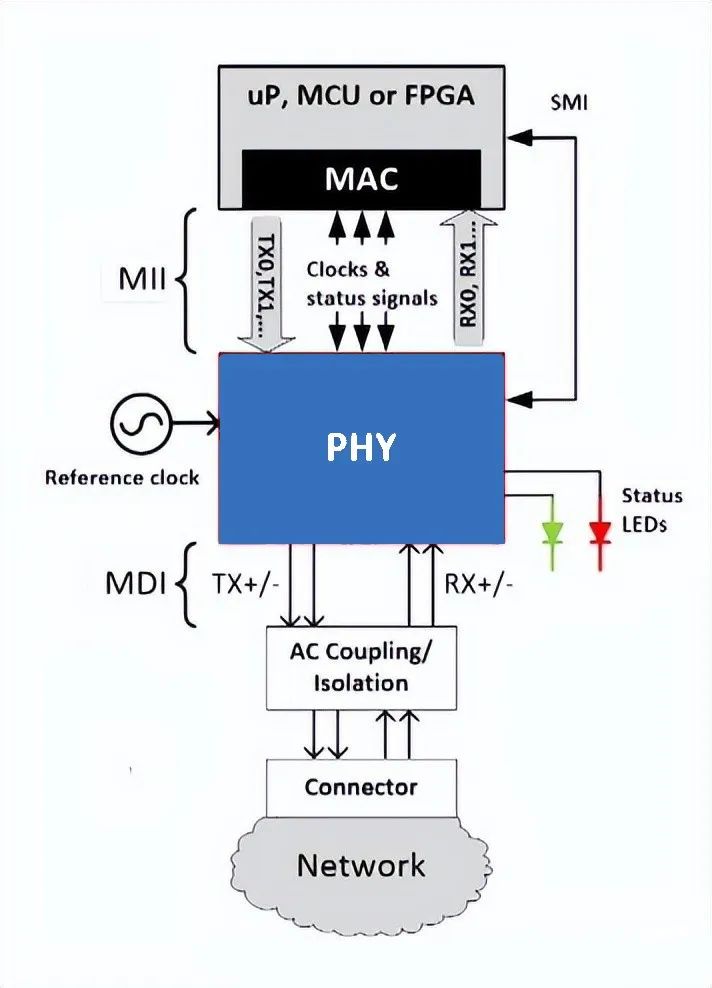

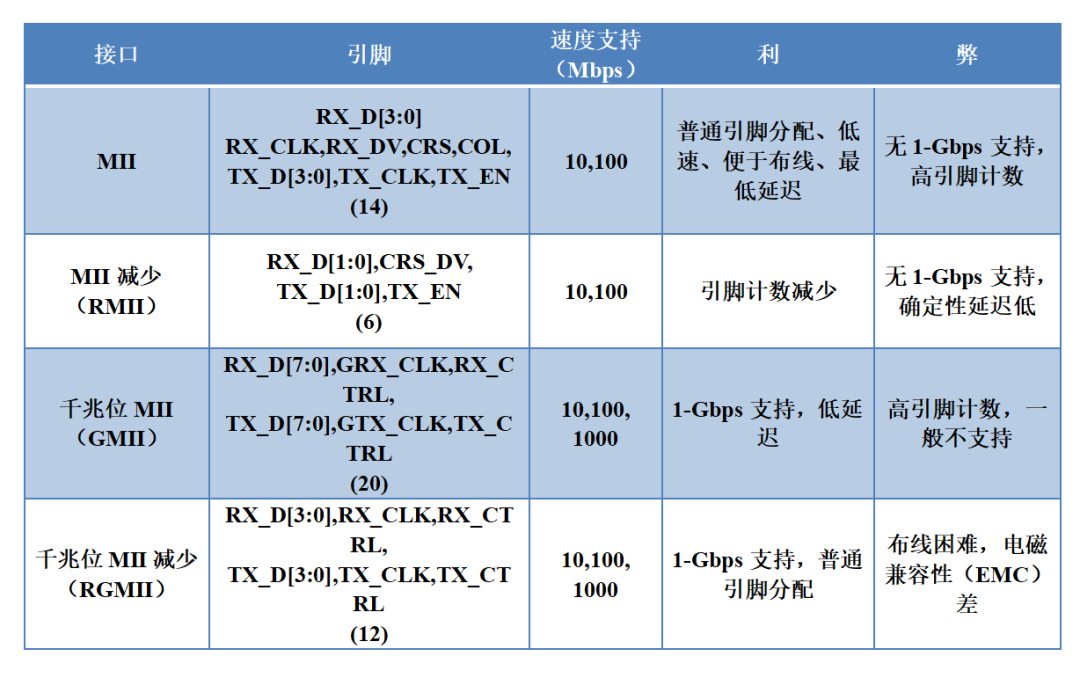

對于這種方案,其硬件方案比獨立的更簡單,PHY與MAC之間有以下兩個重要的硬件接口:(1)MDIO總線接口,主要是完成CPU對于PHY芯片的寄存器配置;(2)MII即媒體獨立接口,也叫介質無關接口。常見的有MII、RMII、GMII、RGMII等。“媒體獨立”表明在不對 MAC 硬件重新設計或替換的情況下,任何類型的 PHY 設備都可以正常工作。MII 數據接口總共需要16個信號,包括:

- transmit data - TXD[3:0]

- transmit strobe - TX_EN

- transmit clock - TX_CLK

- transmit error - TX_ER/TXD4

- receive data - RXD[3:0]

- receive strobe - RX_DV

- receive clock - RX_CLK

- receive error - RX_ER/RXD4

- collision indication - COL

- carrier sense - CRS

一般說來,包括IC 對 PHY 作讀取與寫入用的一組信號:MDC(clock),MDIO(data) 作為 data sampling reference 用的兩組 clock,頻率應為 25MHz(TX_CLK,RX_CLK)各4-bit 的輸出、輸入 Bus(TX[0:3],RX[0:3]);通知對方準備輸入數據的輸出、輸入的啟動信號(TX_EN);輸出、輸入的錯誤通知信號(TX_ER,RX_ER);得到有效輸入數據的通知信號(RX_DV);網絡出現擁塞的 colision 信號(Col)。做為 carrier 回復用的信號(CRS),電位可使用+5V 或+3.3V。MII 以 4bit,即半字節方式雙向傳送數據,時鐘速率 25MHz,其工作速率可達 100Mb/s。MII傳遞了網絡的所有數據和數據的控制,而 MAC對PHY 的工作狀態的確定和對 PHY 的控制則是使用 SMI ( Serial Management Interface) 界面通過讀寫PHY的寄存器來完成的。PHY 里面的部分寄存器是 IEEE 定義的,這樣 PHY 把自己的目前的狀態反映到寄存器里面,MAC 通過 SMI 總線不斷地讀取 PHY 的狀態寄存器以得知目前 PHY 的狀態,例如連接速度,雙工能力等。當然也可以通過 SMI 設置 PHY 的寄存器達到控制的目的,例如流控地打開關閉,自協商模式還是強制模式等。不論是物理連接的 MII 總線和 SMI 總線還是 PHY 的狀態寄存器和控制寄存器都是有 IEEE 的規范的,因此不同公司的 MAC 和 PHY 一樣可以協調工作。當然為了配合不同公司的 PHY 的自己特有的一些功能,驅動需要做相應的修改。

SMI

SMI是MAC內核訪問PHY寄存器接口,它由兩根線組成、雙工,MDC為時鐘,MDIO為雙向數據通信,原理上跟I2C總線很類似,也可以通過總線訪問多個不同的PHY。

MDC/MDIO基本特性:

- 兩線制:MDC(時鐘線)和MDIO(數據線)。

- 時鐘頻率:2.5MHz

- 通信方式:總線制,可同時接入的PHY數量為32個

- 通過SMI接口,MAC芯片主動地輪詢PHY層芯片,獲得狀態信息,并發出命令信息。

后來為了支持千兆網口,也就開始有了千兆網的MII接口,也就是GMII接口。現在比較常用的是RGMII,減小了MAC和PHY之間的引腳數量。數據信號和控制信號混合在一起,并且在工作時鐘的上升沿和下降沿同時采樣,其對應關系如下:10M帶寬對應的是2.5MHz,因為4bit*2.5M=10Mbps100M帶寬對應的是25MHz,因為4bit*25M=100Mbps1000M帶寬對應的是125MHz,4bit*125M=1000Mbps,因為250MHz頻率太高,所以采用雙邊沿采樣技術(會帶來設計復雜度)。

-

以太網

+關注

關注

41文章

5635瀏覽量

175928

發布評論請先 登錄

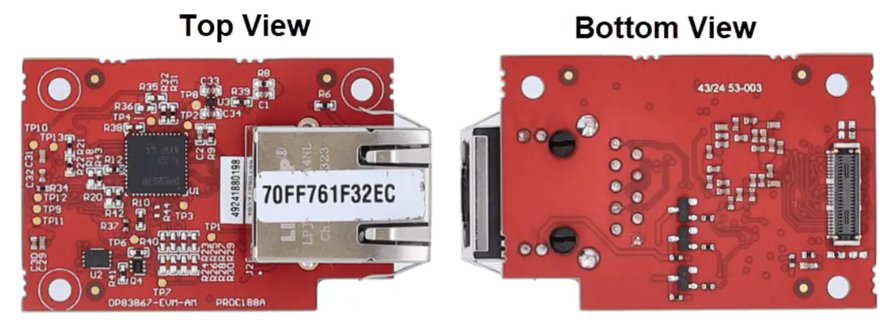

Texas Instruments DP83867-EVM-AM以太網PHY附加板數據手冊

Analog Devices Inc. ADIN1110低功耗10BASE-T1L以太網MAC-PHY數據手冊

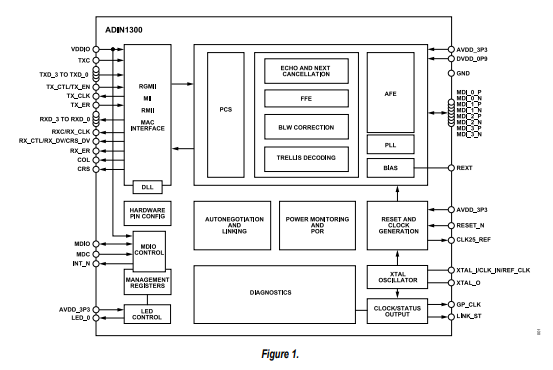

ADIN1300低延遲和低功耗10 Mbps、100 Mbps和1 Gbps以太網PHY技術手冊

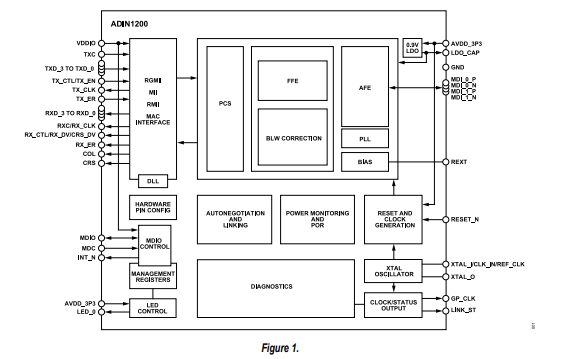

ADIN1200可靠的工業低功耗10 Mbps和100 Mbps以太網PHY技術手冊

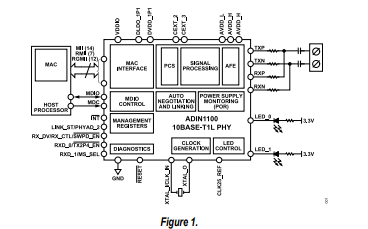

ADIN1100穩健型、低功耗10BASE-T1L工業以太網PHY技術手冊

愛普生SG2520CAA有源晶振賦能車身以太網 PHY

AN4754-將Microchip橋接控制器與外部以太網PHY搭配使用

利用DP83TC812-Q1以太網物理層 (PHY) 的完整汽車以太網系統中的設置和測量

以太網——PHY、MAC、MII與網卡

以太網——PHY、MAC、MII與網卡

評論