在Allegro軟件16.6版本及以上版本,增加了顯示網絡名稱的功能,方便進行布線設計。本文向大家講解,如何將網絡命令進行顯示,具體的操作步驟如下所示:

01第一步

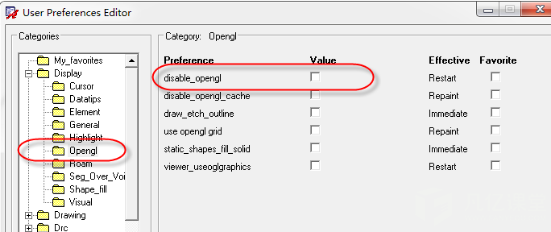

首先將Opengl模式開啟,進入用戶參數設置界面,在Display顯示界面選擇Opengl,右側的第一項復選框不要勾選,如圖1所示;

圖1 開啟Opengl模式示意圖

02第二步

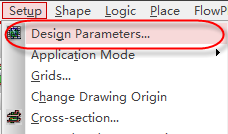

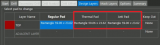

開啟Opengl模式之后,重新啟動PCB軟件,打開設計參數選項,點擊Setup-Design Parameters,如圖2所示;

圖2 打開設計參數設置示意圖

03第三步

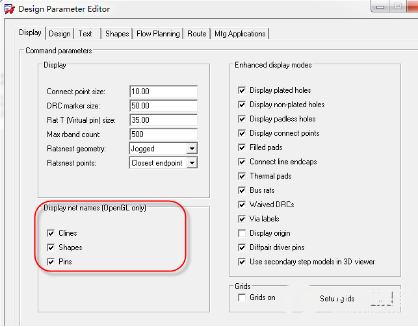

進入設置界面以后,選擇Display選項,在Display net name的選項中,將下面三項的復選框進行勾選,目前只支持在走線、銅皮、焊盤上顯示網絡,如圖3所示;

圖3 顯示網絡命令參數設置示意圖

04第四步

設置完參數之后,回到PCB界面,這樣網絡名稱就會在走線、銅皮、焊盤上進行顯示了。

上述,就是在Allegro軟件中,在走線、銅皮、焊盤上顯示網絡名稱的方法解析。

-

allegro

+關注

關注

42文章

699瀏覽量

146942

發布評論請先 登錄

Allegro Skill布局功能之整體模塊鏡像介紹

PCB單層板LAYOUT,QFN封裝的中間接地焊盤走線出不來怎么辦?

Allegro Skill封裝原點-優化焊盤

Allegro小技巧 | 如何在走線、銅皮、焊盤上顯示網絡名稱

Allegro小技巧 | 如何在走線、銅皮、焊盤上顯示網絡名稱

評論