隨著業界對增加晶體管密度、增加帶寬和降低功耗的需求越來越迫切,許多 IC 設計和封裝團隊都在深入研究如何增加垂直堆疊多個芯片裸片(die)和小芯片(chiplet)的方案。這種被稱為3D-IC 的技術有望實現許多超越傳統單裸片在單平面設計的優勢。其架構可以將多個同質和異質的裸片/小芯片 Chiplet(例如邏輯、內存、模擬和射頻功能)整合到同一設計中。這為系統級芯片(SoC)的集成提供了一個替代方案,支持設計人員希望集成在單一設計中的所有功能,并因此節省在新的制程節點重新設計這些功能而花費的昂貴成本。

3D-IC 有望在網絡、圖形、AI/ML 和高性能計算等領域產生廣泛影響,特別是對于需要超高性能、低功耗器件的應用而言。具體的應用領域包括多核 CPUs、GPUs、數據包緩沖器/路由器、智能手機和 AI/ML 應用。雖然人們對這一新興技術很感興趣,但它仍然處于早期階段。缺乏標準的定義、供應鏈生態系統仍在不斷變化,并且需要解決設計、分析、驗證和測試方面的挑戰。

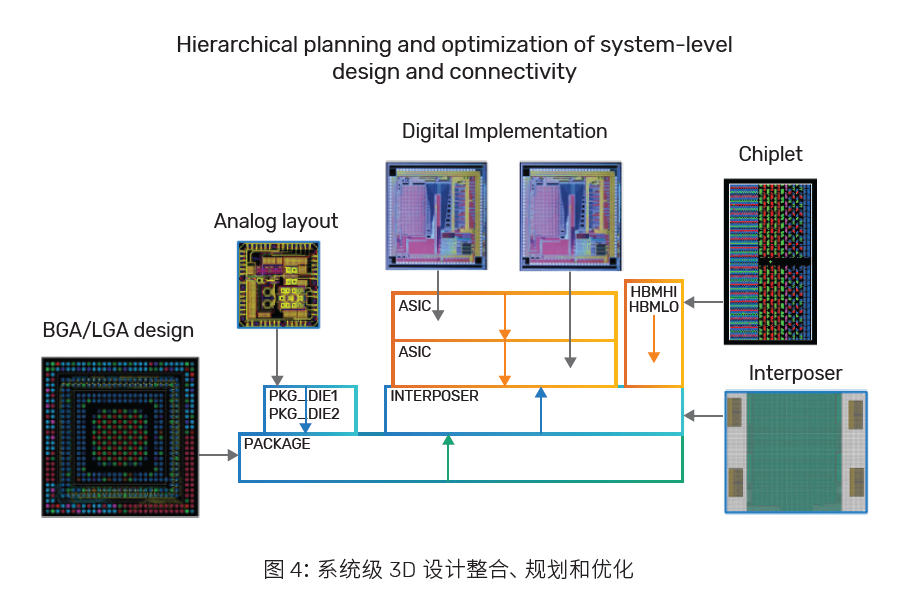

從設計的角度來看,要實現真正的 3D 集成,需要對某些設計工具進行一些加強。尤其在架構分析、熱分析、多裸片間的排置、時序、測試和驗證方面的功能都需要提升。此外,還需要新的系統級功能,如頂層規劃和優化、芯片裸片(die)之間和小芯片(chiplet)之間的信號完整性和 IC/封裝協同設計。其中一些功能現在已經具備,可以在系統設計工具中實現。

最終,設計人員需要能將所需功能全部匯聚到單一集成的設計平臺的解決方案。成功的 3D-IC 設計環境可以在前期階段捕獲頂層設計意圖,通過早期的功耗/發熱估算支持抽象化,并通過實現、提取、時序收斂、測試、分析和封裝之間實現融合。

本白皮書為PDF版本,全長7頁,將簡要介紹3D-IC 技術,并討論設計挑戰、生態系統要求和所需的解決方案。雖然各種類型的多晶粒封裝已經存在多年,但本白皮書的關注重點是 3D 集成和多個堆疊裸片的封裝:

-

引言

-

近距離分析 3D-IC

-

3D-IC 設計挑戰與設計需求

-

數據提取和分析

-

面向測試的設計

-

打造 3D-IC 生態系統

-

結論

點擊文末“閱讀原文”

免費下載白皮書

-

芯片

+關注

關注

459文章

52160瀏覽量

436045 -

IC

+關注

關注

36文章

6093瀏覽量

178381

發布評論請先 登錄

中興通訊發布創新與知識產權白皮書

NVIDIA Blackwell白皮書:NVIDIA Blackwell Architecture Technical Brief

解決電路噪聲難題:《電路噪聲防護與優化設計技術白皮書》工程師必備的全面指南

雷曼光電參編的COB顯示屏調研白皮書發布

微軟發布《GraphRAG實踐應用白皮書》助力開發者

Omdia與華為共發布NPS管理白皮書

紫光同芯參編《智能底盤操作系統白皮書》發布

Samtec 白皮書 | Flyover?電纜系列下篇

免費下載 I 白皮書:3D-IC 設計的挑戰和需求

免費下載 I 白皮書:3D-IC 設計的挑戰和需求

評論