電子發(fā)燒友網(wǎng)報(bào)道(文/李彎彎)近日消息,一組研究人員使用簡(jiǎn)單英語(yǔ)而不是硬件描述語(yǔ)言,成功地設(shè)計(jì)了一款微處理器。ChatGPT等生成式人工智能正在以幾個(gè)月前還不可能的方式幫助人們進(jìn)行研究、學(xué)習(xí)和創(chuàng)造。如今它已經(jīng)開始進(jìn)入硬件設(shè)計(jì)等領(lǐng)域。

紐約大學(xué)坦登電氣與計(jì)算機(jī)工程系以及網(wǎng)絡(luò)安全中心的研究助理教授皮爾斯博士(Dr. Hammond Pearce)介紹說(shuō),他的團(tuán)隊(duì)研究項(xiàng)目Chip Chat的靈感來(lái)源于想要探索現(xiàn)有生成人工智能大語(yǔ)言模型(LLM)在硬件設(shè)計(jì)領(lǐng)域的能力和局限性的愿望。

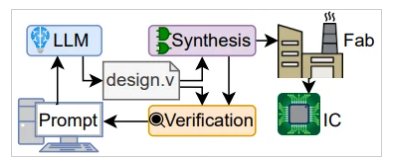

使用LLM創(chuàng)建IC的設(shè)計(jì)流程

“我們很想知道這些模型有多好,”他說(shuō),“很多人認(rèn)為這些模型真的只是玩具,而我不這樣認(rèn)為,現(xiàn)在它們還沒(méi)有無(wú)處不在,不過(guò)未來(lái)它的應(yīng)用肯定會(huì)得到普及,這就是為什么我們做Chip Chat——幾乎像是一個(gè)概念驗(yàn)證演示。”

大語(yǔ)言模型設(shè)計(jì)的IC首次制造出來(lái)

使用基于聊天的人工智能助手可以幫助解決芯片設(shè)計(jì)行業(yè)的一個(gè)巨大挑戰(zhàn):硬件描述語(yǔ)言(HDL)。雖然像Verilog這樣的HDL代碼對(duì)設(shè)計(jì)微處理器至關(guān)重要,但它們需要非常專業(yè)的知識(shí)。

硬件描述語(yǔ)言(HDL),是電子系統(tǒng)硬件行為描述、結(jié)構(gòu)描述、數(shù)據(jù)流描述的語(yǔ)言。利用這種語(yǔ)言,數(shù)字電路系統(tǒng)的設(shè)計(jì)可以從頂層到底層(從抽象到具體)逐層描述自己的設(shè)計(jì)思想,用一系列分層次的模塊來(lái)表示極其復(fù)雜的數(shù)字系統(tǒng)。

然后,利用電子設(shè)計(jì)自動(dòng)化( EDA )工具,逐層進(jìn)行仿真驗(yàn)證,再把其中需要變?yōu)閷?shí)際電路的模塊組合,經(jīng)過(guò)自動(dòng)綜合工具轉(zhuǎn)換到門級(jí)電路網(wǎng)表。接下去,再用專用集成電路 ASIC 或現(xiàn)場(chǎng)可編程門系列 FPGA 自動(dòng)布局布線工具,把網(wǎng)表轉(zhuǎn)換為要實(shí)現(xiàn)的具體電路布線結(jié)構(gòu)。

硬件描述語(yǔ)言(HDL)的發(fā)展至今已有很多年的歷史,并成功地應(yīng)用于設(shè)計(jì)的各個(gè)階段:建模、仿真、驗(yàn)證和綜合等。到20世紀(jì)80年代,已出現(xiàn)了上百種硬件描述語(yǔ)言,對(duì)設(shè)計(jì)自動(dòng)化曾起到了極大的促進(jìn)和推動(dòng)作用。但是,這些語(yǔ)言一般各自面向特定的設(shè)計(jì)領(lǐng)域和層次,而且眾多的語(yǔ)言使用戶無(wú)所適從。因此,急需一種面向設(shè)計(jì)的多領(lǐng)域、多層次并得到普遍認(rèn)同的標(biāo)準(zhǔn)硬件描述語(yǔ)言。20世紀(jì)80年代后期,VHDL和Verilog HDL語(yǔ)言適應(yīng)了這種趨勢(shì)的要求,先后成為IEEE 標(biāo)準(zhǔn)。

皮爾斯博士說(shuō):“硬件描述語(yǔ)言面臨的最大挑戰(zhàn)是,沒(méi)有多少人知道如何編寫它們。成為這方面的專家很難,這意味著我們?nèi)匀挥凶詈玫?a target="_blank">工程師用這些語(yǔ)言做瑣碎的事情,因?yàn)闆](méi)有那么多工程師可以做這些事情。”

在他看來(lái),人工智能可以加速工程師的產(chǎn)出,這樣人工智能就可以快速完成簡(jiǎn)單的事情,工程師也可以把腦力集中在更難的事情上。

通過(guò)使硬件定義更容易生成,該團(tuán)隊(duì)相信他們可以使IC設(shè)計(jì)更容易訪問(wèn),并使HDL專家能夠?qū)W⒂诟匾娜蝿?wù)。根據(jù)該團(tuán)隊(duì)的說(shuō)法,通過(guò)基于聊天的生成人工智能,工程師可以用簡(jiǎn)單的英語(yǔ)而不是HDL設(shè)計(jì)微處理器。

通過(guò)Chip Chat,該團(tuán)隊(duì)成功地設(shè)計(jì)了一個(gè)基于8位累加器的微處理器,其功能與可比較的PIC產(chǎn)品相同。然后將該芯片發(fā)送到Skywater 130nm穿梭機(jī)上進(jìn)行制造。該團(tuán)隊(duì)聲稱,這項(xiàng)研究標(biāo)志著LLM設(shè)計(jì)的IC首次真正制造出來(lái)。

ChatGPT等生成式AI在芯片設(shè)計(jì)領(lǐng)域的探索

事實(shí)上,在ChatGPT出現(xiàn)之后,就有不少人開始探討它在芯片設(shè)計(jì)領(lǐng)域的潛在應(yīng)用。芯片設(shè)計(jì)是一項(xiàng)高度技術(shù)密集的工作,需要精通電子、材料、物理等多個(gè)領(lǐng)域的專業(yè)知識(shí)。

通常,它需要一些專業(yè)的EDA(Electronic Design Automation)工具,例如邏輯綜合、布局與布線、時(shí)序分析等。但是,這些EDA工具需要用戶有豐富的專業(yè)知識(shí)和豐富的設(shè)計(jì)經(jīng)驗(yàn),且需要用戶手動(dòng)輸入復(fù)雜的指令和參數(shù),這使得芯片設(shè)計(jì)成為一個(gè)復(fù)雜而費(fèi)時(shí)的過(guò)程。

業(yè)內(nèi)人士認(rèn)為,ChatGPT的自然語(yǔ)言處理技術(shù)可以為芯片設(shè)計(jì)提供一種全新的方式。ChatGPT可以通過(guò)學(xué)習(xí)已有的芯片設(shè)計(jì)數(shù)據(jù)和文檔,自動(dòng)生成芯片設(shè)計(jì)的指令和參數(shù),并提供對(duì)芯片設(shè)計(jì)問(wèn)題的解決方案的自然語(yǔ)言描述。這種方式可以減少芯片設(shè)計(jì)過(guò)程中的人為錯(cuò)誤,提高芯片設(shè)計(jì)的效率和準(zhǔn)確性。

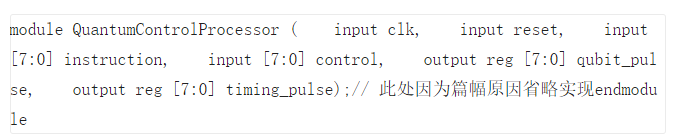

ChatGPT的代碼生成能力也能夠極大的加速芯片設(shè)計(jì)的速度。有這樣一個(gè)案例,量子控制處理器是量子計(jì)算機(jī)的核心控制部分,有人用ChatGPT合成了一個(gè)量子控制處理器的代碼,如下:

據(jù)介紹,雖然這段代碼有些許小問(wèn)題,比如ChatGPT并不能很好地實(shí)現(xiàn)時(shí)序的控制,會(huì)出現(xiàn)浪費(fèi)時(shí)鐘周期的現(xiàn)象,但是這段代碼可正確編譯,并且是一個(gè)有效的設(shè)計(jì)方案。

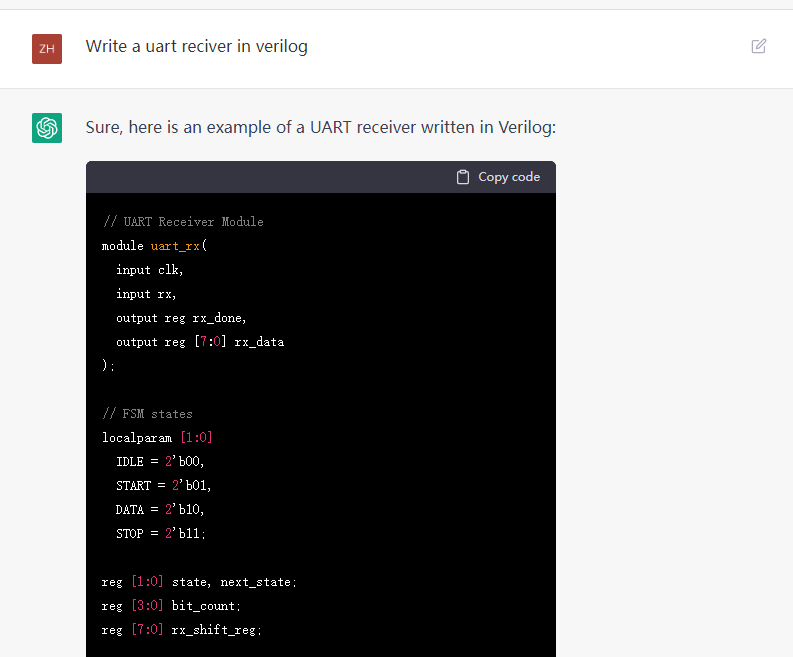

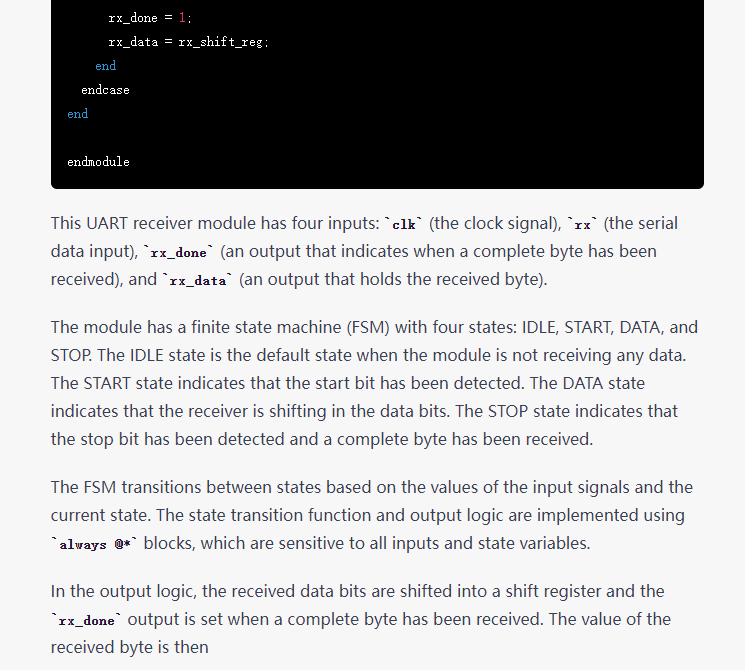

另外此前也有人好奇ChatGPT能不能寫出一段Verilog代碼,于是就做了嘗試。發(fā)現(xiàn),它不僅能寫出一段代碼,甚至還能加上一段解釋,這位讓ChatGPT寫Verilog代碼的業(yè)內(nèi)人士說(shuō),完整代碼很長(zhǎng),自己也沒(méi)有驗(yàn)證,不過(guò)大概看下來(lái),功能基本都有。

對(duì)于過(guò)于復(fù)雜的功能,比如以太網(wǎng)協(xié)議棧,當(dāng)?shù)谝淮巫屗鼘懙臅r(shí)候,它提示太難寫不出來(lái),但是把對(duì)話復(fù)位后,再讓它寫,它就能寫一個(gè)大概的module,里面只有寫接口,后面又復(fù)位對(duì)話后再重新讓它寫,寫出來(lái)的程序就更多了。這說(shuō)明它的學(xué)習(xí)能力一直在增長(zhǎng)。

雖然ChatGPT在芯片設(shè)計(jì)中有它的優(yōu)勢(shì),同時(shí)也存在一些限制,比如,ChatGPT需要大量的芯片設(shè)計(jì)數(shù)據(jù)和文檔作為訓(xùn)練數(shù)據(jù)。這些數(shù)據(jù)需要經(jīng)過(guò)標(biāo)注和清理,以保證ChatGPT能夠準(zhǔn)確地學(xué)習(xí)芯片設(shè)計(jì)的知識(shí)和規(guī)律。此外,芯片設(shè)計(jì)數(shù)據(jù)的數(shù)量和質(zhì)量直接影響ChatGPT在芯片設(shè)計(jì)中的準(zhǔn)確性和效率。

再比如,芯片設(shè)計(jì)中的一些細(xì)節(jié)問(wèn)題,例如噪聲、功耗等方面的考慮,可能需要ChatGPT結(jié)合EDA工具進(jìn)行深度優(yōu)化。在這種情況下,ChatGPT將需要學(xué)習(xí)和理解EDA工具的功能和限制,以生成更加準(zhǔn)確和可行的芯片設(shè)計(jì)指令和參數(shù)。

也因此,ChatGPT在芯片設(shè)計(jì)中的應(yīng)用,并不能完全取代人類工程師的工作。皮爾斯博士表示,這些人工智能總是會(huì)有無(wú)法完成的工具和工作。它們生產(chǎn)的產(chǎn)品總是會(huì)有弱點(diǎn)。

小結(jié)

在ChatGPT出現(xiàn)之后,基于其強(qiáng)大的文字、代碼生成能力等,人們開始探索它在各個(gè)領(lǐng)域的應(yīng)用,包括在芯片設(shè)計(jì)方面。也有工程師利用它寫Verilog代碼,基本功能都能實(shí)現(xiàn)。如今紐約大學(xué)利用更是利用它設(shè)計(jì)并制造出了一顆微處理器,這樣ChatGPT在芯片設(shè)計(jì)上的應(yīng)用更進(jìn)一步,而且ChatGPT的存在也能夠真正地解決芯片設(shè)計(jì)中一直難以解決的挑戰(zhàn)。

-

微處理器

+關(guān)注

關(guān)注

11文章

2371瀏覽量

83863 -

ChatGPT

+關(guān)注

關(guān)注

29文章

1588瀏覽量

8807

發(fā)布評(píng)論請(qǐng)先 登錄

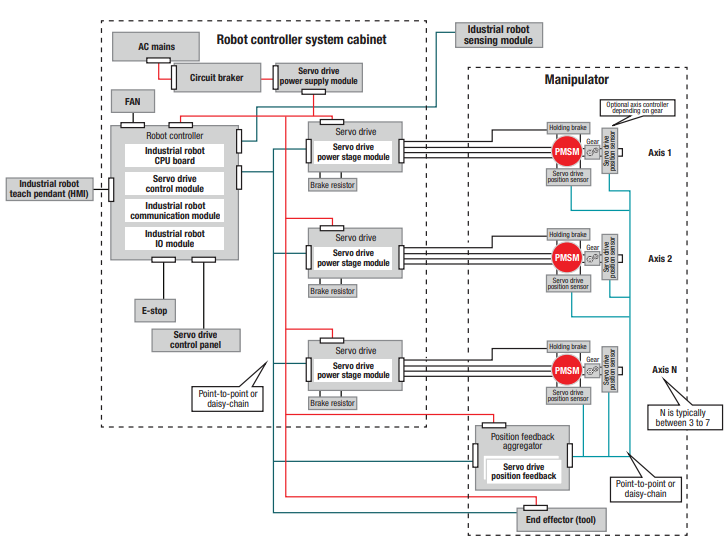

工業(yè)機(jī)器人設(shè)計(jì)工程師必備指南免費(fèi)下載

羅徹斯特電子對(duì)微處理器的長(zhǎng)期支持

MPU微處理器的工作原理

微處理器芯片正常工作應(yīng)具備哪些基本條件?

微處理機(jī)和微處理器的區(qū)別

微處理器執(zhí)行指令的基本過(guò)程

微處理器的指令集有哪些

硬件工程師VS軟件工程師|硬件工程師看到這都淚目了!#硬件設(shè)計(jì) #硬件工程師 #電子工程師 #軟件工程師

FPGA算法工程師、邏輯工程師、原型驗(yàn)證工程師有什么區(qū)別?

簡(jiǎn)述微處理器的發(fā)展歷史

微處理器如何控制計(jì)算機(jī)系統(tǒng)

影響微處理器性能的因素

微處理器的主要性能指標(biāo)

微處理器的指令集架構(gòu)介紹

ChatGPT設(shè)計(jì)并制造出首顆微處理器!芯片設(shè)計(jì)工程師工作危險(xiǎn)了?

ChatGPT設(shè)計(jì)并制造出首顆微處理器!芯片設(shè)計(jì)工程師工作危險(xiǎn)了?

評(píng)論