前面幾篇文章已經詳細介紹了FPGA時序約束基礎知識以及常用的時序約束命令,相信大家已經基本掌握了時序約束的方法。

今天介紹一下,如何在Vivado中添加時序約束,Vivado添加約束的方法有3種:xdc文件、時序約束向導(Constraints Wizard)、時序約束編輯器(Edit Timing Constraints )

一、XDC文件

使用VIvado的“Source文件管理器”直接創建新的xdc文件或者添加已有的xdc文件。

具體步驟如下:

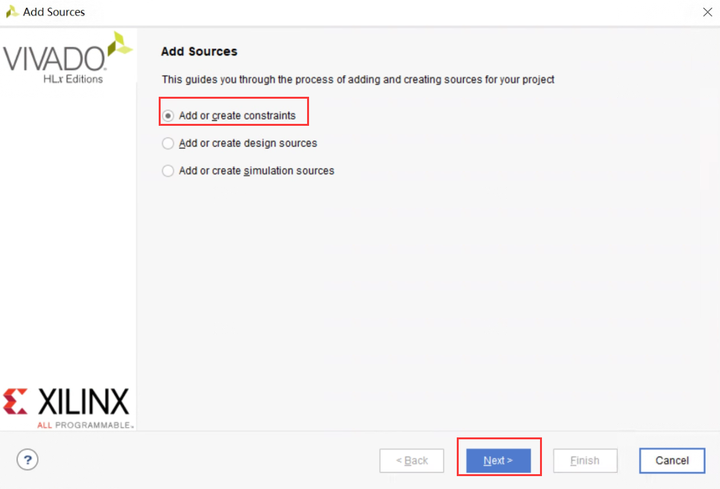

第一步:點擊“+”

第二步:選擇“Add or create constraints”,點擊“next”

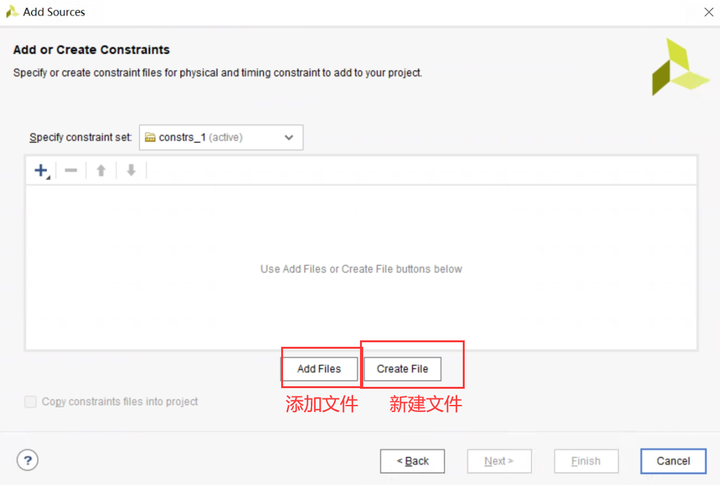

第三步:如果是添加文件則點擊“Add Files”,如果是新建文件,則點擊“Create File”

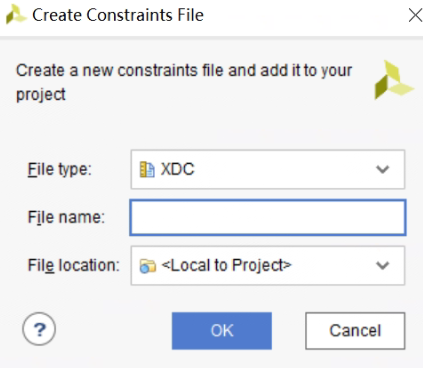

第四步:如果是新建文件,則輸入文件名,點擊“OK”,再點擊“Finish”即可

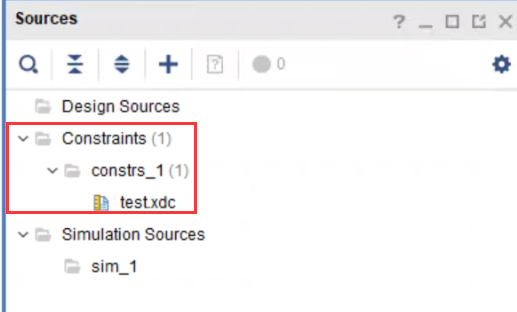

這樣就可以,在source界面中的“Constraints”中看到新建的文件。

雙擊打開新建的xdc文件,寫入約束語句即可。

創建XDC文件的方式很靈活,但在添加約束時需要謹慎一些,因為一些錯誤的約束可能會導致電路出錯或性能下降。

二、時序約束向導(Constraints Wizard)

時序約束向導是Vivado提供的一個交互式添加約束工具。

可以幫助用戶通過簡單的設置界面來自動生成xdc文件中的TIMING約束。

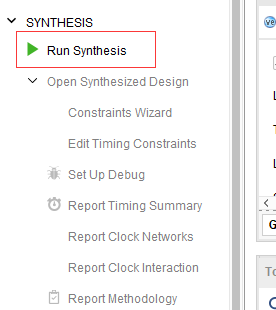

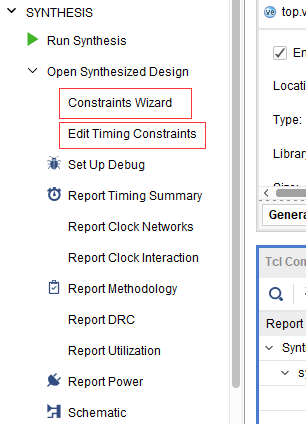

第一步:將HDL代碼綜合

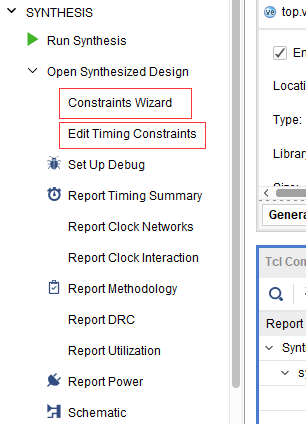

?第二步:點擊VIvado左邊導航欄的“Synthesis”的“Constraints Wizard”。

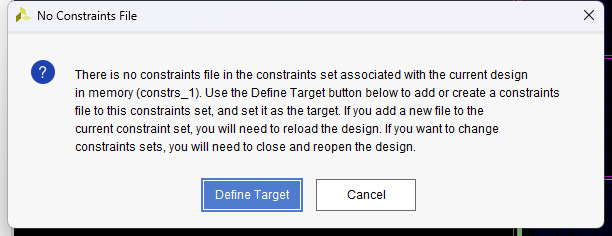

?第三步:如果未創建xdc文件,vivado會提示新建新的xdc文件。

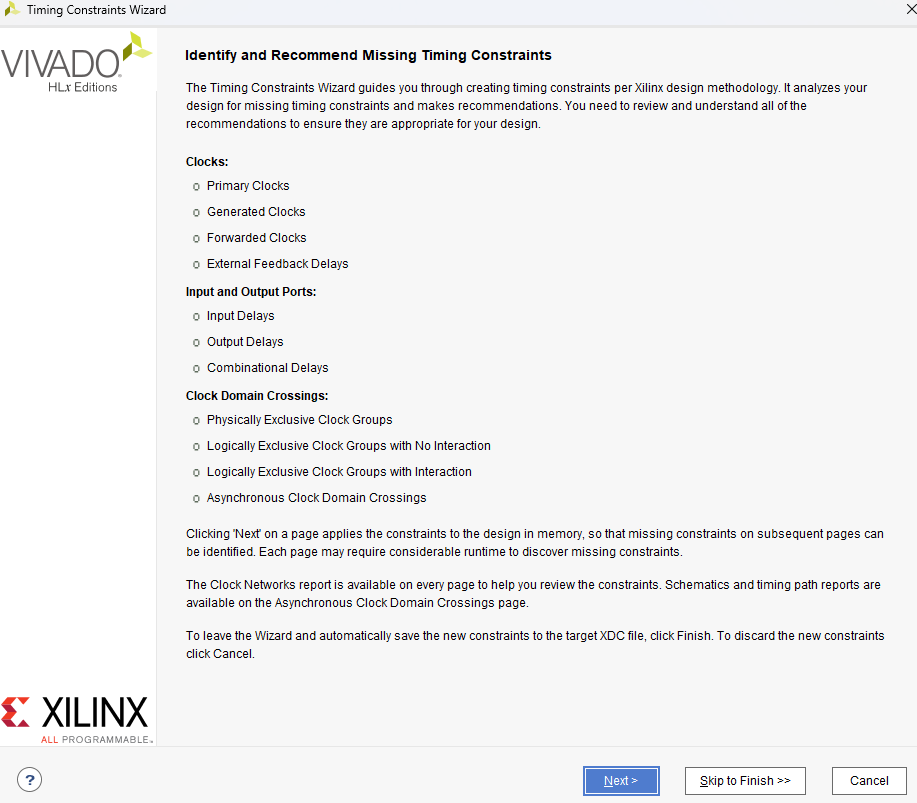

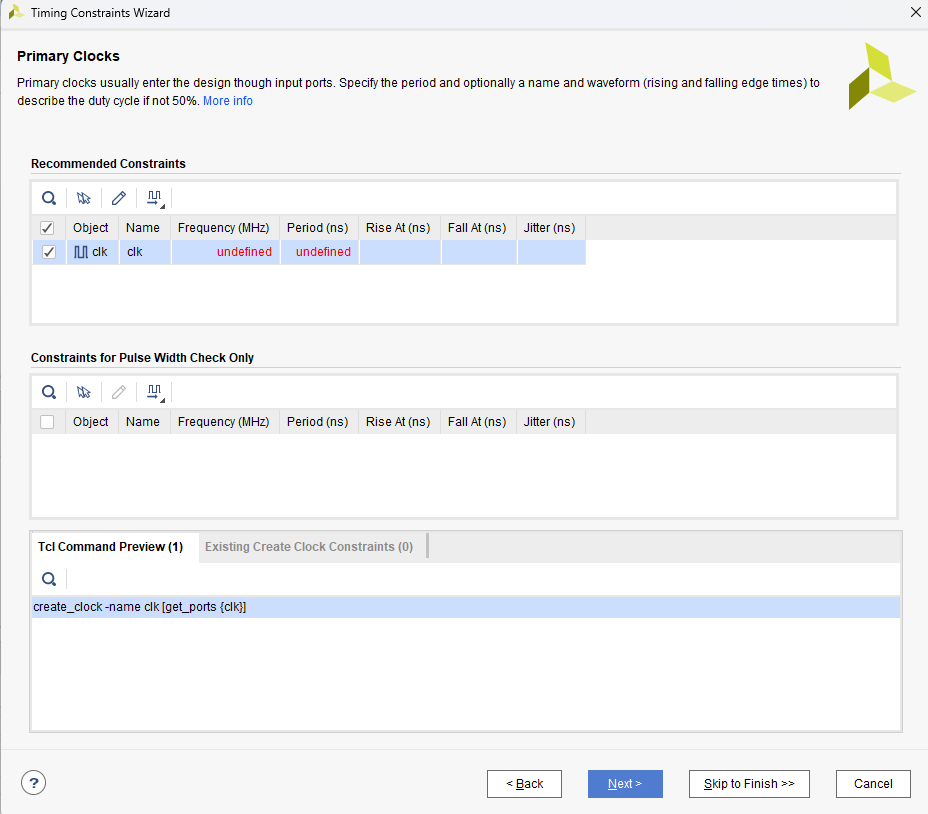

?第四步:進入時序約束向導界面

時序約束向導是按照主時鐘約束、衍生時鐘約束、輸入延遲約束、輸出延遲約束、時序例外約束、異步時鐘約束等的順序來依次創建時鐘約束的。

?點擊下一步,這里只演示填入主時鐘,輸入時鐘周期,點擊“skip to finish”。

?

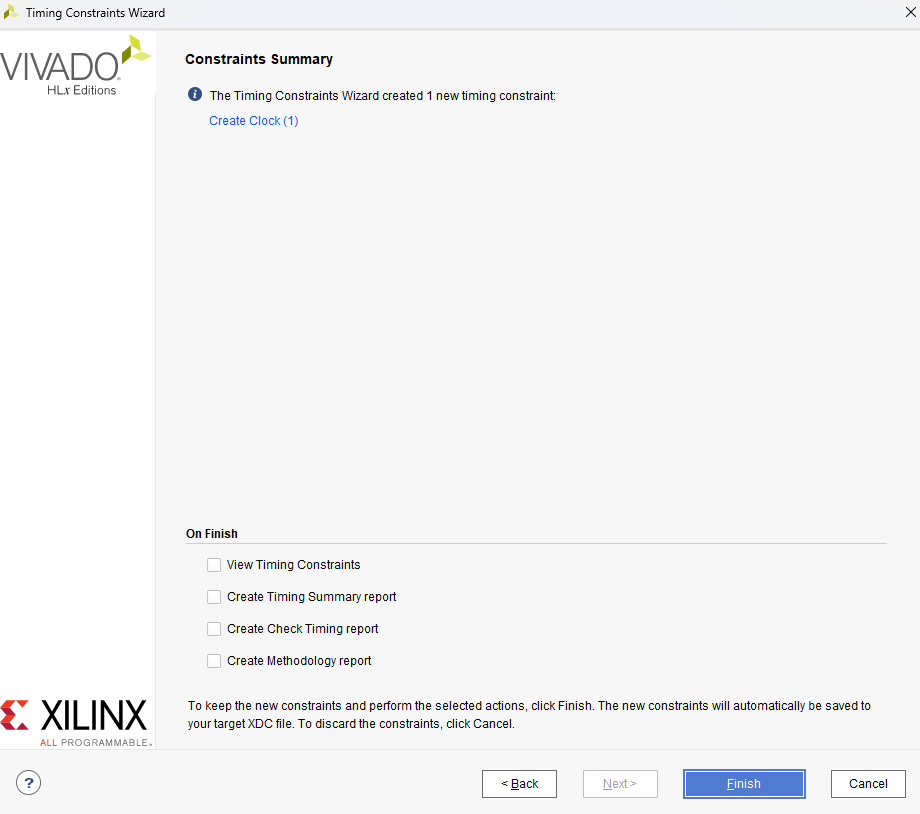

?最后點擊finish,生成約束會自動保存到xdc文件中。

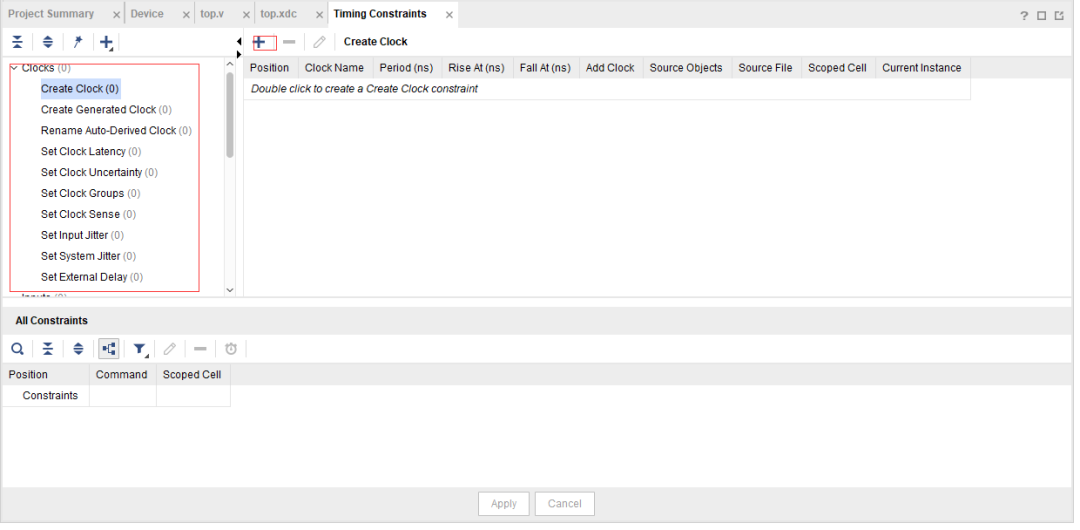

三、時序約束編輯器(Edit Timing Constraints )

時序約束編輯器是Vivado中提供的可視化界面,用于修改編輯在xdc文件的時序約束,用戶通過這個界面可以添加/刪除約束、調整約束優先級及修改約束屬性。

第一步:將HDL代碼綜合完后,點擊VIvado左邊導航欄的“Synthesis”的“Edit Timing Constraints”。

?

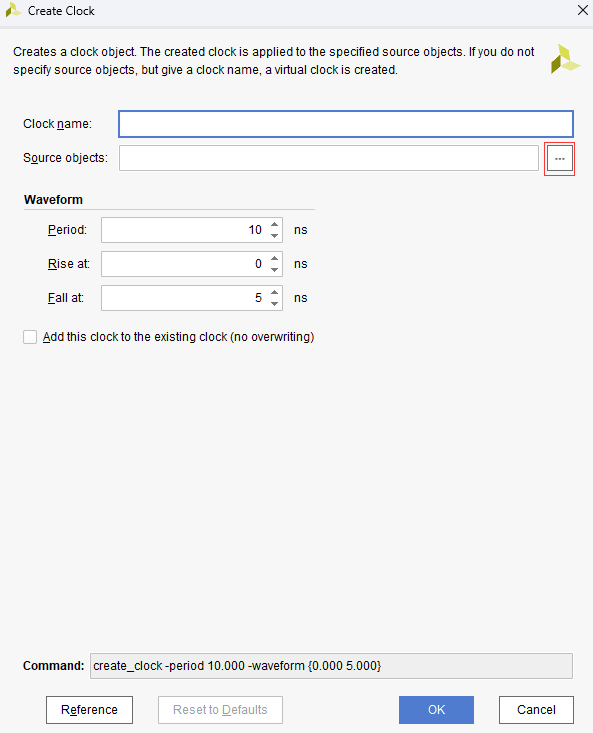

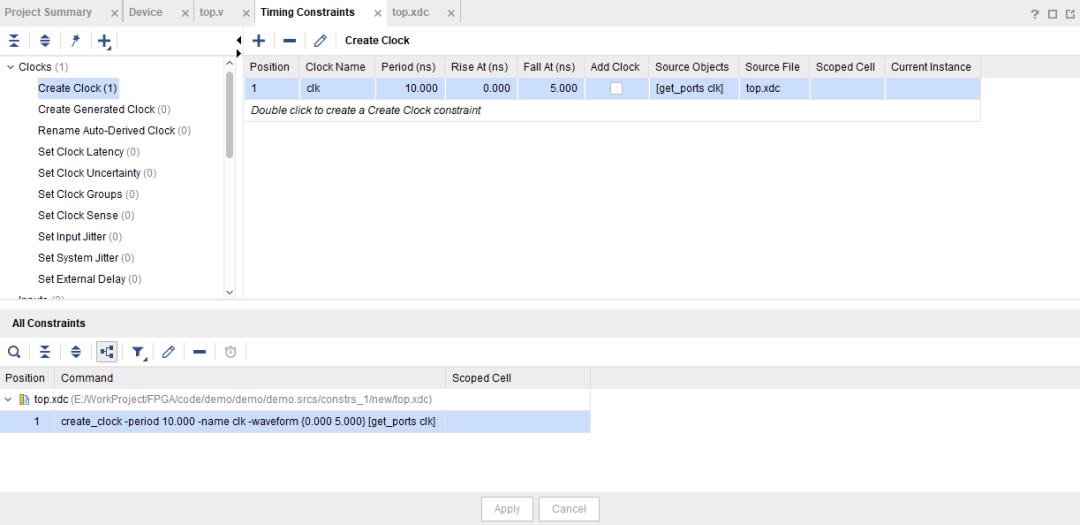

第二步:彈出編輯界面,如下圖所示,先在左側選擇時序約束類型,再點擊右側窗口的“+”

號,開始添加時序約束命令。

?

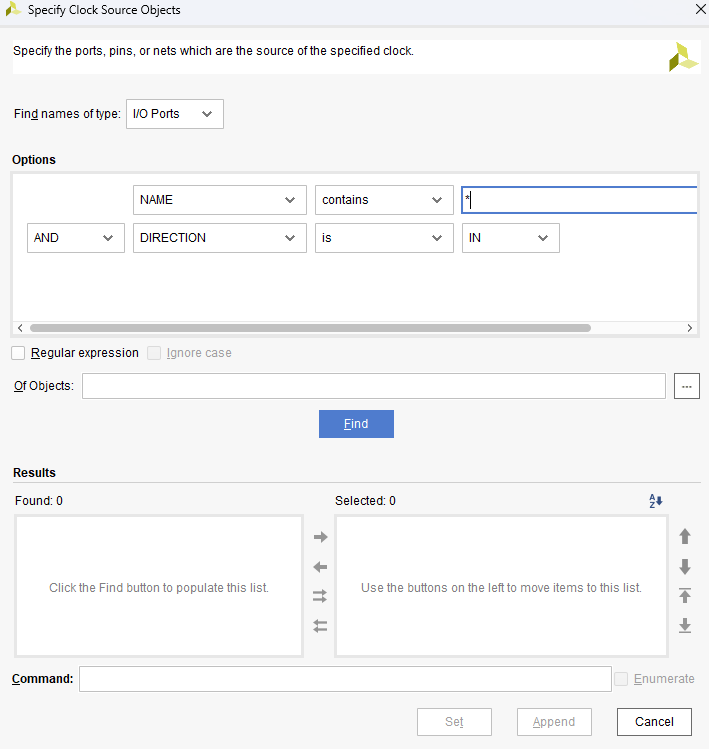

第三步,點擊紅框中“...”,打開搜索端口界面,再點擊“find”按鈕,自動彈出搜索到端口號。

?

?

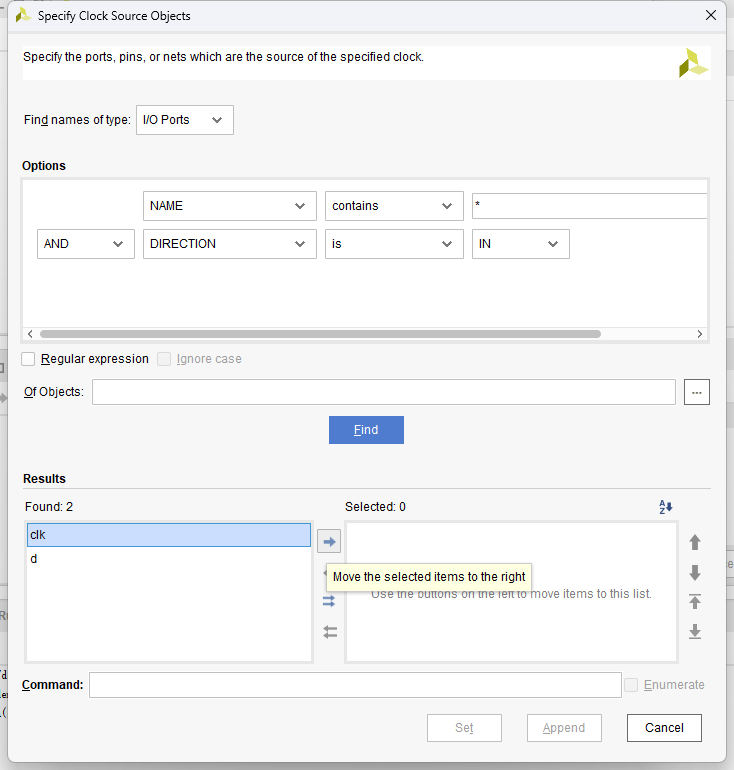

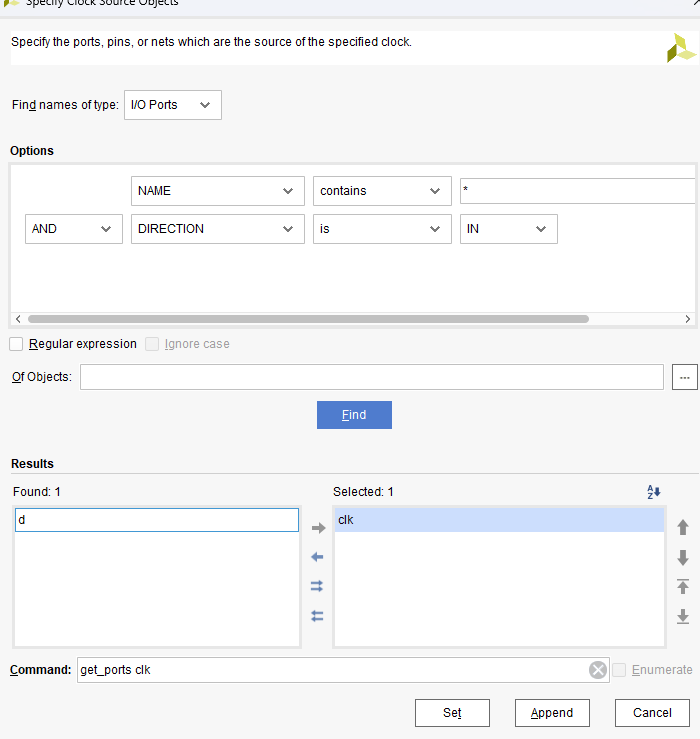

第四步:選中需要添加約束的端口,如“clk”,點擊右側箭頭,移動到“選中窗口”,再點擊“set”按鈕。

?

?

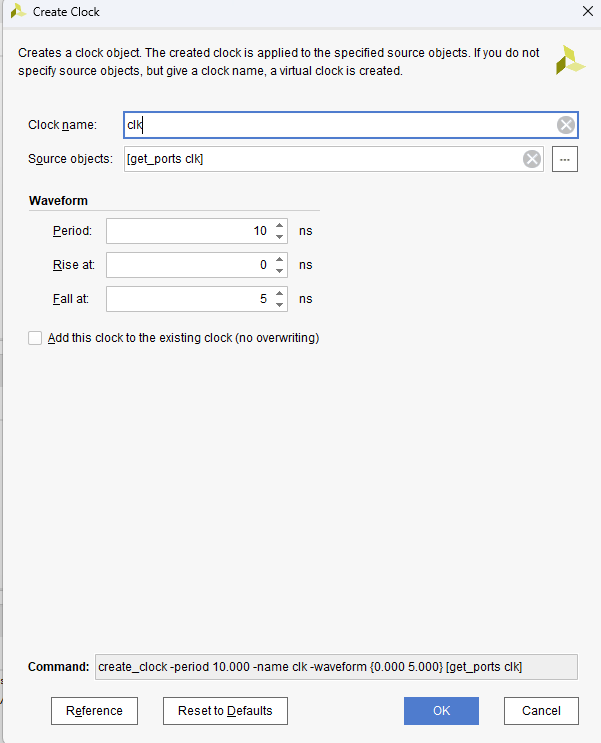

第五步:輸入約束端口名,并設置時鐘周期和占空比,點擊“OK”。

?

第六步:按“ctrl+s”快捷鍵保存,最下方的預覽窗口會顯示設置的時鐘約束,而且會自動保存到xdc約束文件中。

?

與直接xdc文件相比,時序約束編輯器提供了時序約束詳細的分類和說明,更容易理解和使用。

四、總結

本文分享了Vivado中常用的添加時序約束的方法,大家可以按照自己的習慣和喜好選擇方式即可。

-

FPGA

+關注

關注

1643文章

21954瀏覽量

613996 -

HDL

+關注

關注

8文章

330瀏覽量

47815 -

編輯器

+關注

關注

1文章

816瀏覽量

31756 -

時序約束

+關注

關注

1文章

118瀏覽量

13621 -

Vivado

+關注

關注

19文章

828瀏覽量

68205

發布評論請先 登錄

VIVADO時序約束及STA基礎

FPGA主時鐘約束詳解 Vivado添加時序約束方法

FPGA開發中如何對整個設計添加時序約束

Vivado中的靜態時序分析工具Timing Report的使用與規范

如何在Vivado中添加時序約束

如何在Vivado中添加時序約束

評論