對(duì)于要求相位以及占空比嚴(yán)格的小數(shù)分頻,建議采用模擬電路實(shí)現(xiàn)。 而使用數(shù)字電路實(shí)現(xiàn)只能保證盡量均勻,在長(zhǎng)時(shí)間內(nèi)進(jìn)行分頻 。

在討論小數(shù)分頻之前,先問一個(gè)問題:設(shè)計(jì)中是否真的需要50%占空比的時(shí)鐘?

在回答這個(gè)問題之前,可以先回顧之前我們寫過的RTL設(shè)計(jì),可以看一下之前的RTL設(shè)計(jì)代碼中always塊是不是大部分都是@(posedge clk)。

對(duì)于絕大多數(shù)的觸發(fā)器,其實(shí)只需要用到時(shí)鐘的上升沿觸發(fā),很少用到下降沿。在這種情況下,只要上升沿和時(shí)鐘頻率有關(guān)系,什么時(shí)候來下降沿不重要! 所以50%的占空比不是必須的 。

因此在小數(shù)分頻器中我們關(guān)注的是如何得到一個(gè)盡量均勻的分頻信號(hào),而不是得到一個(gè)絕對(duì)50%占空比的分頻信號(hào)。

下面以4.5倍的分頻(非50%占空比)作為例子介紹,即每9個(gè)參考時(shí)鐘包含2個(gè)對(duì)稱脈沖。下面是4.5分頻的設(shè)計(jì)步驟。

①:使用復(fù)位值為000000001的9位移位寄存器,可以在每個(gè)時(shí)鐘上升沿使移位寄存器循環(huán)左移一位。

②:要產(chǎn)生第一個(gè)脈沖,必須使在半周期時(shí)移動(dòng)第一位并將第一位與第二位進(jìn)行或操作。

③:要產(chǎn)生第二個(gè)脈沖,第5位和第6位必須在半周期時(shí)移動(dòng)并與原始第6位進(jìn)行或操作。

注意:所有這些移位都是用來保證輸出波形不含毛刺的必要條件。

上面產(chǎn)生的時(shí)鐘占空比為40%,并且輸出的時(shí)鐘完全不含毛刺。

always@(posedge clk or negedge rst_n)

if(!rst_n)

cnt[9:1] <= 9'b000000001;

else

cnt[9:1] <= cnt[9:1] < < 1;

always@(negedge clk or negedge rst_n)

if(!rst_n)begin

count1 <= 1'b0;

count5 <= 1'b0;

count6 <= 1'b0;

end

else begin

count1 <= cnt[1];

count5 <= cnt[5];

count6 <= cnt[6];

end

assign clkout = (cnt[6] | count5 | count6) |

(cnt[0] | cnt[1] |count1);

-

模擬電路

+關(guān)注

關(guān)注

125文章

1588瀏覽量

103643 -

分頻器

+關(guān)注

關(guān)注

43文章

490瀏覽量

50791 -

移位寄存器

+關(guān)注

關(guān)注

3文章

287瀏覽量

22629 -

RTL

+關(guān)注

關(guān)注

1文章

388瀏覽量

60625 -

觸發(fā)器

+關(guān)注

關(guān)注

14文章

2032瀏覽量

61848

發(fā)布評(píng)論請(qǐng)先 登錄

基于FPGA的小數(shù)分頻器如何去實(shí)現(xiàn)?

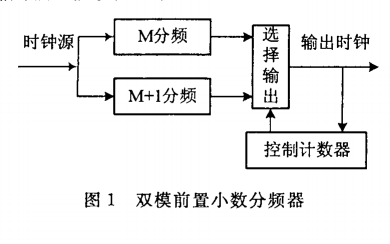

怎么把小數(shù)分頻控制字與整數(shù)分頻控制字結(jié)合起來去控制可編程分頻器?

FPGA實(shí)現(xiàn)小數(shù)分頻器

△∑小數(shù)頻率合成器中的小數(shù)分頻器設(shè)計(jì)

分頻器的作用是什么 半整數(shù)分頻器原理圖分析

如何使用FPGA進(jìn)行任意小數(shù)分頻器的設(shè)計(jì)

奇數(shù)分頻器的介紹和實(shí)現(xiàn)

偶數(shù)分頻器的設(shè)計(jì)

偶數(shù)分頻、奇數(shù)分頻、半整數(shù)分頻和小數(shù)分頻詳解

FPGA學(xué)習(xí)-分頻器設(shè)計(jì)

分頻器之小數(shù)分頻設(shè)計(jì)

分頻器之小數(shù)分頻設(shè)計(jì)

評(píng)論