等離子蝕刻可能是半導體制造中最重要的工藝,也可能是僅次于光刻的所有晶圓廠操作中最復雜的工藝。將近一半的晶圓廠步驟依靠等離子體(一種高能電離氣體)來完成工作。

盡管晶體管和存儲單元不斷縮小,工程師們仍在繼續提供可靠的蝕刻工藝。

“為了可持續地制造具有納米級精度和正確成本結構的芯片,晶圓廠設備制造商需要突破等離子體物理學、材料工程和數據科學的界限,以提供所需的設備解決方案,”Lam Research公司的蝕刻產品組營銷副總裁 Thomas Bondur 說。這一點在等離子蝕刻中表現得最為明顯,等離子蝕刻與光刻技術攜手合作,在晶圓上創建精確、可重復的特征。

本文談及了 3D NAND、DRAM、納米片 FET 和互連中的關鍵蝕刻步驟,并展望了 2D 設備和低預算后端處理。該行業還在尋求更具可持續性的蝕刻化學品,以減少其工廠的等效而養護毯排放量。

對于許多工具制造商來說,工藝建模在蝕刻工藝開發中起著舉足輕重的作用。目標是縮短上市時間,同時降低晶圓和掩模成本。

“對一些最棘手的步驟進行蝕刻工藝優化可能需要一年或更長時間才能完成,”Lam Research 高級營銷總監 Barrett Finch 說。“我們最近在三周內完成了一些過程模擬工作,如果使用典型的基于硅的測試和開發,預計需要三個月的時間。”

光是設備制造商的光罩和晶圓成本,就可能達到數十萬甚至數百萬美元。

蝕刻基礎

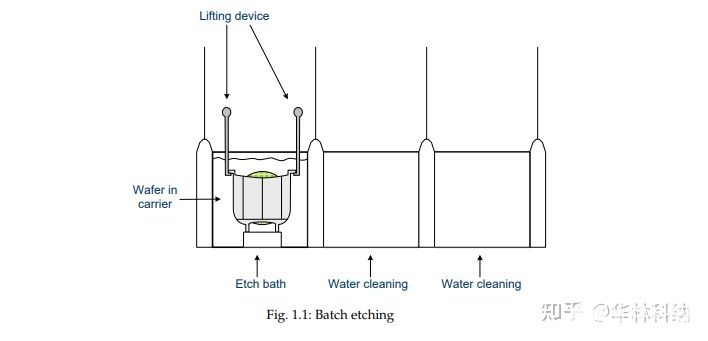

蝕刻工藝與光刻工藝密切相關。蝕刻之前通常先進行薄膜沉積(通過外延、化學或物理氣相沉積等)。通常,CVD薄膜涂有光刻膠,然后使用光刻(248nm 或 193nm UV、13.5nm EUV)通過圖案化的掩模版(掩模)曝光,光刻作用產生了圖層。在單晶圓等離子蝕刻室中,通常蝕刻化學品和離子轟擊并去除光刻膠沒有反應的CVD 薄膜(在正膠中)。蝕刻后,光刻膠灰化、濕法化學清洗和/或濕法蝕刻去除殘留物。

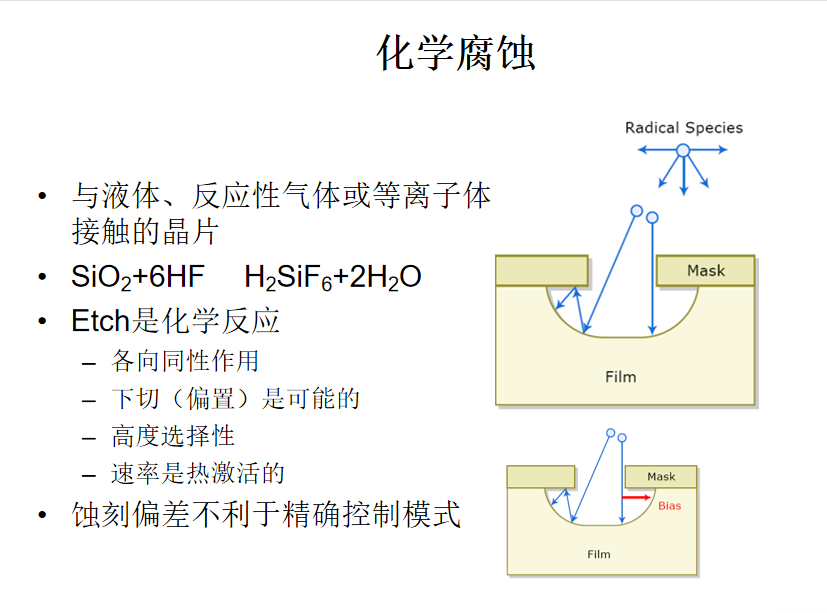

等離子蝕刻工藝可大致分為電介質、硅或導體蝕刻。二氧化硅和氮化硅等電介質最好使用氟化氣體蝕刻,而硅和金屬層與氯化學反應最好。基本上存在三種干法蝕刻模式——反應離子蝕刻(reactive ion etching)、等離子蝕刻(plasma etching)和濺射蝕刻( sputter etch:ion beam)。蝕刻工藝都是關于化學反應物、等離子體和晶圓材料之間復雜的相互作用。當 RF bias應用于反應性氣體時,電子和帶正電的離子轟擊晶圓以物理去除(蝕刻)材料,同時化學物質和自由基與暴露的材料反應形成揮發性副產物。蝕刻可以是各向同性的(垂直和水平反應相等),

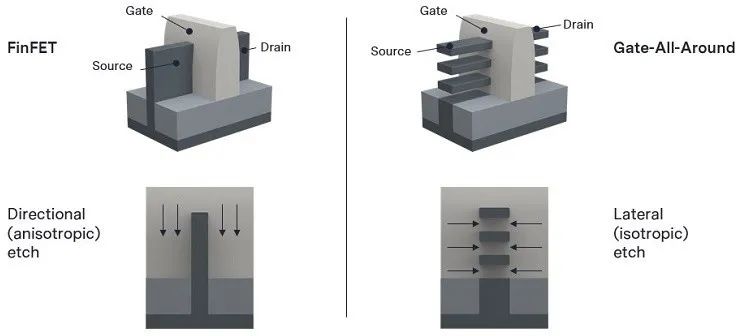

圖1:從 finFET 到 GAA 的過渡推動了關鍵的各向同性選擇性蝕刻要求

蝕刻工程師最關心的指標是蝕刻速率(etch rate)、輪廓控制(profile control)、均勻性(整個晶圓)和蝕刻選擇性(etch selectivity),因為這些會影響良率和生產率。蝕刻選擇性只是您要蝕刻的材料相對于其底層的去除率——例如,硅上的SiO 2 。在蝕刻過程中,不要去除過多的光致抗蝕劑也是有利的。但在這種情況下,通常會先將圖案轉移到硬掩模(二氧化硅、氮化硅、SiOC、TiN)上,然后再轉移到底層薄膜上。

選擇性規格從 2:1 到 1,000:1(高選擇性蝕刻)不等。隨著每個新節點的出現,這些規范變得更加嚴格。“隨著High NA EUV 在未來四年內開始取代常規 EUV,焦點要低得多,所以你不能再曝光厚光刻膠——我指的是 30 納米厚,” imec干法蝕刻研發工程師 Philippe Bézard 說。“但你仍然需要在下面圖案化相同的薄膜厚度。所以現在你要求更高的選擇性,而不是 2:1,我們必須達到更接近 10:1,這是選擇性突然提高 4 到 5 倍。”

從概念驗證 (POC:proof of concept) 到大批量制造 (HVM)

Bézard描述了蝕刻工藝開發的三個階段:

確定執行蝕刻所需的蝕刻機、氣體、輔助層等;

展示在規格范圍內完全去除薄膜的性能,并在一個晶圓上保持工藝均勻性;

確定如何在 HVM 中以高產量和小漂移在數千個晶圓上重復該過程;

通常,熟練的蝕刻和集成工程師會處理開發的前兩個階段。第三階段可能會再次利用工程專業知識,但機器學習可以提供幫助。

“一般來說,機器學習和數據分析只在第三階段有用,”他說。“它非常強大,因為它可以訪問大量數據,并且可以理解一百萬個相互作用的微小、簡單的事物。因此,對于人腦來說,試圖解決這個問題非常困難,但對于計算機程序而言,它更易于管理。但如果你有一個新的應用程序、新的蝕刻材料或新的集成,它并沒有顯示出比人類有任何改進。”

ML 的使用還與制造成本有關,因為在第三階段使用了數千個晶圓——至少比第一和第二階段使用的晶圓大一個數量級。

Lam Research 蝕刻產品組高級總監 Barrett Finch 將新工藝探索描述為從標稱工藝流程和布局中進行概念驗證,并在晶圓上開發一個或多個工作設備。然后將該 POC 轉移到晶圓廠的產品開發團隊,以擴大流程并提高良率。

Finch說:“將名義上的概念驗證轉變為可行的高收益產品所需的工作量往往被低估,這與盈利能力存在巨大差距。”“工藝窗口建模試圖通過在研發尋路的早期階段引入工廠變化來縮小這一差距。” 他建議虛擬 DOE 和基于 Monte Carlo 的分析跨多個過程參數,通過模擬預期的可變性來測試 POC。

“工藝窗口建模可以回答這個問題,我必須保持什么樣的 CD 或可變性水平才能達到最低設備性能和良率?'我們已經在幾天內完成了超過 100 萬個虛擬晶圓的虛擬工藝窗口測試,這在現實生活中是不可能完成的,”他說。

多個參數影響蝕刻速率(rate)、輪廓(profile)和選擇性(selectivity)。一個關鍵是溫度。“我們的客戶在控制蝕刻速率、選擇性和蝕刻輪廓時看到了熱效應對蝕刻加工的影響。Lam Research 半導體工藝和集成工程高級經理 Benjamin Vincent 表示,所有這些參數都會影響器件產量和晶圓廠生產率。他認為,當一個工藝步驟具有多種可能的配置(工藝空間很大),或者該步驟的下游結果高度不可預測時,模擬可能特別有用。

Esgee Technologies 的產品營銷經理 Alex Guermouche 表示:“蝕刻工藝依賴于晶圓的表面溫度,而這又取決于多種熱通量——包括熱傳導、離子碰撞能量、表面反應和等離子體輻射熱通量。”“因此,等離子體模型需要結合所有這些物理特征,以準確描述晶圓表面的溫度變化。工藝模擬軟件可以對一系列蝕刻屬性進行建模,使我們能夠更快地獲得更好的蝕刻結果,并加快客戶提高產量或優化產量的能力。”

蝕刻工藝的精確計時

對于更緊密的幾何形狀和更薄的薄膜,需要在蝕刻速率與對其他操作參數的良好控制之間取得平衡。

“隨著設計規則的縮小,許多蝕刻工藝正在轉向非常快速的等離子體蝕刻工藝步驟,這需要對所有反應輸入進行高度精確的控制:功率、壓力、化學和溫度,”Finch 說,并指出優化等離子體的趨勢脈沖行為產生特定的離子與中性比,然后清除副產物。“此類條件的高級建模對于實現進一步的設備縮放至關重要。”

一段時間以來,蝕刻系統制造商一直在使用建模軟件來加快下一個節點的開發或提高產量。考慮到該過程及其所有變量的絕對復雜性,這并不奇怪。

“在開發下一節點技術時,根本沒有足夠的時間或足夠的晶圓來執行所有可能的工藝實驗,”Finch 說。“蝕刻設備設置組合的數量可能達到數百萬,甚至數十億,使用所有工藝可能性的強力晶圓開發是根本不可能的。”

當然,所有好的模型都是在實際芯片上驗證的。“一個準確的模型應該具有預測性,它應該解決用戶想要解決的目標問題,”Finch說。“每次根據模擬工作推薦工藝或設計變更時,實際的晶圓廠數據應該反映推薦的結果。在我們的案例中,我們已經能夠使用基于模型的結果準確預測流程變化的影響,并快速解決困難的流程和技術開發問題。”

工具供應商還致力于先進的蝕刻工藝,以更緊密地集成生產線,并將曾經的雙掩模級工藝(兩個光刻步驟)轉變為一個工藝,以簡化工藝并降低成本。

Bézard 說:“公司沒有采用現有的硬件來讓瑞士軍刀裝備得更好,而是引入了特定于應用程序的技術,例如解決尖端問題的新系統。” 目的是使彼此面對的兩條線靠得更近,目前這涉及線圖案化步驟,然后是切割掩模。“應用材料公司和其他公司正在推出的是一種在水平方向上直接蝕刻的方法。” 這樣的過程也可以加寬通孔。

納米片 FET 的蝕刻步驟

納米片工藝流程中最關鍵的蝕刻步驟包括虛擬柵極蝕刻、各向異性柱蝕刻、各向同性間隔蝕刻和通道釋放步驟。通過硅和 SiGe 交替層的剖面蝕刻是各向異性的,并使用氟化化學。優化內部間隔蝕刻(壓痕)和通道釋放步驟,以極低的硅損失去除 SiGe。

溝道釋放步驟至關重要。“納米片的釋放需要極高的選擇性,”Bézard 說。“大多數納米片是硅,然后是硅鍺和硅。你有交替層,你需要刪除一個而不修改另一個。” 一些出版物已經討論了執行多步驟 SiGe 蝕刻以減少由單個蝕刻步驟引起的結構應力。

該制程的下一步是形成自對準觸點。“在這里,我們試圖做的基本上是蝕刻二氧化硅,而不是接觸或凹陷氮化硅。比方說,目前的規格是 3nm 凹陷,但人們要求零損失,”Bézard 說。“在這種情況下,我們甚至沒有使用選擇性這個詞。我們只是談論休會(recess)——而且是零休會(zero recess)。”

3D NAND

對于3D NAND閃存,層數不斷增加,未來需要采用多個堆疊層,最終創建堆疊設備的垂直串。“此外,隨著層數的增加,為了繼續增加位密度,有很大的動力來縮放層的字線間距或垂直/Z 間距,”TEL的技術總監和高級技術人員 Robert Clark說。“從工藝的角度來看,蝕刻和沉積工藝將需要不斷改進,以適應持續縮放所需的越來越小的關鍵尺寸和越來越高的縱橫比。”

Clark描述了未來的變化。“著眼于多層電荷陷阱器件的先進節點,需要對柵極堆疊進行工程設計,以實現更短的柵極長度、每個單元更多的電平和更高的編程效率——可能通過采用高 k 材料。未來也可能需要更高導電率的通道來取代多晶硅通道,”他說。

3D NAND 中最關鍵的蝕刻之一涉及通過多層氧化物-氮化物堆棧(200 層以上)深度蝕刻約 100 納米的孔,深度可達 10 微米。Imec 的 Bézard 說這個蝕刻步驟特別昂貴。

“我們有一種物理現象發生,稱為差異充電效應( differential charging effect),”他說。“在等離子體中,我們有電子、離子和中性物質可以簡化很多。電子向各個方向移動,但離子垂直于表面加速。所以你在孔的底部有正電荷,在頂部有負電荷,你會得到一個試圖排斥進入的離子的電場。”

結果,需要高功率水平來完全蝕刻溝槽。“我們正試圖在沒有電弧的情況下維持 30 到 50 gigawatts的功率,因此卡盤必須經過極好的拋光和制造,”他說。

深蝕刻還會產生需要最小化的應力,特別是因為多層 NAND 制造隨后需要晶圓減薄、精確對準和與下一層的混合鍵合。

其他工藝

并非所有芯片制造商都生產需要 EUV 光刻的尖端芯片。許多晶圓廠正在擴展其 193 納米光刻和蝕刻工藝。

“我們有一種最近開始推出的高溫 SOC 材料,它可以擴展其圖案化能力并能承受更高的溫度,無論它是用作 CVD 層還是掩模的底層,”Brewer Science半導體產品多元化總監 Brian Wilbur 說。

預計最緊密金屬線的BEOL將經歷從雙鑲嵌集成方案到除銅以外互連的減法沉積和蝕刻的巨大轉變。在這里,兩種金屬——釕和鉬——得到了最徹底的開發。然而,鉬在蝕刻過程中更容易氧化,使其更適合雙鑲嵌方案。釕是一種貴金屬,因此不存在同樣的腐蝕問題,但成本更高。

設備結構也變得不能容忍邊緣放置錯誤。據 TEL 的 Clark 稱,將需要新的層與層之間以及通孔和線路之間的自對準方案。“第一個實施可能是用于 DRAM 中的埋字線,以及用于邏輯的小間距 MOL 金屬層,這些地方需要更高的熱穩定性以及更低的電阻率或無襯墊金屬。”

下一代發展

從長遠來看,該行業理想情況下將過渡到較低熱預算的后端工藝(接近 300°C 而不是 400°C),以便將設備集成到后端互連層中。

“該行業確實需要開始將設備構建到更多層中,”TEL 的Clark說。“這意味著我們需要在 BEOL 熱預算內在 BEOL 內構建內存和邏輯設備。”

到目前為止,使用半導體氧化物制造的設備看起來很有前途,既可以用于將存儲設備集成到邏輯 BEOL 流程中,也可以用于在 DRAM 的存儲陣列之上構建 CMOS 陣列。

另一個重大轉變涉及二維材料的集成,研究機構和領先的芯片制造商已經開始對其進行測試。正在考慮對二硫化鎢或二硫化鉬等材料進行蝕刻工藝。這些薄膜由單層材料組成,因此開發集成它們的制造工藝極具挑戰性。

可持續性

芯片制造商和材料供應商正在尋求替代化學品以減少碳排放。在蝕刻中,罪魁禍首是具有高全球變暖潛能值的氟化氣體。

“有問題的 PFOS(全氟辛烷磺酸)的一個原因是因為分子非常穩定,”imec 的 Bézard 說。“大氣中的光或化學反應不足以分解它。”他說,許多含氧量較高的替代氣體混合物更容易分解,并且具有較低的 GWP。“然而,任何候選人都必須提供同樣好的甚至更高的表現才能開始。”

但可持續性并不是蝕刻或沉積的特別挑戰。這是從光刻到封裝的整體行業挑戰,其中新材料的影響影響整個設備處理。

編輯:黃飛

-

晶體管

+關注

關注

77文章

10018瀏覽量

141602 -

蝕刻工藝

+關注

關注

3文章

52瀏覽量

11935 -

3d nand

+關注

關注

4文章

93瀏覽量

29380

原文標題:蝕刻,走向何方?

文章出處:【微信號:wc_ysj,微信公眾號:旺材芯片】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

濕法蝕刻工藝的原理

在PCB外層電路中什么是蝕刻工藝?

【AD問答】關于PCB的蝕刻工藝及過程控制

PCB線路板外層電路的蝕刻工藝詳解

詳談PCB的蝕刻工藝

PCB外層電路的蝕刻工藝

濕法蝕刻工藝

《炬豐科技-半導體工藝》GaN 納米線制造和單光子發射器器件應用的蝕刻工藝

PCB蝕刻工藝原理_pcb蝕刻工藝流程詳解

PCB板蝕刻工藝說明

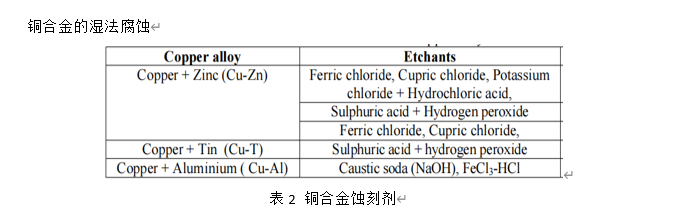

關于濕法蝕刻工藝對銅及其合金蝕刻劑的評述

淺談蝕刻工藝開發的三個階段

淺談蝕刻工藝開發的三個階段

評論