以反引號(`)開始的某些標(biāo)識符是 Verilog 系統(tǒng)編譯指令。編譯指令為 Verilog 代碼的撰寫、編譯、調(diào)試等提供了極大的便利。

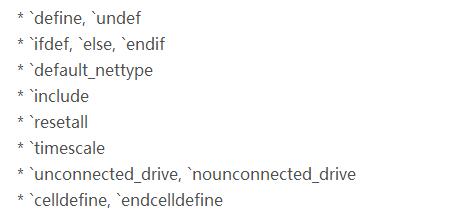

下面介紹下完整的 8 種編譯指令,其中前 4 種使用頻率較高。

define, undef

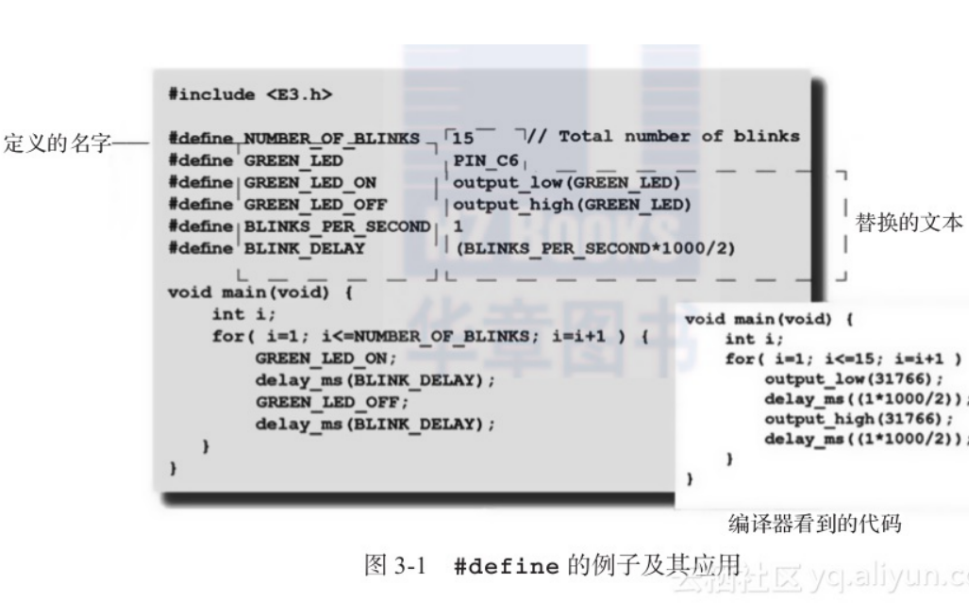

◆在編譯階段,`define 用于文本替換,類似于 C 語言中的 #define

一旦 `define 指令被編譯,其在整個編譯過程中都會有效。例如,在一個文件中定義:

`define DATA_DW 32

則在另一個文件中也可以直接使用 DATA_DW。

`define S $stop;

//用`S來代替系統(tǒng)函數(shù)$stop; (包括分號)

`define WORD_DEF reg [31:0]

//可以用`WORD_DEF來聲明32bit寄存器變量

◆`undef 用來取消之前的宏定義

`define DATA_DW 32

……

reg [DATA_DW-1:0] data_in ;

……

`undef DATA_DW

ifdef, ifndef, elsif, else, `endif

這些屬于條件編譯指令。例如下面的例子中,如果定義了 MCU51,則使用第一種參數(shù)說明;如果沒有定義 MCU、定義了 WINDOW,則使用第二種參數(shù)說明;如果 2 個都沒有定義,則使用第三種參數(shù)說明。

`ifdef MCU51

parameter DATA_DW = 8 ;

`elsif WINDOW

parameter DATA_DW = 64 ;

`else

parameter DATA_DW = 32 ;

`endif

elsif, else 編譯指令對于 ifdef 指令是可選的,即可以只有 ifdef 和 `endif 組成一次條件編譯指令塊。

當(dāng)然,也可用 `ifndef 來設(shè)置條件編譯,表示如果沒有相關(guān)的宏定義,則執(zhí)行相關(guān)語句。

下面例子中,如果定義了 WINDOW,則使用第二種參數(shù)說明。如果沒有定義 WINDOW,則使用第一種參數(shù)說明。

`ifndef WINDOW

parameter DATA_DW = 32 ;

`else

parameter DATA_DW = 64 ;

`endif

`include

使用 `include 可以在編譯時將一個 Verilog 文件內(nèi)嵌到另一個 Verilog 文件中,作用類似于 C 語言中的 #include 結(jié)構(gòu)。該指令通常用于將全局或公用的頭文件包含在設(shè)計文件里。

文件路徑既可以使用相對路徑,也可以使用絕對路徑。

`include "../../param.v"

`include "header.v"

`timescale

在 Verilog 模型中,時延有具體的單位時間表述,并用 `timescale 編譯指令將時間單位與實際時間相關(guān)聯(lián)。

該指令用于定義時延、仿真的單位和精度,格式為:

`timescale time_unit / time_precision

time_unit 表示時間單位,time_precision 表示時間精度,它們均是由數(shù)字以及單位 s(秒),ms(毫秒),us(微妙),ns(納秒),ps(皮秒)和 fs(飛秒)組成。時間精度可以和時間單位一樣,但是時間精度大小不能超過時間單位大小,例如下面例子中,輸出端 Z 會延遲 5.21ns 輸出 A&B 的結(jié)果。

`timescale 1ns/10ps //時間單位為1ns,精度為10ps,合法

//`timescale 10ps/1ns //不合法

module AndFunc(Z, A, B);

output Z;

input A, B ;

assign #5.207 Z = A & B

endmodule

在編譯過程中,timescale 指令會影響后面所有模塊中的時延值,直至遇到另一個 timescale 指令或 ` resetall 指令。

◆由于在 Verilog 中沒有默認(rèn)的 timescale,如果沒有指定 timescale,Verilog 模塊就有會繼承前面編譯模塊的 `timescale 參數(shù)。有可能導(dǎo)致設(shè)計出錯。

◆如果一個設(shè)計中的多個模塊都帶有 `timescale 時,模擬器總是定位在所有模塊的最小時延精度上,并且所有時延都相應(yīng)地?fù)Q算為最小時延精度,時延單位并不受影響。例如:

`timescale 10ns/1ns

module test;

reg A, B ;

wire OUTZ ;

initial begin

A = 1;

B = 0;

# 1.28 B = 1;

# 3.1 A = 0;

end

AndFunc u_and(OUTZ, A, B) ;

endmodule

在模塊 AndFunc 中,5.207 對應(yīng) 5.21ns。

在模塊 test 中,1.28 對應(yīng) 13ns,3.1 對應(yīng) 31ns。

但是,當(dāng)仿真 test 時,由于 AndFunc 中的最小精度為 10ps,因此 test 中的時延精度將進(jìn)行重新調(diào)整。13ns 將對應(yīng) 130010ps,31ns 將對應(yīng) 310010ps。仿真時,時延精度也會使用 10ps。仿真時間單位大小沒有影響。

◆如果有并行子模塊,子模塊間的 `timescale 并不會相互影響。

例如在模塊 test 中再例化一個子模塊 OrFunc。仿真 test 時,OrFunc 中的 #5.207 延時依然對應(yīng) 52ns。

//子模塊:

`timescale 10ns/1ns //時間單位為10ns,精度為1ns,合法

module OrFunc(Z, A, B);

output Z;

input A, B ;

assign #5.207 Z = A | B

endmodule

//頂層模塊:

`timescale 10ns/1ns

module test;

reg A, B ;

wire OUTZ ;

wire OUTX ;

initial begin

A = 1;

B = 0;

# 1.28 B = 1;

# 3.1 A = 0;

end

AndFunc u_and(OUTZ, A, B) ;

OrFunc u_and(OUTX, A, B) ;

endmodule

◆`timescale 的時間精度設(shè)置是會影響仿真時間的。時間精度越小,仿真時占用內(nèi)存越多,實際使用的仿真時間就越長。所以如果沒有必要,應(yīng)盡量將時間精度設(shè)置的大一些。

`default_nettype

該指令用于為隱式的線網(wǎng)變量指定為線網(wǎng)類型,即將沒有被聲明的連線定義為線網(wǎng)類型。

◆`default_nettype wand

該實例定義的缺省的線網(wǎng)為線與類型。因此,如果在此指令后面的任何模塊中的連線沒有說明,那么該線網(wǎng)被假定為線與類型。

◆`default_nettype none

該實例定義后,將不再自動產(chǎn)生 wire 型變量。

例如下面第一種寫法編譯時不會報 Error,第二種寫法編譯將不會通過。

//Z1 無定義就使用,系統(tǒng)默認(rèn)Z1為wire型變量,有 Warning 無 Error

module test_and(

input A,

input B,

output Z);

assign Z1 = A & B ;

endmodule

//Z1無定義就使用,由于編譯指令的存在,系統(tǒng)會報Error,從而檢查出書寫錯誤

`default_nettype none

module test_and(

input A,

input B,

output Z);

assign Z1 = A & B ;

endmodule

`resetall

該編譯器指令將所有的編譯指令重新設(shè)置為缺省值。

`resetall 可以使得缺省連線類型為線網(wǎng)類型。

當(dāng) resetall 加到模塊最后時,可以將當(dāng)前的 timescale 取消防止進(jìn)一步傳遞,只保證當(dāng)前的 timescale 在局部有效,避免 timescale 的錯誤繼承。

celldefine, endcelldefine

這兩個程序指令用于將模塊標(biāo)記為單元模塊,他們包含模塊的定義。例如一些與、或、非門,一些 PLL 單元,PAD 模型,以及一些 Analog IP 等。

`celldefine

module (

input clk,

input rst,

output clk_pll,

output flag);

……

endmodule

`endcelldefine

unconnected_drive, nounconnected_drive

在模塊實例化中,出現(xiàn)在這兩個編譯指令間的任何未連接的輸入端口,為正偏電路狀態(tài)或者為反偏電路狀態(tài)。

`unconnected_drive pull1

. . .

/*在這兩個程序指令間的所有未連接的輸入端口為正偏電路狀態(tài)(連接到高電平)*/

`nounconnected_drive

`unconnected_drive pull0

. . .

/*在這兩個程序指令間的所有未連接的輸入端口為反偏電路狀態(tài)(連接到低電平)*/

`nounconnected_drive

-

Verilog

+關(guān)注

關(guān)注

29文章

1366瀏覽量

111872 -

C語言

+關(guān)注

關(guān)注

180文章

7630瀏覽量

140478 -

PLL電路

+關(guān)注

關(guān)注

0文章

92瀏覽量

6719 -

MCU芯片

+關(guān)注

關(guān)注

3文章

256瀏覽量

11979

發(fā)布評論請先 登錄

一個簡單的8位處理器完整設(shè)計過程及verilog代碼

Verilog 預(yù)編譯

你知道Verilog HDL編譯器指令都有哪些嗎

循環(huán)模型編譯器Verilog和System Verilog語言支持指南

NICE自定義指令如何被編譯生成匯編文件和.verilog二進(jìn)制文件?

Verilog HDL硬件描述語言_Verilog語言要素

Verilog的語言要素

淺析VerilogHDL編譯系統(tǒng)的預(yù)處理

C語言編譯器常見的預(yù)編譯指令詳細(xì)資料說明

如何使用Icarus Verilog+GTKWave來進(jìn)行verilog文件的編譯和仿真

介紹下Verilog系統(tǒng)完整的8種編譯指令

介紹下Verilog系統(tǒng)完整的8種編譯指令

評論