封裝和層次結構

TLM接口的使用將驗證環境中的每個組件與其他組件隔離。驗證環境實例化一個組件,并完成其ports/exports的連接,不需要進一步了解驗證組件具體的實現。

較小的驗證組件可以組合成較大的驗證組件,此時上一級組件就是一個簡單的引出包含多個子組件的容器。

層次化連接

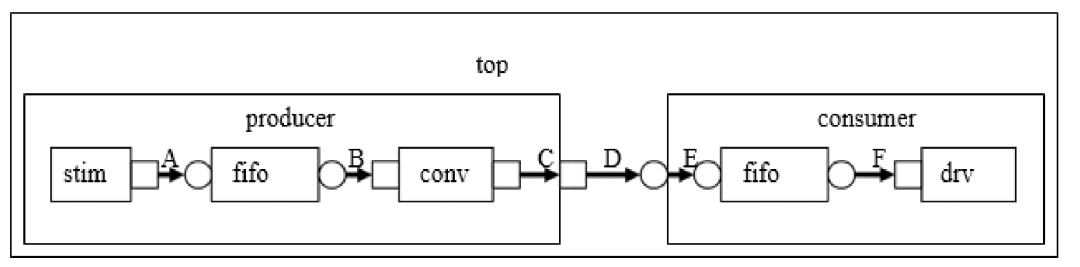

建立跨層次連接涉及到一些額外的問題,考慮下圖所示的分層設計。

這個設計的層次包含兩個組件,producer和consumer。producer包含三個組件,stim、fifo和conv。consumer包含兩個組件,fifo和drv。這兩個fifo都是uvm_tlm_fifo 組件的例化。

從頂層角度看,producer的put_port與consumer的put_export相連。在上圖中,A、B、D和F是標準的 peer-to-peer連接。連接A的代碼為:

stim.put_port.connect(fifo.put_export);

連接C和E有所不同,C是port-to-port的連接,E是export-to-export的連接。這兩種連接對于完成層次化連接是必要的。

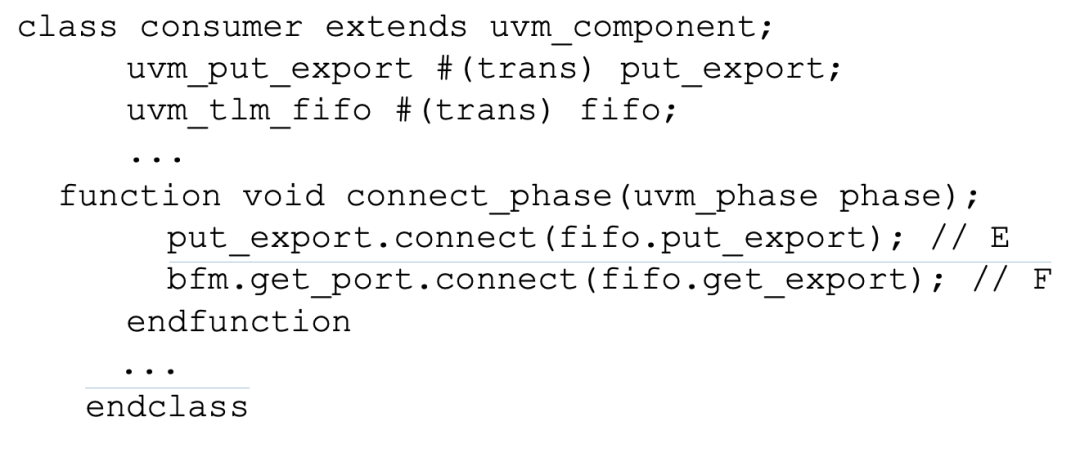

連接E的代碼為:

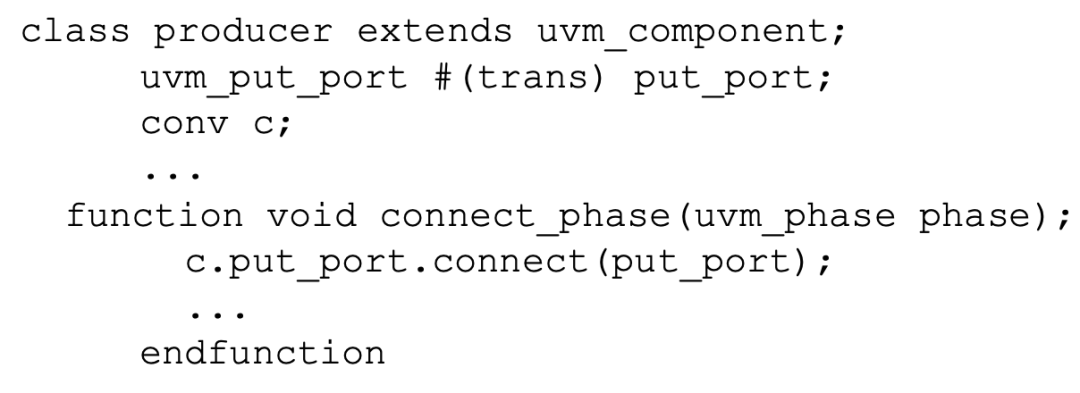

連接C代碼為

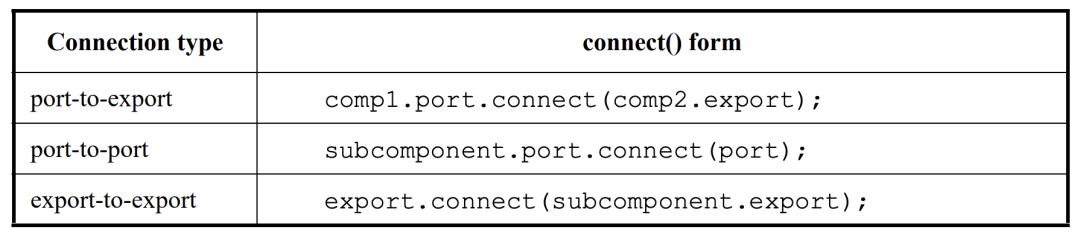

連接類型

port.connect()方法的參數可以是一個export和port,這取決于連接的性質(即peer-to-peer或者hierarchical)。

export.connect()的參數總是一個子組件的export。

審核編輯:湯梓紅

-

接口

+關注

關注

33文章

8933瀏覽量

153189 -

封裝

+關注

關注

128文章

8476瀏覽量

144770 -

UVM

+關注

關注

0文章

182瀏覽量

19426 -

代碼

+關注

關注

30文章

4886瀏覽量

70244 -

TLM

+關注

關注

1文章

33瀏覽量

24918

原文標題:層次化的UVM TLM連接

文章出處:【微信號:芯片驗證工程師,微信公眾號:芯片驗證工程師】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

關于層次化符號的管腳的一個疑問

數字IC驗證之“什么是UVM”“UVM的特點”“UVM提供哪些資源”(2)連載中...

什么是uvm?uvm的特點有哪些呢

請問一下在UVM中的UVMsequences是什么意思啊

談談UVM中的uvm_info打印

海信TLM3229G、TLM3729G彩電電路圖

ASIC芯片設計之UVM驗證

典型的UVM Testbench架構

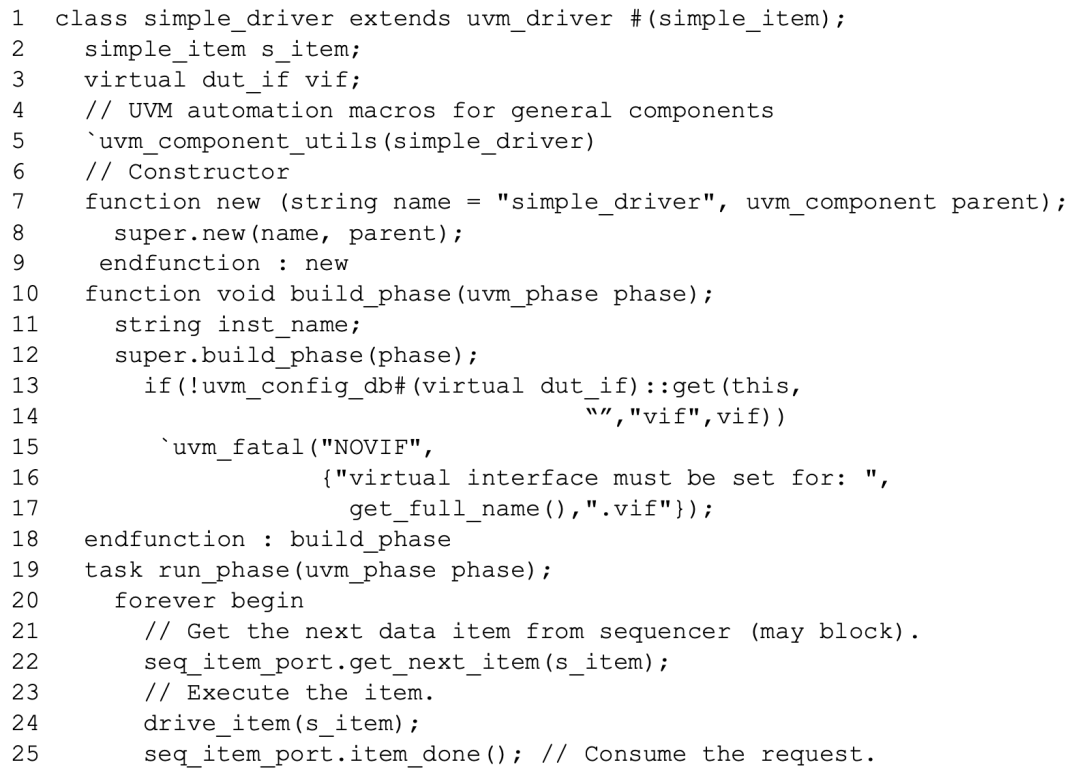

創建UVM Driver

Easier UVM Code Generator Part 4:生成層次化的驗證環境

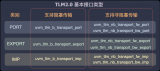

數字IC驗證之基本的TLM通信

層次化的UVM TLM連接

層次化的UVM TLM連接

評論