隨著實習(xí)面試的臨近、秋招的逐步靠近,愈發(fā)覺得知識需要成系統(tǒng),讓它們串接起來。不然,太容易忘了

1、單比特信號

1.1電平同步

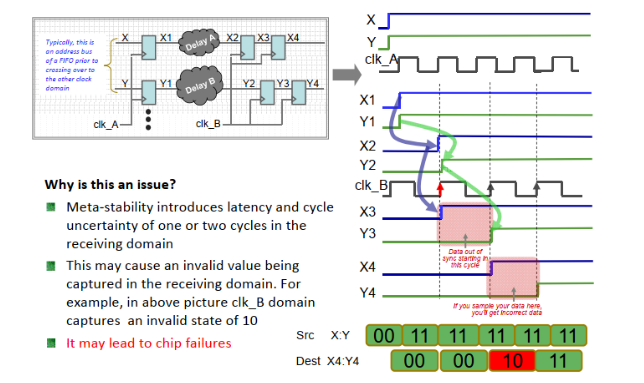

當(dāng)我們需要在兩個時鐘域間傳輸一個電平信號,這里的電平信號表示信號能夠維持一定的時間(如在原時鐘域內(nèi)至少維持兩個周期),可以采用兩個觸發(fā)器打拍。

類似下面這種,持續(xù)一定時間,能在亞穩(wěn)態(tài)穩(wěn)定后采樣到穩(wěn)定的值,即第一個周期可能同步失敗,但第二個周期有機會采樣穩(wěn)定的值,不發(fā)生亞穩(wěn)態(tài)

1.2、脈沖同步

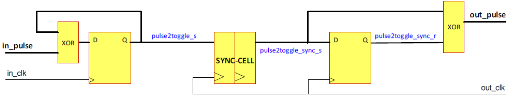

當(dāng)信號在發(fā)送端時鐘域內(nèi)只能持續(xù)一個周期時,可以稱為脈沖信號。要注意的是,發(fā)送的是脈沖,收到的也應(yīng)該是脈沖。

為了讓脈沖能夠被接收端采樣,可以將脈沖信號在發(fā)送時鐘域內(nèi)變成電平信號。即采樣到in_pulse為1,則翻轉(zhuǎn)Q,將脈沖變成邊沿。

只要脈沖有足夠的間隔,就能保證接收端能夠邊沿檢測,從而輸出一個接收時鐘周期的脈沖

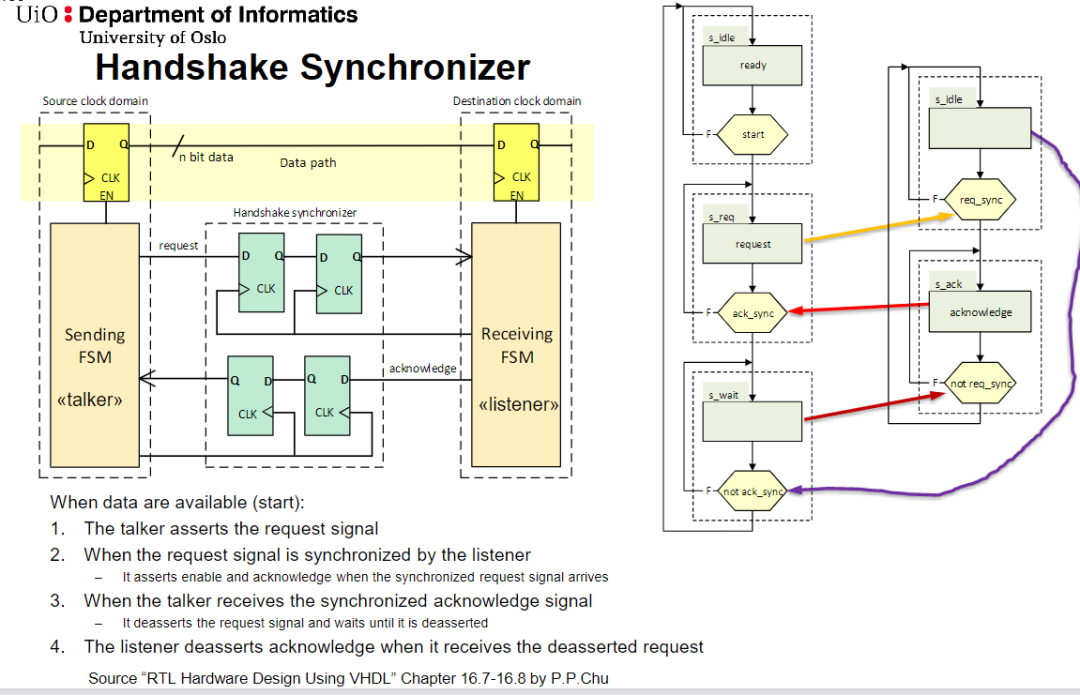

1.3 握手

很顯然,上面兩種方式不存在接收方對發(fā)送方的反饋。

也可以使用握手協(xié)議,確保一筆一筆的完成傳輸,只有完成一筆傳輸,才會改變數(shù)據(jù)。

見:握手信號傳輸跨時鐘域數(shù)據(jù)

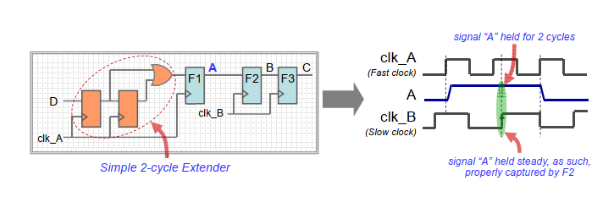

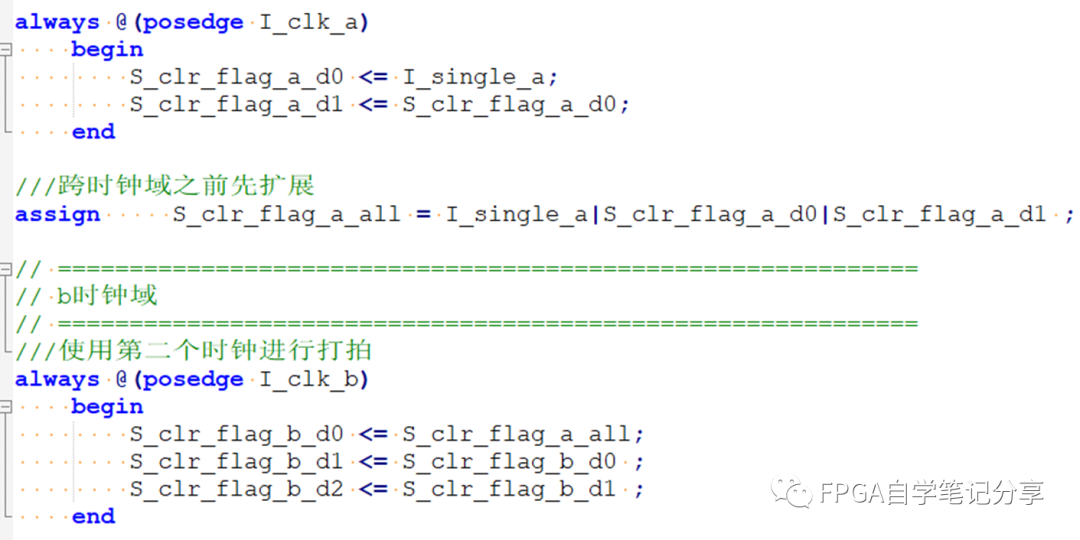

1.4 展寬

當(dāng)信號寬度不夠,可以使用展寬的方法,如在發(fā)送域打拍,然后取或

2、多bit

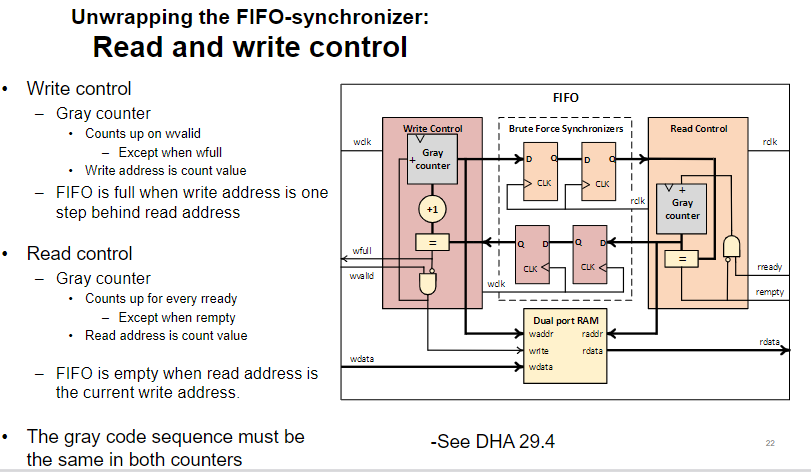

2.1 異步FIFO

使用異步FIFO傳輸數(shù)據(jù)--格雷碼計數(shù)器實現(xiàn)

使用異步FIFO傳輸數(shù)據(jù)--對以前的強烈批判

2.2 多路復(fù)用

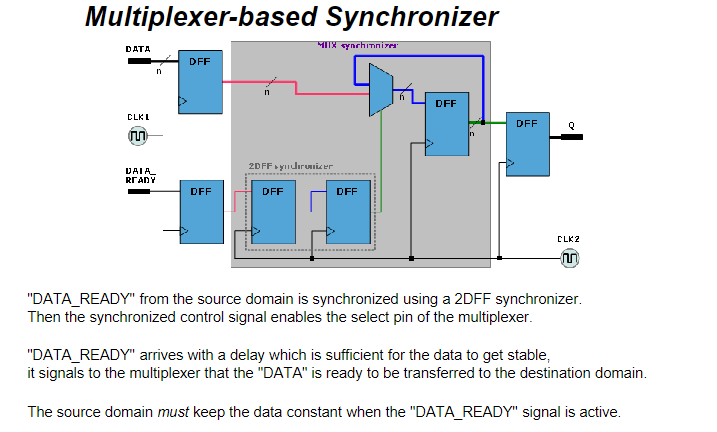

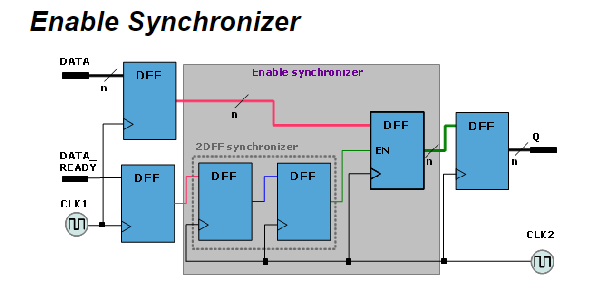

DMUX數(shù)據(jù)有效會搭配一個標(biāo)志信號data_ready,對標(biāo)志信號進(jìn)行同步,將同步后的標(biāo)志信號作為MUX的選通信號。

在發(fā)送時鐘域內(nèi),標(biāo)志信號和數(shù)據(jù)是同步的,在同步器內(nèi),標(biāo)志信號同步有延遲。這樣即使數(shù)據(jù)和標(biāo)志信號在接收時鐘上升沿附近變化,data_ready可能發(fā)生亞穩(wěn)態(tài),亞穩(wěn)態(tài)結(jié)束后,同步后的標(biāo)志信號可以正常工作。而數(shù)據(jù)在這些延遲內(nèi),能夠達(dá)到穩(wěn)定,即接收方采樣的data是不變的,當(dāng)然不會違反建立保持時間

這要求當(dāng)data_ready=1時,data要保持

換種方式,我們可以將標(biāo)志信號作為于觸發(fā)器使能端。道理是類似的,en=0,并不會使能觸發(fā)器的采樣

2.3 握手

和單bit類似,協(xié)議讓數(shù)據(jù)維持足夠的時間

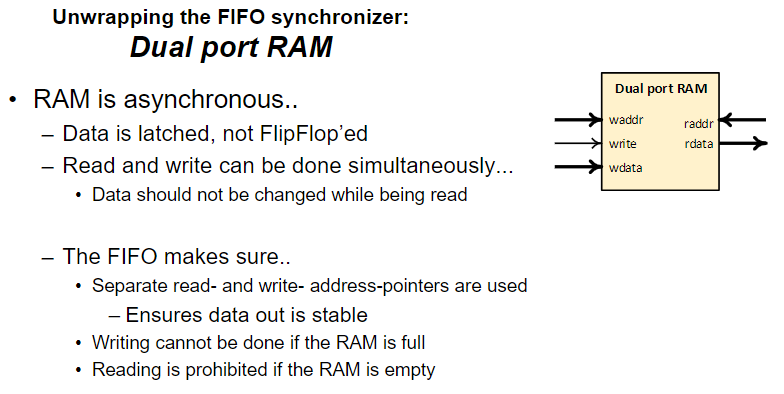

2.4 雙口RAM

雙口RAM可以同時讀寫

增加讀寫控制邏輯,很像異步FIFO,不多說

3、收斂

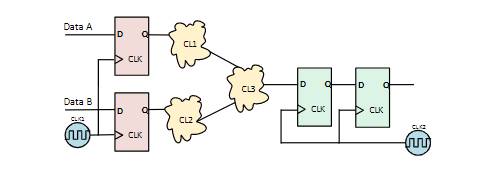

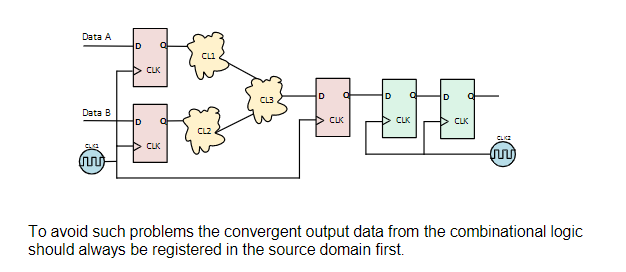

當(dāng)出現(xiàn)信號的合流時,如下圖所示,dataa和datab將經(jīng)過組合邏輯變成1bit。由于組合邏輯的延遲不同,可能出現(xiàn)毛刺,可能傳輸?shù)藉e誤的信號,

解決辦法就是發(fā)送方再打拍

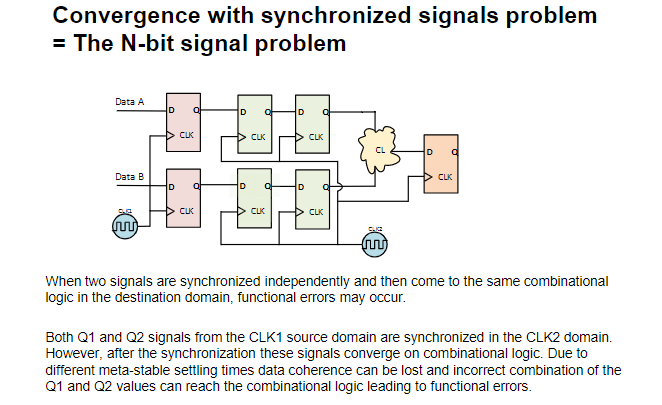

還要注意的是,兩級同步后,也應(yīng)該避免多比特使用組合邏輯,原因在于亞穩(wěn)態(tài)恢復(fù)的數(shù)據(jù)不確定

4、發(fā)散

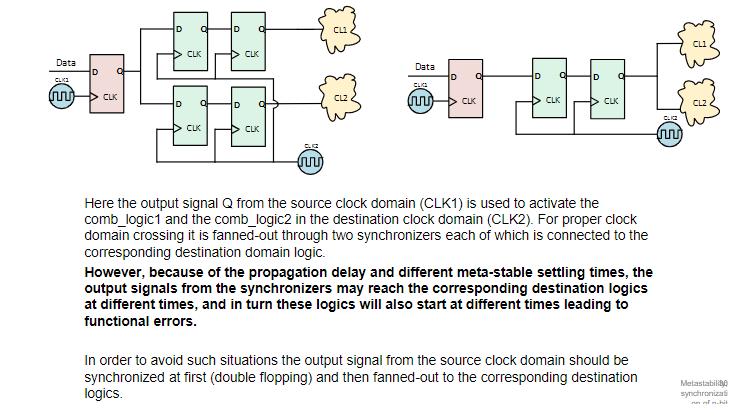

當(dāng)信號要作用于接收方的不同邏輯時,即有多個扇出,由于傳播延時和不同的亞穩(wěn)態(tài)解決時間meta-stable settling time,輸出也可能不同。

因此只能先同步然后使用,避免分別同步使用

審核編輯:湯梓紅

-

脈沖

+關(guān)注

關(guān)注

20文章

901瀏覽量

96754 -

fifo

+關(guān)注

關(guān)注

3文章

400瀏覽量

44619 -

信號

+關(guān)注

關(guān)注

11文章

2842瀏覽量

77902 -

Mux

+關(guān)注

關(guān)注

0文章

40瀏覽量

23668 -

時鐘域

+關(guān)注

關(guān)注

0文章

53瀏覽量

9726

原文標(biāo)題:跨時鐘域梳理

文章出處:【微信號:Hack電子,微信公眾號:Hack電子】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

跨時鐘域控制信號傳輸設(shè)計方案

關(guān)于RTC時鐘的知識點

關(guān)于FPGA中跨時鐘域的問題分析

如何處理跨時鐘域這些基礎(chǔ)問題

跨時鐘域知識點梳理

跨時鐘域知識點梳理

評論