第2章一個(gè)簡單的UVM驗(yàn)證平臺(tái)

2.4 UVM的終極大作:sequence

2.4.1 在驗(yàn)證平臺(tái)中加入sequencer

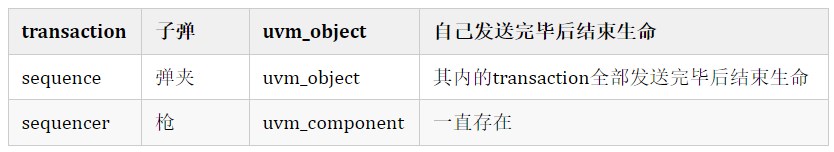

sequence機(jī)制作用:用于產(chǎn)生激勵(lì)。其分為兩部分,一是sequence,二是sequencer。

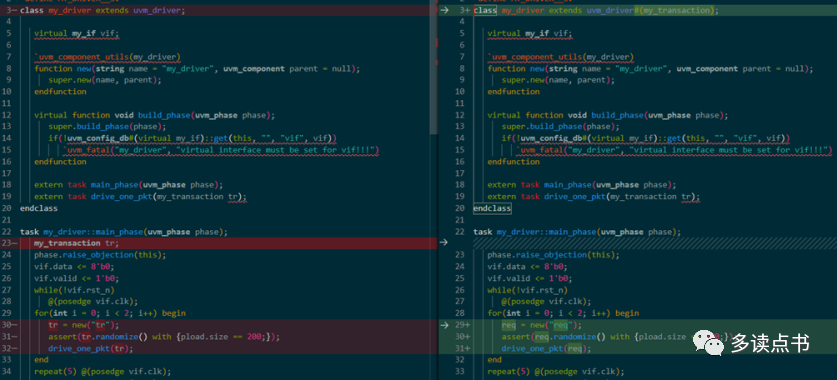

在定義driver時(shí)指明此driver要驅(qū)動(dòng)的transaction的類型,這樣定義的好處是可以直接使用uvm_driver中的某些 預(yù)先定義好的成員變量 ,如uvm_driver中有成員變量 req ,它的類型就是傳遞給uvm_driver的參數(shù)。由此帶來的變化如下:(不需要定義中間變量tr了)

2.4.2 sequence機(jī)制

三者關(guān)系:

每一個(gè)sequence都有一個(gè)body任務(wù),當(dāng)一個(gè)sequence啟動(dòng)之后,會(huì)自動(dòng)執(zhí)行body中的代碼。body中uvm_do這個(gè)宏的作用如下:

- 創(chuàng)建一個(gè)my_transaction的實(shí)例m_trans;

- 將其隨機(jī)化;

- 最終將其送給sequencer。

如果不使用uvm_do宏,也可以直接使用start_item與finish_item的方式產(chǎn)生transaction。

sequencer負(fù)責(zé)協(xié)調(diào)sequence和driver的請求

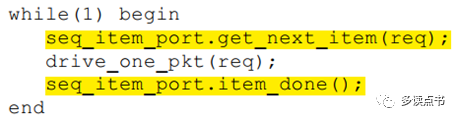

- sequencer和driver之間

- 將兩者連接:drv.seq_item_port.connect(sqr.seq_item_export);

- 在driver中通過get_next_item任務(wù)來得到一個(gè)新的req,并且驅(qū)動(dòng)它,驅(qū)動(dòng)完成后調(diào)用item_done通知sequencer(完成握手)。

- sequencer和sequence之間:

- sequence中的uvm_do宏發(fā)送transaction后,會(huì)一直等待,直到driver返回item_done信號(hào)。

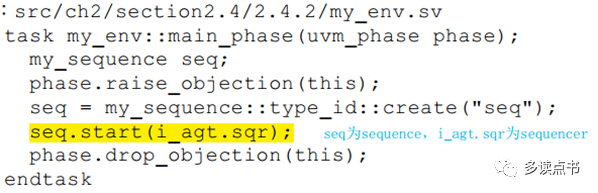

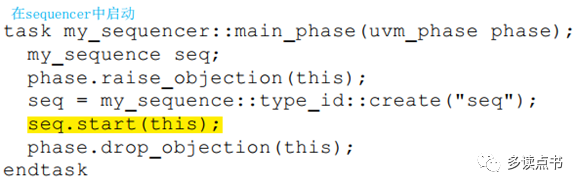

- 在某個(gè)component(如my_sequencer、 my_env)的main_phase中啟動(dòng)這個(gè)sequence,即可讓sequence向sequencer發(fā)送transaction。

get_next_item和try_next_item的比較

- get_next_item是阻塞的,它會(huì)一直等到有新的transaction才會(huì)返回;

- try_next_item則是非阻塞的,它嘗試著詢問sequencer是否有新的transaction,如果有,則得到此transaction,否則就直接返回。其行為更加接近真實(shí)driver的行為

2.4.3 default_sequence的使用

引入default_sequence的原因:

- 在某個(gè)component的build_phase階段使用config_db與default sequence替代了在某個(gè)component的main_phase階段利用seq.start(i_agt.sqr)啟動(dòng)sequence,將objection與sequence完全聯(lián)系起來,增加了可移植性。

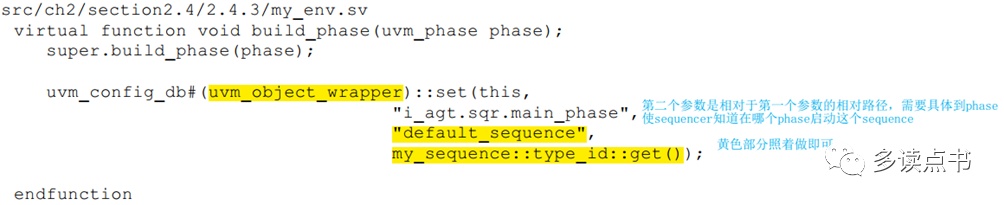

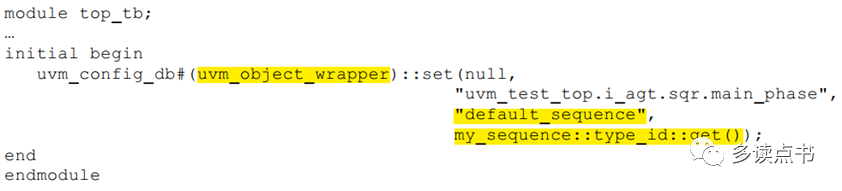

如何使用default_sequence:

- 方法一:在某個(gè)component(如my_env)的build_phase中設(shè)置如下代碼

- 方法二:在top_tb中設(shè)置

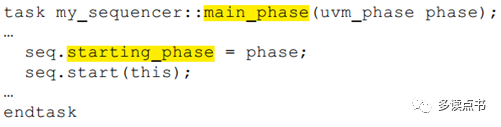

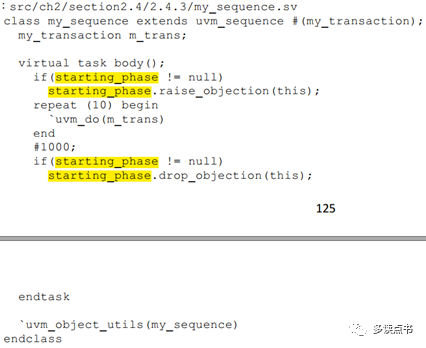

使用default_sequence時(shí) 如何提起和撤銷objection ?

- 因?yàn)樵趕equencer在啟動(dòng)default_sequence時(shí),uvm_sequence的內(nèi)置變量starting_phase會(huì)自動(dòng)執(zhí)行如下內(nèi)容:

- 所以可以在sequence中使用借助starting_phase來提起和撤銷objection。

2.5 建造測試用例

2.5.1 加入base_test

對(duì)my_env進(jìn)一步封裝,添加一些公司個(gè)性化內(nèi)容,舉例如下:

- 在report_phase中根據(jù)UVM_ERROR的數(shù)量來打印不同的信息。它在main_phase結(jié)束之后執(zhí)行。

- 設(shè)置整個(gè)驗(yàn)證平臺(tái)的超時(shí)退出時(shí)間

- 通過config_db設(shè)置驗(yàn)證平臺(tái)中某些參數(shù)的值

2.5.2 UVM中測試用例的啟動(dòng)

通過傳遞參數(shù)變量值啟動(dòng)的原因:

- 保證后加的測試用例不影響已經(jīng)建好的測試用例

如何使用:

- 定義不同的base_test,讓run_test()使用缺省模式,然后通過在命令中傳遞參數(shù)變量來實(shí)現(xiàn)一次編譯執(zhí)行多個(gè)用例,如下:

- +UVM_TEST_NAME=my_case0

-

UVM

+關(guān)注

關(guān)注

0文章

182瀏覽量

19434 -

sequence

+關(guān)注

關(guān)注

0文章

23瀏覽量

2967

發(fā)布評(píng)論請先 登錄

新手學(xué)習(xí)System Verilog & UVM指南

IC驗(yàn)證"為什么要學(xué)習(xí)UVM呢"

數(shù)字IC驗(yàn)證之“什么是UVM”“UVM的特點(diǎn)”“UVM提供哪些資源”(2)連載中...

什么是uvm?uvm的特點(diǎn)有哪些呢

談?wù)?b class='flag-5'>UVM中的uvm_info打印

UVM中seq.start()和default_sequence執(zhí)行順序

談UVM之sequence/item見解 sequencer特性及應(yīng)用(下)

Modelsim uvm庫編譯及執(zhí)行

計(jì)算機(jī)三級(jí)嵌入式學(xué)習(xí)筆記(三)

開關(guān)電源學(xué)習(xí)筆記 --- 目錄

UVM中uvm_config_db機(jī)制背后的大功臣

UVM中uvm_config_db機(jī)制背后的大功臣

一文詳解UVM設(shè)計(jì)模式

UVM學(xué)習(xí)筆記(三)

UVM學(xué)習(xí)筆記(三)

評(píng)論