人工智能和機器學習正在迅速滲透到廣泛的設備中,推動了SoC設計的重新架構,需要更多的內存空間和更高的帶寬來傳輸和處理數據。這種變化需要更高速的接口和更寬的總線,為增強最新的 PCIe、USB、DP 和 SATA 協議規范以及升級 PIPE(PCI Express 的 PHY 接口)規范作為首選 PHY 接口鋪平了道路。

PCIe 基本規范已升級到版本 5.0,修訂版 0.7,預計很快就會升級到修訂版 1.0。PCIe 5.0 引入了 32 GT/s 的更高鏈路速度作為其主要新功能,也稱為 Gen5 速度。為了加速PCIe系統的發展,PIPE接口在行業中得到了廣泛的應用。隨著基本規范升級到5.0,PIPE規范也在迎頭趕上,并已升級到5.1.1版本。最新的規格版本使 PIPE 接口能夠達到 Gen5 速度,并提供了一些額外的增強功能。

PIPE 規范已發展到版本 5.1.1,不僅是為了匹配最新的規范,而且還是為了擴展協議中的未來增強功能。在我們之前關于 PIPE – PCIe PIPE 4.4.1:PCIe 4.0 的推動者博客中,我們討論了 PIPE 規范版本 4.4 中可用的功能。在這篇博客中,我們將討論 PIPE 規范版本 5.1.1 中添加的新功能。

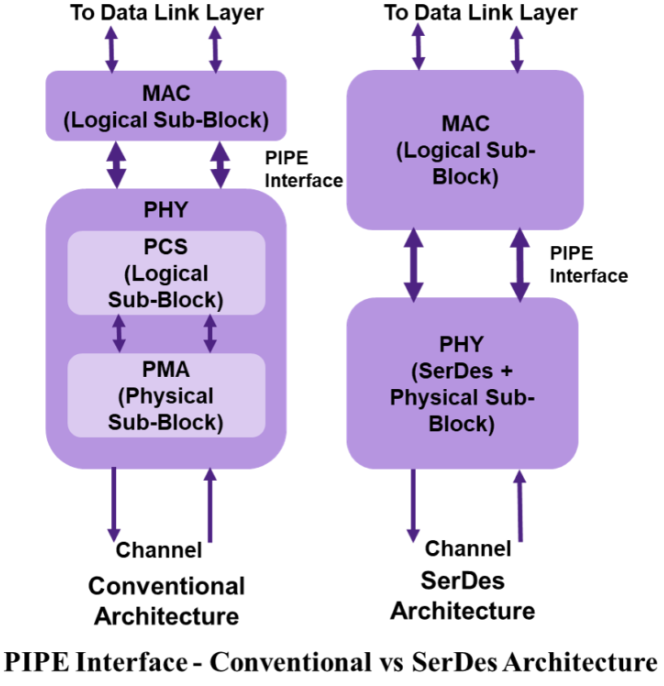

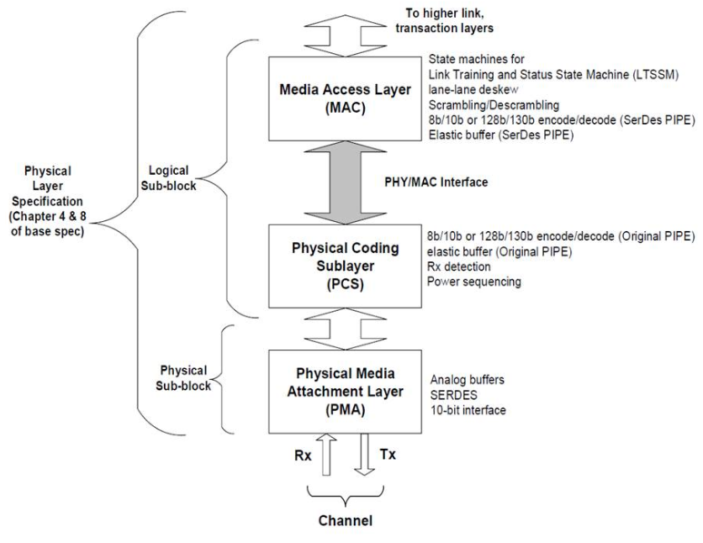

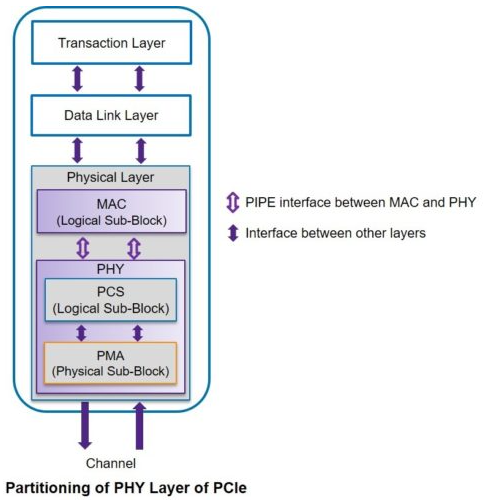

PIPE 4.4.1 已經將 PHY 設計的數字和模擬方面與控制器設計隔離開來,從而在 SoC 開發周期中提供了明確的推動力,因為現在控制器設計必須只滿足其設計的協議方面。但是,對于 PIPE 4.4.1,PHY 供應商應該為不同的協議開發不同的 PHY,或者設計單個復雜的 PHY 來滿足多種協議,如 PCIe、USB 和 SATA。當必須升級設計以適應 PCIe、USB、DP 和 SATA 協議規范中的所有增強和升級時,此使用模型不可擴展。此外,一種新的隧道協議也正在出現,通過通用PHY傳輸USB,PCIe和DP。這為PHY設計鋪平了道路,PHY設計簡單且與協議無關,能夠以更低的空間成本處理更高的帶寬。PIPE 5.1.1 通過引入新功能“SerDes 架構”和“低引腳數接口”,巧妙地解決了這些要求。

SerDes 架構使 PIPE 5 PHY 協議不可知,所有協議特定邏輯都轉移到控制器。這簡化了PHY設計,并允許不同的協議棧輕松共享。低引腳數接口可滿足低房地產成本要求。對于更寬的數據總線,數據路徑已經消耗了接口上的許多引腳。減少引腳總數;大多數非時間關鍵邊帶信令握手通過MBI總線移動。有效的結果是PIPE接口上的引腳數量更少,數據路徑更寬。此方法還可以針對未來的協議增強功能進行擴展。

PIPE 5.1.1 規范除了 SerDes 架構和低引腳數接口外,還有一些額外的更新。以下列表總結了 PIPE 5.1.1 中的所有主要升級:

添加了對顯示端口和融合 IO 協議的支持,同時保持對 PCIe、USB 和 SATA 協議的支持

低引腳數接口

刪除了舊版握手信號

將遺留信號映射到 PHY 和 MAC 的消息總線寄存器

引入了消息總線命令 [讀取和寫入] 的使用,以在以下所有子功能中在 PHY 和 MAC 之間通信握手

接收器均衡

動態均衡

TxDeemph, FS, LF, LocalFS, LocalLF 設置

接收器裕量

車道邊距

彈性緩沖區控制

極性反轉

塊對齊控制

塞爾德斯建筑

啟用與現有常規 8/16/32 位數據路徑等效的 SerDes 數據路徑

啟用新的更寬的 SerDes 數據路徑,相當于傳統的 64 位數據路徑。

低功耗 L1 子狀態支持使用邊帶信號

已棄用“PCLK 作為 PHY 輸出模式”,用于 PIPE 接口的操作

強制要求“PCLK 作為 PHY 輸入模式”,用于 PIPE 接口的操作

這簡化了PHY設計,因為“時鐘生成”的負擔現在轉移到控制器設計中

添加了MAC和PHY握手,用于通信“速率”,“寬度”和“pclk_rate”信號變化

PclkChangeOk 和 PclkChangeAck 信號用于此握手

PHY 使用 PclkChangeOk 信號與 MAC 通信,表明 MAC 已準備好更改速率、寬度或 Pclk 頻率

MAC使用PclkChangeAx信號與PHY通信,表明速率,寬度或Pclk頻率的變化是完整和穩定的

添加了對 P2 電源狀態下接收器檢測的支持

已棄用的“車道關閉”信號

其中許多更新以向后不兼容為代價提供了未來的可擴展解決方案。其中一個示例是要求棄用傳統邊帶信號并使用 MBI 總線在 MAC 和 PHY 消息總線寄存器空間之間發出握手信號。用于邊帶信號(例如均衡信號)的傳統 PIPE 接口對于任何符合 PCIe 4.0 的設備執行接收器均衡和動態均衡功能是必需的,現在不再適用于符合 PCIe 5.0 的設備。接收器均衡和動態均衡通過 MBI 總線傳輸,使用 MBI 讀寫命令從 MAC 和 PHY 的消息總線寄存器空間寄存器。

另一個劇烈的架構變化是對 SerDes 架構的可選支持。對于 PCIe 4.0 設備,對 SerDes 架構的支持是可選的,但對于 PCIe 5.0 設備是強制性的。隨著SerDes架構的引入,與原始PIPE架構相比,PHY實現了最少的數字邏輯。這使得PHY設計具有可擴展性,并且易于在不同協議之間共享。仍然建議使用 PHY 設計來支持傳統架構,以保持與選擇不遷移到 SerDes 架構的 MAC 的互操作性。傳統架構和SerDes架構的區別如下圖所示。

審核編輯:郭婷

-

soc

+關注

關注

38文章

4338瀏覽量

221692 -

人工智能

+關注

關注

1804文章

48708瀏覽量

246482 -

機器學習

+關注

關注

66文章

8492瀏覽量

134088

發布評論請先 登錄

TS2PCIE412ruar芯片能否用于SATA1.0信號切換?是否支持SATA OBB信號?

請問Virtex7 GTX如何生成PIPE接口PCIE PHY?

沉浸式Android11移植,iTOP-RK3568開發板雙核GPU,獨立NPU,SATA3.0,PCIE3.0

iTOP3A5000開發板多路PCIE、SATA、USB3.0等

USB標準適用于哪些應用

VIAVI推出適用于PCIe 5.0協議一致性訓練器

LTC3529 - 1.5A、1.5MHz 同步升壓型穩壓具自動故障檢測功能,適用于 USB OTG 應用

詳解串行總線中的SATA協議

如何支持USB、DP、PCIe三種信號協議?

揭秘PCIe PIPE 5.1 SerDes架構

PCIe PIPE 4.4.1:PCIe Gen4的推動者

適用于Emulex和OEM適配器的VMWARE ESXi 5.0/5.1 FC/FCoE驅動程序

VIAVI Xgig4K-PCIe-X4-FL飛行引導插入器適用于PCIE4.0在被測設備和VIAVI協議分析儀機箱箱之間提供數據信號連接

適用于PCIe 5.1、DP 1.5、USB 0.1、SATA和未來協議的PIPE 4.3.2

適用于PCIe 5.1、DP 1.5、USB 0.1、SATA和未來協議的PIPE 4.3.2

評論