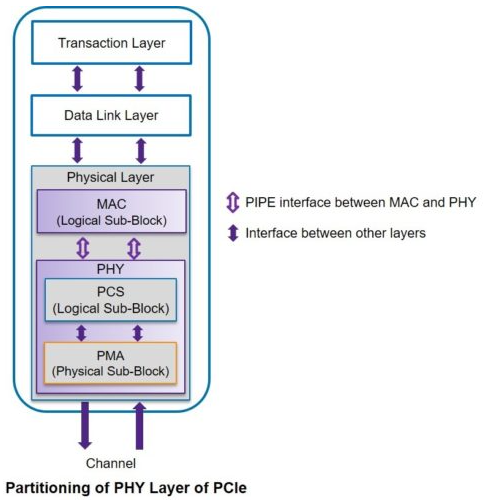

PCIe 是一種多層串行總線協議,可實現雙單工鏈路。由于其專用的點對點拓撲,它提供高速數據傳輸和低延遲。為了加快基于 PCIe 的子系統的驗證和設備開發時間,英特爾定義了 PIPE(PCI Express 的 PHY 接口)架構。PIPE 是 PHY 子層(PCS – 物理編碼子層)和 MAC(媒體訪問層)之間定義的標準接口。

PIPE 的第一個穩定版本于 2 年作為 PIPE 0.2007 發布。隨著時間的推移,PIPE 已經發展到支持更高的速度和下一代 PCIe 規范的附加功能。4年初發布的PIPE 4.1.2017規范完全符合支持4GT / s速度的PCIe 0.16基本規范。它比 PIPE 4.3 有了重大改進,同時保持了向后兼容性。下圖說明了 PIPE 接口和 PCIe 的 PHY 層的分區。

以下列表總結了 PIPE 4.4.1 和 PIPE 4.3 中新添加/修改的功能。

標稱空彈性緩沖區模式: 與標稱半滿彈性緩沖區模式相比,以更小的最壞情況和平均延遲提供更好的數據流優化。

引入消息總線接口的 Rx 裕量:提供一種使用少量導線啟動和參與非延遲敏感型 PIPE 操作的方法。它還可以在不添加額外電線/信號的情況下執行剛剛發布的 PIPE 5.0 操作。

SRIS:提供一種方法來指示有關獨立 Refclk 獨立 SSC 體系結構支持的 PHY。

MAC 和本地 PHY 之間的第 4 代均衡:為 Gen4 均衡提供專用控件,而不是 Gen3 均衡。

L1 次州電源管理:通過引入 RxEiDetectDisable 和 TxCommonModeDisable 信號提供超低功耗操作。

Tx合規性和TxElecIdle信號采樣機制。

審核編輯:郭婷

-

接口

+關注

關注

33文章

8932瀏覽量

153179 -

總線

+關注

關注

10文章

2947瀏覽量

89326 -

PCIe

+關注

關注

16文章

1322瀏覽量

84647

發布評論請先 登錄

請問Virtex7 GTX如何生成PIPE接口PCIE PHY?

PCIe Gen-3高速前端卡參考設計

了解PIPE4.4規范及PCIe 4.0的開發設計

邁威科技PCIe Gen4 NVMe SSD控制器面世!推進下一代技術發展

PCIe Gen 4協議分析儀的竟然那么強大!

三星開發了基于PCIe Gen4的SSD新產品PM1733

邁入高速新進程,上海寶存推出PCIe Gen4企業級存儲

為什么PCIe Gen3/Gen4不使用CXL

FORESEE成功研發出旗下首款PCIe Gen 4×4 SSD

西部數據推出高性能、輕薄低功耗的PCIe Gen4 NVMe SSD

江波龍推出PCIe Gen4×4無緩存主控SSD XP2000d

江波龍FORESEE推出PCIe Gen4×4無緩存主控SSD——XP2000

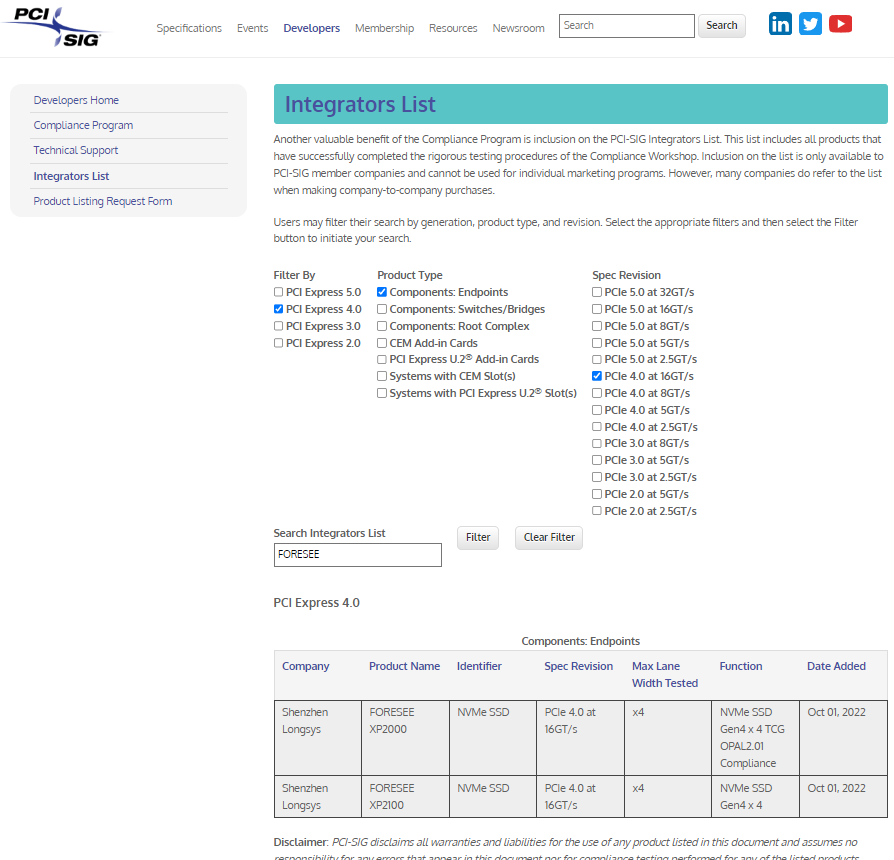

FORESEE PCIe Gen4 SSD系列產品通過PCI-SIG兼容性認證

江波龍FORESEE PCIe Gen4 SSD系列產品通過PCI-SIG兼容性認證

FORESEE推出首款自研PCIe Gen4 BGA SSD,輕薄終端的存儲“更優解”

PCIe PIPE 4.4.1:PCIe Gen4的推動者

PCIe PIPE 4.4.1:PCIe Gen4的推動者

評論