如果你正在使用Vivado開發套件進行設計,你會發現綜合設置中提供了許多綜合選項。這些選項對綜合結果有著潛在的影響,而且能夠提升設計效率。為了更好地利用這些資源,需要仔細研究每一個選項的功能。本文將要介紹一下Vivado的綜合參數設置。

一、Vivado綜合參數介紹

在Vivado中,默認情況下,綜合器會根據指定的目標芯片和設定的優化策略來產生最優的電路實現方案。常用的選項都可以在下圖菜單中設置。

1、flatten_hierarchy

這個參數決定了Vivado綜合工具將如何控制層次結構,一般默認為rebuilt,主要有以下3個參數選項:

(1)full

表示采用完全展平層次結構,只留下頂層。只保留頂層層次,執行邊界優化 。

(2)none

表示采用不展平層次結構, 綜合后的輸出具有與原始RTL相同的層次結構,且不執行邊界優化 。

(3)rebuilt

表示允許綜合工具展平層次結構,然后根據原始RTL重建層次結構。 此值允許跨邊界優化的QoR優勢,最終層次結構與RTL類似,便于分析。

2、gated_clock_conversion

控制綜合工具的轉換時鐘邏輯能力,使用門控時鐘轉換還需要使用RTL屬性才能工作。

3、fsm_extraction

控制狀態機的編碼方式綜合方式,默認值為auto,此時vivado會自動推斷最佳的編碼方式,它有以下幾個選項:關閉、sequential、獨熱碼、自動等等,其設定的FSM編碼方式優先于HDL代碼中定義的方式。

4、fsm_encoding

設置針對某個狀態機設定編碼方式,綜合屬性 -fsm_coding的優先級高于-fsm_extraction,但如果HDL代碼中已經定義了編碼方式,該設定將無效。

5、 Keep_equivalent_registers

設置是否保留等效寄存器,equivalent registers也就是等效寄存器,共享輸入數據的寄存器。 勾選時,等效寄存器不會合并; 不勾選時,等效寄存器會被合并。

6、resource_sharing

設置算術運算通過資源共享來優化設計資源,默認值為auto。

7、control_set_opt_threshold

設置是否開啟控制集的優化,以減少控制集的個數,但會增加LUT資源消耗。 觸發器的控制集由時鐘信號、復位/置位信號和使能信號構成,通常只有{clk,set/rst,ce}均相同的觸發器才可以被放置在一個SLICE中,但開啟這個參數后3個觸發器會被放置到同一個SLICE中。

8、no_lc

是否開不允許出現LUT整合。 通過LUT整合可以降低LUT的資源消耗,但也可能導致布線擁塞。 因此,xilinx建議,當整合的LUT超過了LUT總量的15%時,應考慮勾選-no_lc,關掉LUT整合。

9、shreg_min_size

影響移位寄存器的實現方式,默認值為3。 當HDL代碼描述的移位寄存器深度大于此設定值時,將采用“觸發器+SRL+觸發器”的方式實現,其中SRL由LUT實現。

10、bufg

控制綜合時推斷出來的BUFG數量。 當綜合過程中看不到設計網表中的其他BUFG時,Vivado設計工具會使用此選項,可以推斷出指定的數量,并跟蹤在RTL中實例化的BUFG數量。 例如,如果bufg選項設置為12并且在RTL中實例化了三個BUFG,則該工具最多可以推斷出9個BUFG。

11、fanout_limit

設置全局信號高扇出數目,但當HDL代碼中有MAX_FANOUT時,該屬性失效。

12、directive

設置不同的優化策略,主要選項參數如下:

- Default,默認設置。

- RuntimeOptimized,執行最短時間的優化選項,會忽略一些RTL優化來減少綜合運行時間。

- AreaOptimized_high/medium,執行一些通用的面積優化。

- AlternateRoutability,使用算法提高布線能力,減少MUXF和CARRY的使用。

- AreaMapLargeShiftRegToBRAM,將大型的移位寄存器用塊RAM來實現。

- AreaMultThresholdDSP,會更多地使用DSP塊資源。

- FewerCarryChains,位寬較大的操作數使用查找表(LUT)實現,而不用進位鏈。

13、max_bram

設定當前工程的最大塊RAM數量,通常在設計中有黑盒或第三方網表時使用,默認設置為-1時,表示使用當前芯片的最大塊RAM數量。

max_uram:指定ultra ram最大使用個數。 max_bram_cascade_height:指定bram最大級聯數。 max_uram_cascade_height:指定uram最大級聯數。

14、max_dsp

設定當前工程的胡最大塊DSP的數量。 與max_ram一樣。

15、cascase_dsp

控制sum DSP塊輸出中的加法器,默認為auto。 auto表示使用塊內置加法器鏈計算DSP輸出的總和。 tree強制在結構中(Fabric)實現總和。

16、tcl.pre和tcl.post

在綜合之前和之后立即運行的Tcl文件

二、重要選項介紹

1、Report Setting

設置是否開啟綜合資源消耗報告,默認開啟即可,如果不需要看,可以關閉。

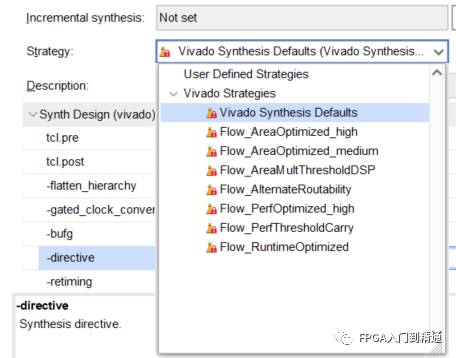

2、Setting設置中的Strategy

這里可選不同優化策略設計,使得設計滿足相應的需求,如下圖所示:

(1) “速度優化”:使時鐘頻率最快。 面積和功耗可能更大。

(2) “平衡優化”:在速度和面積之間取得平衡。

(3) “面積優化”:使元素數量最少,但可能會影響時鐘速度和功耗。

(4) “功耗優化”:降低功耗。

三、HDL代碼設置綜合屬性

1、srl_style

srl_style可設定移位寄存器的不同實現方式,主要有以下幾種方式:

(* srl_style = “srl_reg” ),實現移位寄存器為SRL + FF結構。

( srl_style = “reg_srl” ),實現移位寄存器為FF + SRL結構。

( srl_style = “reg_srl_reg” ),實現移位寄存器為FF + SRL + FF 結構。

( srl_style = “register” ),實現移位寄存器為純FF結構。

( srl_style = “srl” *),實現移位寄存器為純SRL結構。

其中SRL可以有效減小面積,相比級聯寄存器的結構性能要更好,如果再加了FF,時序性能更好。

2、ram_style和rom_style

定義存儲器實現方式,主要有以下幾種方式:

(*ram_style = "block" *),表示用Block RAM實現

(*ram_style = "reg" *),表示用寄存器實現

(*ram_style = "distributed" *),表示用分布式 RAM實現

(*ram_style = "uram" *),表示用uram實現

3、use_dsp48

定義實現這部分算術運算使用dsp資源進行實現,常用形式為:( use_dsp48=“yes” )。

(*use_dsp48=“yes”*) reg test;

4、dont_touch

dont_touch可以防止相關內容被邏輯優化,常用形勢為:( dont_touch =“yes” )

(*dont_touch =“yes”*) reg test;

5、max_fanout

設置當前信號的最大扇出數目,常用形式為:(* max_fanout = “20”*)

(*MAX_FANOUT = 50 *) reg test;

-

HDL

+關注

關注

8文章

330瀏覽量

48047 -

編碼

+關注

關注

6文章

969瀏覽量

55766 -

開發套件

+關注

關注

2文章

177瀏覽量

24674 -

綜合器

+關注

關注

0文章

12瀏覽量

6593 -

Vivado

+關注

關注

19文章

835瀏覽量

68754

發布評論請先 登錄

變頻器的參數設置及缺陷的處理

變頻器功能參數設置

變頻器設置面板及參數設置方法

Vivado綜合參數設置

Vivado綜合參數設置

評論