本文主要介紹Vivado布線參數(shù)設(shè)置,基本設(shè)置方式和vivado綜合參數(shù)設(shè)置基本一致,將詳細說明如何設(shè)置布線參數(shù)以優(yōu)化FPGA設(shè)計的性能,以及如何設(shè)置Vivado壓縮BIT文件。

一、Vivado布線概述

Vivado布線是在FPGA設(shè)計中實現(xiàn)物理布局的關(guān)鍵步驟之一。 這一步驟不僅可以對綜合后生成的網(wǎng)表進行邏輯綜合優(yōu)化,還可以進行針對特定設(shè)計的功率和物理綜合設(shè)計進行優(yōu)化。 最終目標是建立一個符合設(shè)計要求的物理布局,同時最小化電路的時鐘周期延遲和功耗消耗。

主要布線步驟如下:

說明:

opt_design:邏輯優(yōu)化;

power_opt_design:可選,電源優(yōu)化。

place_design:布局設(shè)計。

phys_opt_design:可選,物理綜合優(yōu)化。

route_design:布線設(shè)計。

write_bitstream:生成bit文件。

二、布線參數(shù)設(shè)置

在設(shè)置界面中,可以選擇指定的約束文件、綜合策略,如下圖所示:

1、Incremental implementation

增量編譯設(shè)置,可以選擇加載上一版本布線后DCP文件,優(yōu)化編譯速度。

2、Startegy

布線策略選擇,根據(jù)實際需要來選擇,一般選用默認配置即可。

3、參數(shù)設(shè)置說明

(1)directive與strategy

directive:是指定某一階段的指令,用于設(shè)定某一階段的優(yōu)化策略和實現(xiàn)方法。

strategy:是為了整個工程的實現(xiàn)指標,而運行了一系列的directive,算是各階段directive指定好的策略合集。

(2)tcl.pre和tcl.post

可選擇加載TCL文件,用于在布線前和布線后執(zhí)行的邏輯。

三、設(shè)置Vivado壓縮BIT文件

Vivado 生成bit文件可以設(shè)定是否壓縮,這樣可以降低flash存儲空間的占用

1、添加約束的方法

在XDC約束文件中,添加這個約束即可:

set_property BITSTREAM.GENERAL.COMPRESS TRUE [current_design]

2、設(shè)置生成bit操作的參數(shù)

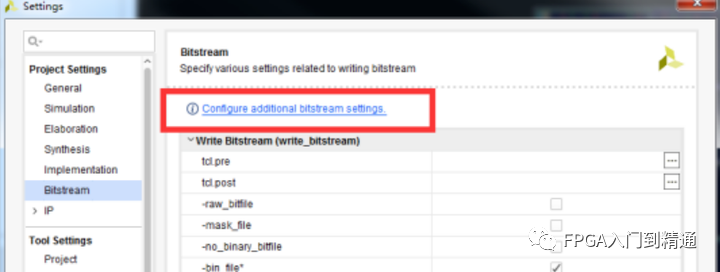

打開settings界面,選擇bitstream,點開“Configure additional bitstream settings”

將壓縮BIT文件的選項設(shè)置為True即可

-

FPGA

+關(guān)注

關(guān)注

1643文章

21964瀏覽量

614116 -

參數(shù)

+關(guān)注

關(guān)注

11文章

1867瀏覽量

32865 -

布線

+關(guān)注

關(guān)注

9文章

792瀏覽量

84895 -

bit

+關(guān)注

關(guān)注

0文章

48瀏覽量

32360 -

Vivado

+關(guān)注

關(guān)注

19文章

829瀏覽量

68229

發(fā)布評論請先 登錄

PMAC_參數(shù)設(shè)置

如何設(shè)置PCB編輯器的參數(shù)?

設(shè)置Vivado壓縮BIT文件的兩種方法

Vivado的安裝生成bit文件及燒錄FPGA的簡要流程教程免費下載

淺談PCB設(shè)置自動布線的技巧

變頻器的參數(shù)設(shè)置及缺陷的處理

變頻器功能參數(shù)設(shè)置

變頻器參數(shù)設(shè)置

變頻器設(shè)置面板及參數(shù)設(shè)置方法

Vivado綜合參數(shù)設(shè)置

Vivado布線和生成bit參數(shù)設(shè)置

Vivado布線和生成bit參數(shù)設(shè)置

評論