數字門級電路可分為兩大類:組合邏輯和時序邏輯。鎖存器是組合邏輯和時序邏輯的一個交叉點,在后面會作為單獨的主題處理。

組合邏輯描述了門級電路,其中邏輯塊的輸出直接反映到該塊的輸入值的組合,例如,雙輸入AND門的輸出是兩個輸入的邏輯與。如果輸入值發生變化,輸出值將反映這一變化,組合邏輯的RTL模型需要反映這種門級行為,這意味著邏輯塊的輸出必須始終反映該邏輯塊當前輸入值的組合。

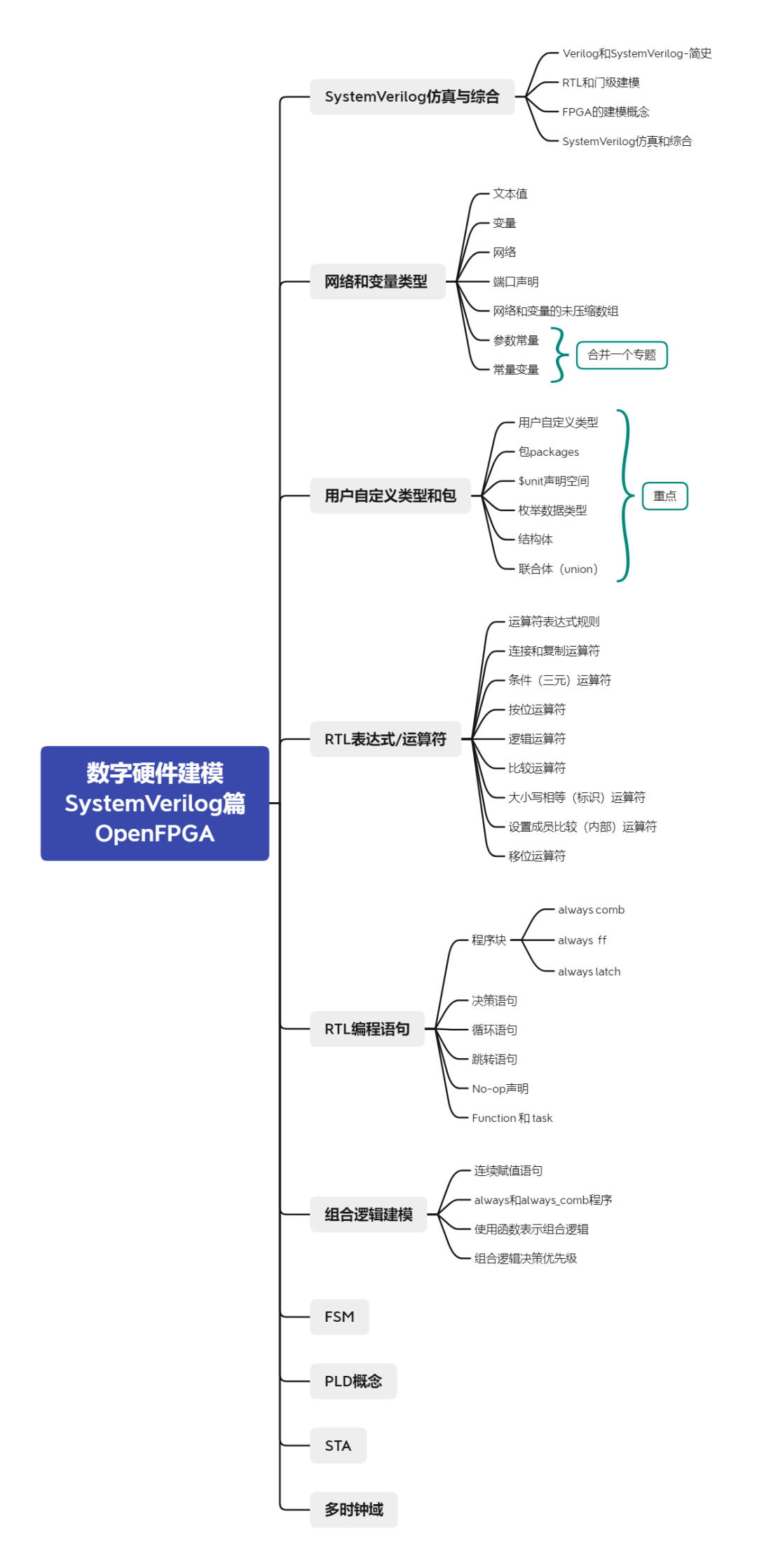

SystemVerilog有三種在可綜合RTL級別表示組合邏輯的方法:連續賦值語句、always程序塊和函數。接下來幾篇文章將探討每種編碼風格,并推薦最佳實踐編碼風格。

時序邏輯概念

時序邏輯描述了一種重要的門級電路,其中輸出反映了一個由門的內部狀態存儲的值。只有特定的輸入變化,如時鐘沿,才會導致存儲的變化。對于D觸發器,時鐘輸入的特定邊沿將改變觸發器的存儲,但D輸入值的變化并不直接改變存儲。相反,特定的時鐘沿會使觸發器的內部存儲更新為時鐘沿的D輸入值。

時序邏輯的RTL模型需要反映這種門級行為,也就是說,邏輯塊的輸出必須在一個或多個時鐘周期內存儲一個值,并且只為特定的輸入變化而更新存儲的值,而不是所有輸入變化。在RTL層面,一個always或always_ff過程被用來模擬這種時序行為。本系列文章主要研究:

RTL時序邏輯的綜合要求

always_ff 時序邏輯建模

時序邏輯時鐘到Q的傳播和建立/保持時間

使用非阻塞賦值來模擬時鐘到Q的傳播效應

同步和異步復位

多個時鐘和時鐘域交叉(CDC)。

在時序邏輯RTL模型中使用單元延時

建立有限狀態機(FSM)模型

對Mealy和Moore FSM架構進行建模

狀態解碼器,并使用獨熱碼的獨特情況

對內存設備進行建模,如RAM

觸發器和寄存器的RTL模型

觸發器和寄存器被用來在一段時間內存儲信息。術語觸發器和寄存器經常被當作同義詞使用,盡管它們在加載和復位的方式上可能存在差異。觸發器是一種存儲元件,在時鐘沿上改變存儲的狀態。各種各樣的硬件應用都可以由觸發器構建,如計數器、數據寄存器、控制寄存器、移位寄存器和狀態寄存器。寄存器可以由任何類型的數據存儲設備構建,包括觸發器、鎖存器和RAM。大多數硬件寄存器是由觸發器建立的。

時序邏輯觸發器和寄存器的RTL模型是用一個帶有靈敏度列表的always或always_ff過程建模的,該過程使用時鐘邊沿來觸發過程的評估。一個RTL觸發器的例子是:

一般來說,RTL模型被寫成在時鐘輸入的正邊沿觸發觸發器。所有的ASIC和FPGA器件都支持在時鐘的上升沿(正邊沿)觸發的觸發器。一些ASIC或FPGA器件還支持在時鐘的下降沿觸發的觸發器。觸發器和由觸發器組成的寄存器可以是不可復位或可復位的。復位可以是同步的,也可以是與時鐘觸發不同步的。一些觸發器也有一個異步復位輸入。

在門級設計中,有幾種類型的觸發器,例如。SR, D,JK和T觸發器。RTL模型可以從這個實現細節中抽象出來,并被寫成通用的觸發器。

在RTL建模中,重點是設計功能,而不是設計實現。綜合編譯器的作用是將抽象的RTL功能描述映射到具體的門級實現。大多數ASIC和FPGA器件使用D型觸發器,所以本文假設綜合編譯器從RTL觸發器中推斷出的觸發器類型。

RTL時序邏輯的綜合要求

當always程序的敏感度列表包含關鍵字posedge或negedge時,綜合編譯器將嘗試推斷出一個觸發器。然而,綜合編譯器還要求滿足以下額外的代碼限制,以便推斷出一個觸發器。

程序靈敏度列表必須指定時鐘的哪個邊沿觸發更新觸發器的狀態(posedge或negedge)。

靈敏度列表必須指定任何異步設置或復位信號的前緣(posedge或negedge)(同步設置或復位不在靈敏度列表中列出)。

除了時鐘、異步設置或異步復位外,靈敏度列表不能包含任何其他信號,如D輸入或使能輸入。

該過程應該在零仿真時間內執行。綜合編譯器會忽略#延遲,并且不允許@或等待時間控制。這條規則的一個例外是使用分配單元內的延遲(后續詳解)。

在時序邏輯程序中賦值的變量不能被任何其他程序或連續賦值所賦值(允許在同一程序中多次賦值)。

在一個時序邏輯程序中,一個被賦值的變量不能有阻塞和非阻塞的混合賦值。例如,復位分支不能用阻塞賦值建模,而時鐘分支則用非阻塞賦值建模。

審核編輯:劉清

-

RAM

+關注

關注

8文章

1391瀏覽量

116782 -

RTL

+關注

關注

1文章

388瀏覽量

60663 -

觸發器

+關注

關注

14文章

2032瀏覽量

61875 -

時序邏輯

+關注

關注

0文章

39瀏覽量

9340 -

門級電路

+關注

關注

0文章

15瀏覽量

2045

原文標題:數字硬件建模SystemVerilog-時序邏輯建模(1)RTL時序邏輯的綜合要求

文章出處:【微信號:Open_FPGA,微信公眾號:OpenFPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

RTL時序邏輯的綜合要求

RTL時序邏輯的綜合要求

評論