1.邏輯綜合

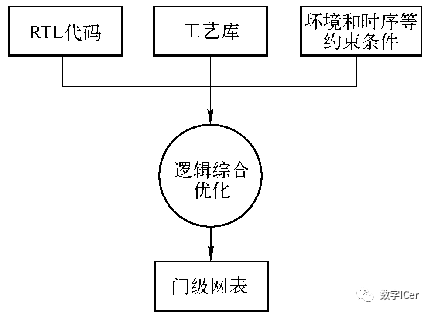

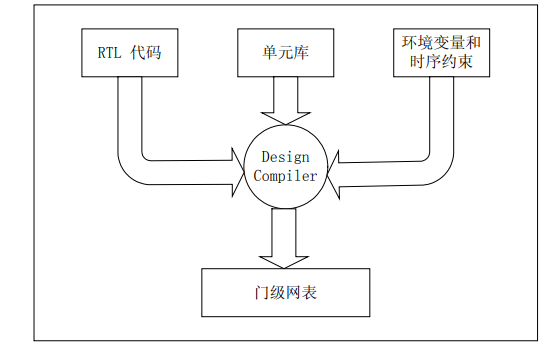

利用工具將RTL代碼轉(zhuǎn)化為門(mén)級(jí)網(wǎng)表的過(guò)程稱為邏輯綜合。綜合一個(gè)設(shè)計(jì)的過(guò)程,從讀取RTL代碼開(kāi)始,通過(guò)時(shí)序約束關(guān)系,映射產(chǎn)生一個(gè)門(mén)級(jí)網(wǎng)表。

1 流程介紹

1.用硬件描述語(yǔ)言進(jìn)行設(shè)計(jì)

讀入的設(shè)計(jì),通常是采用硬件描述語(yǔ)言(HDL)編寫(xiě)的,如Verilog和VHDL。

2.指定工藝庫(kù)

在根據(jù)約束條件進(jìn)行邏輯綜合時(shí),對(duì)于選擇的流片工藝,工藝庫(kù)將提供綜合工具所需要的標(biāo)準(zhǔn)單元的全部信息,即工藝庫(kù)含有特定工藝下的標(biāo)準(zhǔn)單元的邏輯功能、單元的面積、輸入到輸出的時(shí)序關(guān)系、輸出的扇出限制和對(duì)單元時(shí)序檢查所需的信息等。

3.讀入設(shè)計(jì)

把HDL描述的設(shè)計(jì),即RTL代碼輸入給綜合工具,由綜合工具進(jìn)行編譯,綜合工具在綜合時(shí)會(huì)首先檢查代碼的可綜合性。

4.定義環(huán)境約束條件

定義本設(shè)計(jì)要綜合時(shí)的環(huán)境,包括設(shè)計(jì)的工藝參數(shù)(溫度、制造工藝、電壓)、I/O端口屬性等。

5.設(shè)定設(shè)計(jì)的約束條件

約束條件將指定綜合工具按照什么樣的原則來(lái)綜合電路,該電路所要達(dá)到的指標(biāo)是什么。

2 定義時(shí)鐘

定義芯片所需的內(nèi)部時(shí)鐘信號(hào)。

通常時(shí)鐘網(wǎng)絡(luò)在綜合過(guò)程中是不做處理的,會(huì)在后續(xù)的布局布線中插入時(shí)鐘樹(shù),減小其時(shí)鐘偏斜。

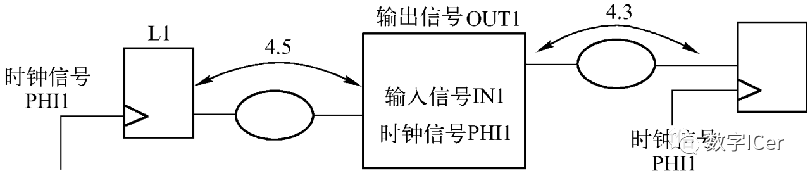

輸入/輸出延時(shí)

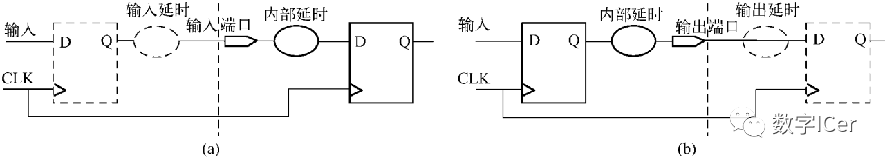

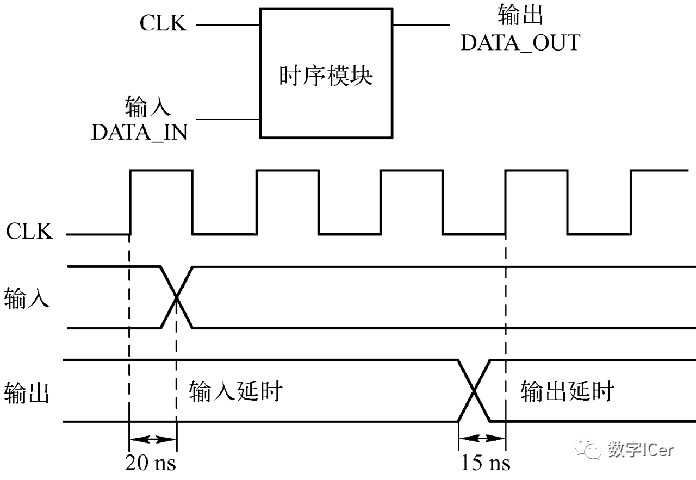

為保證片外的觸發(fā)器可以正確地輸入/輸出,不僅要保證片內(nèi)的延時(shí)要滿足時(shí)序要求,而且要保證片內(nèi)外延時(shí)總和要滿足時(shí)序要求 。

輸入/輸出延時(shí)示意

輸入/輸出延時(shí)示意

3 設(shè)定設(shè)計(jì)規(guī)則約束

設(shè)定設(shè)計(jì)規(guī)則約束包括節(jié)點(diǎn)上信號(hào)最大跳變時(shí)間(Max Transition)、最大扇出(Max Fanout)、最大電容(Max Capacitance)等。合理的設(shè)定這些約束條件將有利于控制功耗,保證信號(hào)完整性。

這3個(gè)約束可以設(shè)置在輸入端口、輸出端口及當(dāng)前設(shè)計(jì)上。通常這些約束在工藝庫(kù)內(nèi)已經(jīng)設(shè)定,由工藝參數(shù)決定大小。如果庫(kù)內(nèi)設(shè)定的值不夠恰當(dāng)或者過(guò)于樂(lè)觀,可以根據(jù)設(shè)計(jì)需要專門(mén)設(shè)置。

4 面積約束

面積約束是指定設(shè)計(jì)的最大面積值,如果設(shè)計(jì)超過(guò)了這一面積就違反了約束。

在將設(shè)計(jì)實(shí)體轉(zhuǎn)換成門(mén)級(jí)電路時(shí),通常要加面積約束條件。這一設(shè)計(jì)指標(biāo),也是邏輯綜合過(guò)程中進(jìn)行優(yōu)化的依據(jù)之一。多數(shù)的邏輯綜合工具允許設(shè)計(jì)者按工藝庫(kù)中門(mén)級(jí)宏單元所用的單位來(lái)指定面積的約束條件。

5 優(yōu)化設(shè)計(jì)

優(yōu)化的主要目的是在滿足時(shí)序要求的前提下盡量減小芯片面積。與工藝無(wú)關(guān)的優(yōu)化缺乏非常準(zhǔn)確的時(shí)序信息,因而注意力往往集中在優(yōu)化面積上。等到映射之后時(shí)序信息比較準(zhǔn)確時(shí)再進(jìn)行修正更有效。

架構(gòu)優(yōu)化:如選擇DesignWare實(shí)現(xiàn)所需功能等。

邏輯優(yōu)化:重構(gòu)(優(yōu)化面積)與展平(優(yōu)化速度)。

門(mén)級(jí)優(yōu)化:映射、延時(shí)優(yōu)化、設(shè)計(jì)規(guī)則修正、面積優(yōu)化。

SoC設(shè)計(jì)中常用的綜合策略

有兩種基本的綜合策略可以選擇,即自頂向下(Top-down)與自底向上(Bottom-up)。

在自頂向下綜合策略里,頂層設(shè)計(jì)與其子模塊同時(shí)編譯,僅需要施加頂層約束。

自底向上的綜合策略是指先單獨(dú)地對(duì)各個(gè)子模塊進(jìn)行約束與綜合,完成后,賦予它們不再優(yōu)化(Dont_touch)屬性,將它們整合到上一層模塊中,進(jìn)行綜合,重復(fù)這一過(guò)程,直至綜合最頂層的模塊。

2.物理綜合

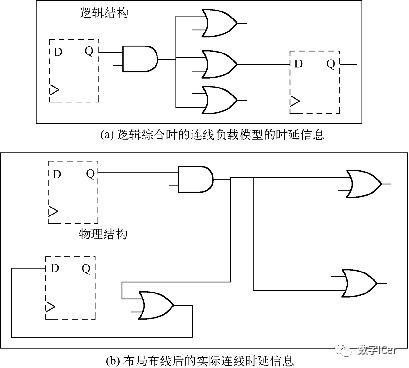

傳統(tǒng)的邏輯綜合方法是依賴于連線負(fù)載模型(Wire-load Model)的,隨著工藝尺寸的不斷縮小及芯片復(fù)雜性的增加,整個(gè)電路的延時(shí)信息更多取決于互連線延時(shí)。

在物理綜合時(shí),就考慮布局布線的問(wèn)題了。

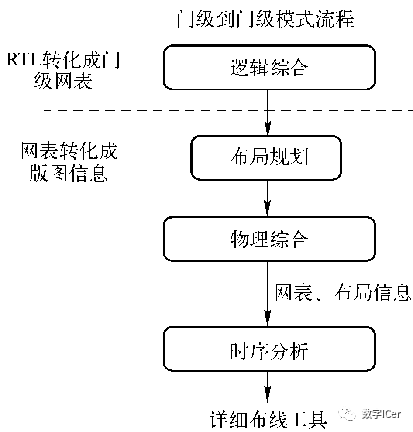

操作模式

物理綜合要求的約束條件通常有芯片尺寸、引腳位置、線上負(fù)載信息、版圖規(guī)劃信息等。一般使用以下兩種操作模式。

RTL到門(mén)級(jí)模式:在RTL到門(mén)級(jí)模式下,物理綜合的輸入信息是RTL級(jí)的設(shè)計(jì)電路、版圖規(guī)劃信息及含有版圖信息的物理綜合的庫(kù)文件。

門(mén)級(jí)到布局后門(mén)級(jí)模式 :在這一模式下,與RTL到門(mén)級(jí)模式的唯一區(qū)別是物理綜合的輸入信息是門(mén)級(jí)網(wǎng)表,而不是RTL級(jí)的設(shè)計(jì)電路。

相對(duì)而言,RTL到門(mén)級(jí)模式所花費(fèi)的時(shí)間要比門(mén)級(jí)到門(mén)級(jí)模式的時(shí)間長(zhǎng)。

物理綜合的流程圖

物理綜合的流程圖

更多請(qǐng)查看 :綜合與時(shí)序分析

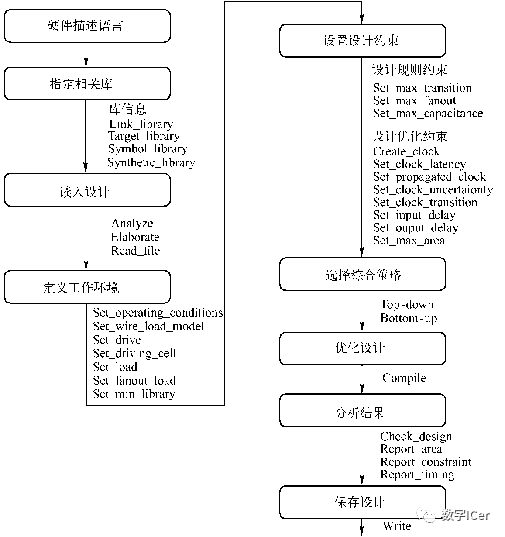

實(shí)例:用Design Compiler 進(jìn)行邏輯綜合

在綜合的各個(gè)步驟中所經(jīng)常用到的命令

在綜合的各個(gè)步驟中所經(jīng)常用到的命令

(1)指定庫(kù)文件

在綜合之前,需要用一個(gè)名為“.synopsys_dc.setup”的初始化文件建立綜合的環(huán)境。在該文件中,通過(guò)向相關(guān)環(huán)境變量賦值,來(lái)定義工藝庫(kù)的位置及綜合所需要的參數(shù)。

synopsys的安裝目錄下:對(duì)于UNIX系統(tǒng)來(lái)說(shuō),它通常位于“$SYNOPSYS/admin/setup”目錄下。用于卸載synopsys工藝獨(dú)立庫(kù)及別的參數(shù),不包含設(shè)計(jì)相關(guān)的數(shù)據(jù)。

用戶根目錄下:這里的setup文件包含用戶對(duì)于自己DC工作環(huán)境的參數(shù)設(shè)置。

啟動(dòng)DC的當(dāng)前目錄:這里的setup文件包含因項(xiàng)目與設(shè)計(jì)而異的變量設(shè)置。

Setup文件的內(nèi)容

search_path:由目錄列表組成。當(dāng)DC搜索某個(gè)未指定路徑的文件(如庫(kù)、設(shè)計(jì)文件等)時(shí),將由search_path中定義的路徑中去搜索該文件。通常將其定義為某個(gè)主要的庫(kù)文件所在的目錄路徑。

target_library:指定對(duì)設(shè)計(jì)進(jìn)行綜合時(shí)采用的工藝庫(kù),由廠家提供。該庫(kù)中的器件被DC用于邏輯映射。本變量指定的庫(kù)文件名,應(yīng)該也包含在link_library所列出的內(nèi)容中,用于供DC讀取門(mén)級(jí)網(wǎng)表。

link_library:該變量指定的庫(kù)文件中的器件將不會(huì)被DC用來(lái)進(jìn)行綜合,如RAM、ROM及I/O。在RTL設(shè)計(jì)中,將以實(shí)例化的方式進(jìn)行引用。

symbol_library:該變量指定的庫(kù)文件包含有工藝庫(kù)中器件的圖形化信息,用于生成圖形化原理圖。

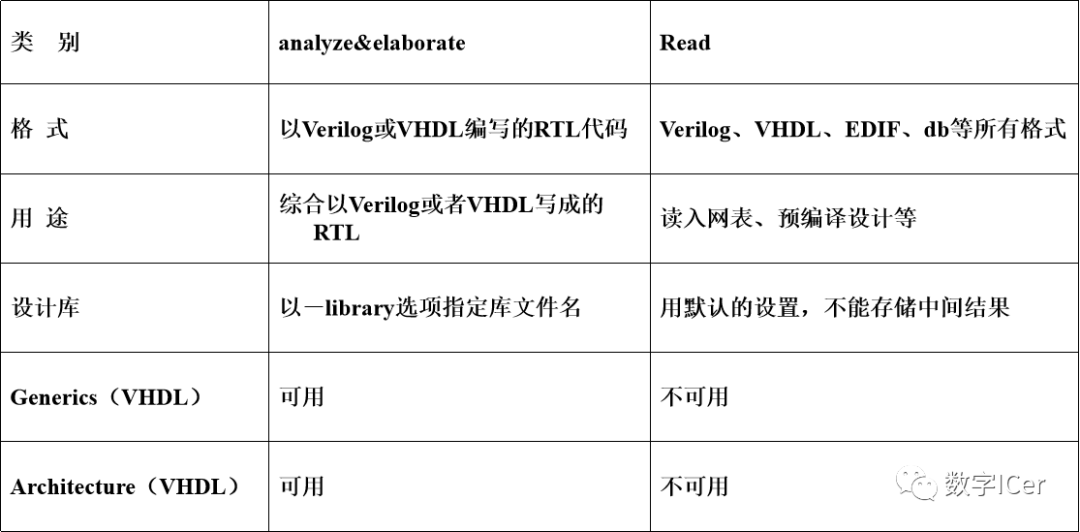

(2)讀入設(shè)計(jì)

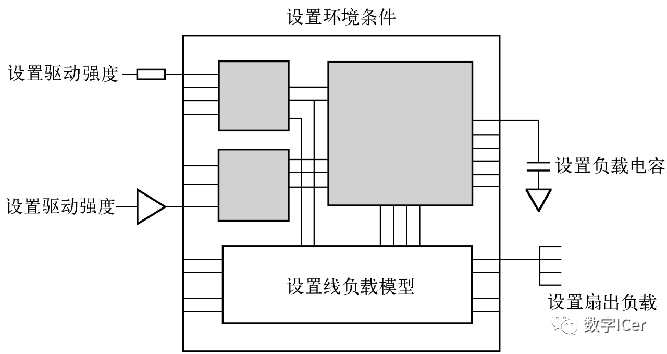

(3)定義工作環(huán)境

設(shè)置環(huán)境條件(set_operating_conditions)

設(shè)置線負(fù)載模型(set_wire_load_model)

設(shè)置驅(qū)動(dòng)強(qiáng)度(set_drive與set_driving_cell)

設(shè)置電容負(fù)載

設(shè)置扇出負(fù)載(set_fanout_load)

(4)設(shè)置約束條件

設(shè)置設(shè)計(jì)規(guī)則約束(set_max_transition、set_max_fanout、set_max_capacitance)

例如:set_max_transition 0.3 current_design

例如:set_max_capacitance 1.5[get_ports out1]

例如:set_max_fanout 3.0[all_outputs]

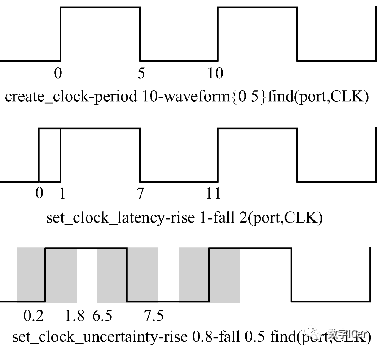

時(shí)鐘定義的相關(guān)命令

create_clock用來(lái)定義一個(gè)時(shí)鐘的周期和波形

set_clock_latency定義時(shí)鐘網(wǎng)絡(luò)的延時(shí)

set_clock_uncertainty定義時(shí)鐘偏斜值

時(shí)鐘定義

create_generated_clock定義一個(gè)內(nèi)部生成的時(shí)鐘。可以將內(nèi)部分頻或者倍頻產(chǎn)生的時(shí)鐘定義為初級(jí)時(shí)鐘的函數(shù)。

例如:create_generated_clock -name GENCLK -source CLKIN -divide_by 2[get_pins idiv/ div_reg/Q]

對(duì)于只含有組合邏輯的模塊,為了定義該模塊的延時(shí)約束,可以創(chuàng)建一個(gè)虛擬時(shí)鐘,再相對(duì)于虛擬時(shí)鐘定義輸入/輸出延時(shí)。

設(shè)置輸入/輸出端口的延時(shí)

輸入延時(shí)定義了信號(hào)相對(duì)于時(shí)鐘的到達(dá)時(shí)間,指一個(gè)信號(hào)在時(shí)鐘沿之后多少時(shí)間到達(dá)。

輸出延時(shí)則定義輸出信號(hào)相對(duì)于時(shí)鐘所需要的到達(dá)時(shí)間,指一個(gè)信號(hào)在時(shí)鐘沿之前多少時(shí)間輸出。

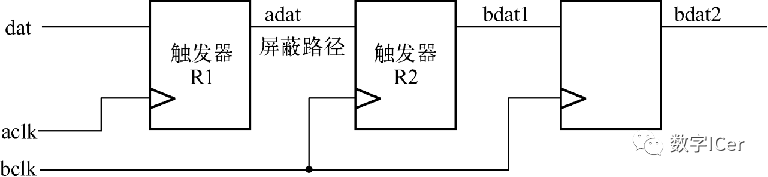

特別路徑的約束

虛假路徑(set_false_path)是指由于邏輯功能、數(shù)據(jù)順序或操作模式等原因,從來(lái)不會(huì)激活或者不需要考慮的路徑。

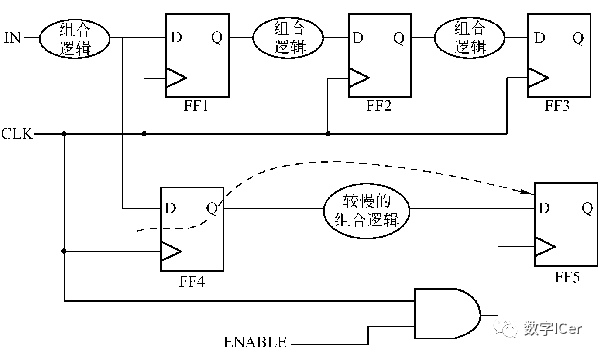

設(shè)置多周期路徑

設(shè)置多周期路徑(set_multicycle_path),指設(shè)計(jì)中從發(fā)送數(shù)據(jù)到采樣到數(shù)據(jù)的時(shí)間允許多于一個(gè)時(shí)鐘周期的路徑。虛線標(biāo)出了多周期路徑。

(5)設(shè)定綜合優(yōu)化策略

通過(guò)使用compile命令調(diào)用DC,對(duì)設(shè)計(jì)進(jìn)行綜合與優(yōu)化。該命令有許多選項(xiàng)可以選擇,其中,映射努力(map_effort)即要求工具優(yōu)化的程度,可以設(shè)置為低、中、高。

在初次編譯時(shí),如果需要對(duì)整個(gè)設(shè)計(jì)的性能和面積等有一個(gè)大致的了解,可以將map_effort設(shè)置為低。默認(rèn)的map_effort級(jí)別為中,而在最后一次編譯中,可以將map_effort設(shè)置為高。通常,將map_effort設(shè)置為中即可。

審核編輯:湯梓紅

-

物理綜合

+關(guān)注

關(guān)注

0文章

3瀏覽量

6589 -

RTL

+關(guān)注

關(guān)注

1文章

388瀏覽量

60634 -

觸發(fā)器

+關(guān)注

關(guān)注

14文章

2032瀏覽量

61852

原文標(biāo)題:邏輯綜合與物理綜合

文章出處:【微信號(hào):數(shù)字ICer,微信公眾號(hào):數(shù)字ICer】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

淺談IC設(shè)計(jì)中邏輯綜合

物理綜合與優(yōu)化的優(yōu)點(diǎn)有哪些?流程是怎樣的?

請(qǐng)問(wèn)如何通過(guò)物理綜合與優(yōu)化去提升設(shè)計(jì)性能?

如何使用DCNXT實(shí)現(xiàn)物理綜合?

DC邏輯綜合詳解

Tcl與Design Compiler (八)——DC的邏輯綜合與優(yōu)化 精選資料分享

DC邏輯綜合

ASIC邏輯綜合及Synopsys Design Compiler 的使用資料說(shuō)明

芯片設(shè)計(jì)之邏輯綜合過(guò)程

EDA邏輯綜合概念 邏輯綜合三個(gè)步驟

什么是邏輯綜合?邏輯綜合的流程有哪些?

邏輯綜合與物理綜合

邏輯綜合與物理綜合

評(píng)論