鍺硅(SiGe)外延(p-MOS源漏)

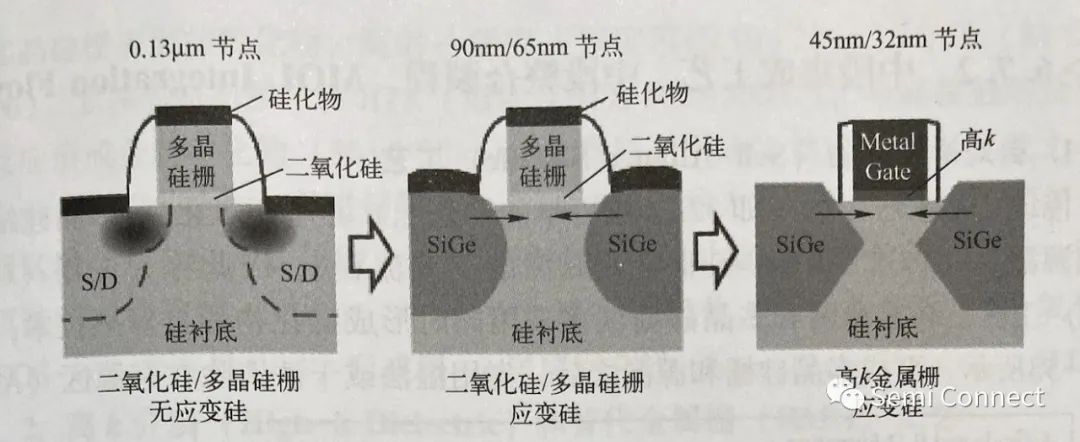

自 32 nm節點以來,CMOS 器件結構已從多晶硅柵(如硅氧化/多晶硅結構)和非應變源漏結構演變到利用高k柵介質/金屬柵 (high-k/ Metal-Gate, HKMG)和應變硅源漏,如圖所示。

其制造工藝流程如下:首先形成補償側墻(Offset Spacer),經n+/p+輕摻雜源漏后,選擇性地進行圖形化,在p型源漏區先進行干法刻蝕,使其凹陷適當的深度(30~100nm);然后采用濕法各向異性刻蝕形成“鉆石”形腔(Diamond Cavity,又稱“∑”形狀);接著外延鍺硅(SiGe)形成p-MOS 的源漏,p型摻雜可由原位硼摻雜或硼離子注入和快速熱退火(RTA) 來形成。p型源漏的鉆石形鍺硅面向溝道的鄰近尖點(DiamondTip),可有效地增強沿溝道方向的壓應力,因此也增強了溝道空穴遷移率。

審核編輯 :李倩

-

CMOS

+關注

關注

58文章

5978瀏覽量

238006 -

晶硅

+關注

關注

1文章

51瀏覽量

22900

原文標題:前段集成工藝(FEOL)- 6

文章出處:【微信號:Semi Connect,微信公眾號:Semi Connect】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

概倫電子集成電路工藝與設計驗證評估平臺ME-Pro介紹

集成電路工藝中的金屬介紹

集成電路新突破:HKMG工藝引領性能革命

大馬士革銅互連工藝詳解

芯片封裝工藝集成工程師的必修課程指南

晶合集成28納米邏輯工藝通過驗證

集成電路工藝學習之路:從零基礎到專業水平的蛻變

前段集成工藝(FEOL)

前段集成工藝(FEOL)

評論