作者:Pablo Perez, Jr. and John Martin Dela Cruz

本信號鏈功率優化系列的第1部分討論了如何量化電源噪聲,以確定其影響的信號鏈器件參數。通過確定信號處理設備可以接受的實際噪聲限制,可以創建優化的配電網絡(PDN),而不會影響其產生的信號的完整性。在第2部分中,該方法應用于高速模數和數模轉換器,表明將噪聲降低到必要的水平并不總是等同于更高的成本、更大的尺寸和更低的效率。實際上,這些設計參數可以在一個優化的電源解決方案中得到滿足。

本文重點介紹信號鏈的另一部分——RF收發器。在這里,我們檢查設備對來自每個電源軌的噪聲的靈敏度,以確定哪些需要額外的噪聲過濾。本文提供了一種優化的電源解決方案,通過將其SFDR和相位噪聲性能與連接到RF收發器時的電流PDN進行比較,進一步驗證了該解決方案。

優化ADRV9009 6 GHz雙通道RF收發器的電源系統

ADRV9009是一款高度集成的射頻(RF)捷變收發器,提供雙發射器和接收器、集成頻率合成器和數字信號處理功能。該 IC 提供高性能和低功耗的多功能組合,可滿足 3G、4G 和 5G 宏蜂窩時分雙工 (TDD) 基站應用的需求。

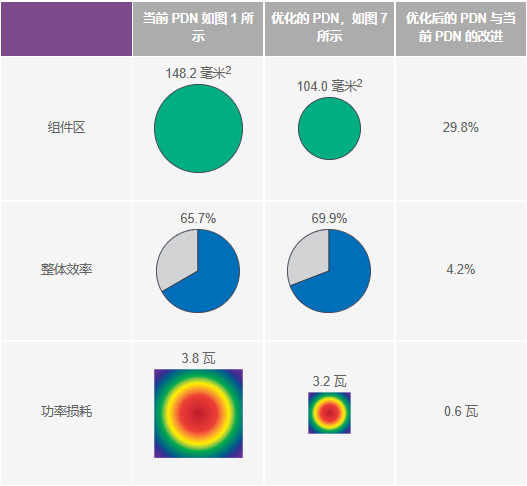

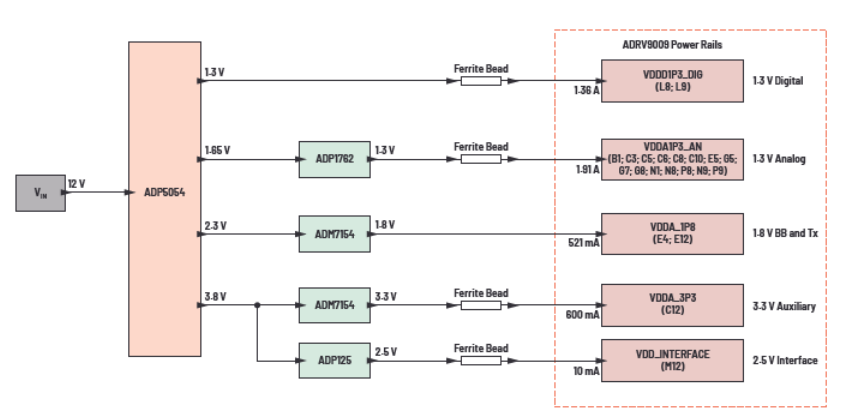

圖1.用于ADRV9009雙通道收發器的標準評估板配電網絡。此設置使用帶有四個LDO后置穩壓器的ADP5054四通道穩壓器,以滿足噪聲規格并最大限度地提高收發器的性能。目標是改進此解決方案。

圖1所示為雙通道收發器ADRV9009的標準PDN。PDN由一個ADP5054四通道開關穩壓器和四個線性穩壓器組成。這里的目標是了解配電網絡的哪些性能參數可以改進,同時產生不會降低收發器性能的噪聲。

如本系列1、2所示,量化ADRV9009對電源噪聲的靈敏度對于優化PDN是必要的。ADRV9009 6 GHz雙通道RF收發器需要五種不同的電源軌,即:

1.3 V 模擬 (VDDA1P3_AN)

1.3 V 數字 (VDDD1P3_DIG)

1.8 V 發射器和 BB (VDDA_1P8)

2.5 V 接口 (VDD_INTERFACE)

3.3 V 輔助 (VDDA_3P3)

分析

圖 2 顯示了模擬電源軌(VDDA1P3_AN、VDDA_1P8 和VDDA_3P3)的接收器 1 端口 PSMR 結果。對于數字電源軌(VDDD1P3_DIG和VDD_INTERFACE),我們用信號發生器可以產生的最大注入紋波不會在輸出頻譜中產生雜散,因此我們無需擔心最小化這些電源軌上的紋波。調制雜散幅度以dBFS表示,其中最大輸出功率(0 dBFS)相當于50 Ω系統中的7 dBm或1415.89 mV p-p。

圖2.接收器1處ADRV9009收發器模擬電源軌的PSMR性能。

對于VDDA1P3_AN軌,測量是在收發器板的兩個不同分支上進行的。請注意,在圖2中,PSMR在<200 kHz紋波頻率下降至0 dB以下,表明這些頻率下的紋波在相同幅度下會產生更高的調制雜散。這意味著在低于200 kHz時,接收器1對VDDA1P3_AN軌產生的最小紋波也非常敏感。

VDDA_1P8軌在收發器板中分為兩個分支:VDDA1P8_TX和VDDA1P8_BB。VDDA1P8_TX軌在 ~27 dB 附近達到 100 kHz 時的最小 PSMR,對應于 100 kHz 紋波的 63.25 mV p-p,從而產生 2.77 mV p-p 的調制雜散。VDDA1P8_BB在5 MHz紋波頻率下測量的最小值為~11 dB,相當于0.136 mV p-p注入紋波產生的0.038 mV p-p雜散。

VDDA_3P3數據顯示,在大約130 kHz及以下時,PSMR低于0 dB,這表明接收器1的RF信號對來自VDDA_3P3的噪聲非常敏感。該電源軌的PSMR隨著頻率的增加而上升,在5 MHz時高達72.5 dB。

總之,PSMR結果表明,在電源軌中,VDDA1P3_AN軌和VDDA_3P3軌噪聲最令人擔憂,對耦合到ADRV9009收發器接收器1的紋波成分貢獻最大。

圖3.接收器1處ADRV9009收發器模擬電源軌的PSRR性能。

圖3顯示了ADRV9009在模擬電源軌下的PSRR性能。VDDA1P3_AN的PSRR在1 MHz時為~60 dB平坦,在5 MHz時略微下降至~46 dB。這可以看作是5 MHz紋波的0.127 mV p-p,與調制RF信號一起產生0.001 mV p-p雜散。

ADRV9009 VDDA1P8_BB軌的PSRR在5 MHz時觸底為~47 dB,而VDDA1P8_TX軌的PSRR不會低于~80 dB。在低于1 MHz的頻譜中,VDDA_3P3的PSRR高于所示的90 dB。測量被削波在90 dB,因為高達1 MHz的最大注入紋波為20 mV p-p,不足以產生高于本振本底噪聲的雜散。該電源軌的PSRR高于1 MHz以下顯示的值,隨著頻率的增加,它在4 MHz時降至76.8 dB,這是10 kHz至10 MHz范圍內的最低值。

與PSMR結果類似,PSRR數據顯示,耦合到本振頻率的大部分噪聲,特別是高于1 MHz的噪聲,來自VDDA1P3_AN軌和VDDA_3P3軌。

為了確定電源是否滿足噪聲要求,測量直流電源的紋波輸出,從而在100 Hz至100 MHz頻率范圍內繪制波形,如圖4所示。在此頻譜中,增加了一個疊加層:邊帶雜散將在調制信號中出現的閾值。疊加數據是通過在幾個參考點將正弦紋波注入指定的電源軌獲得的,以查看產生邊帶雜散的紋波水平,如本系列第1部分所述。

圖4至圖6所示的閾值數據適用于收發器最敏感的三個電源軌。顯示了各種DC-DC轉換器配置的電源軌頻譜,啟用和不啟用擴頻頻率調制(SSFM)或通過LDO穩壓器或低通(LC)濾波器進行額外濾波。這些波形在電源板上測量,以便為大于或等于低于噪聲限值6 dB的額外裕量留出空間。

圖4.為VDDA1P3_AN軌供電的 LTM8063 (各種配置) 的輸出噪聲頻譜,以及該供電軌的最大允許紋波。

測試

圖 4 示出了 LTM8063 μModule 穩壓器的各種配置的VDDA1P3_AN軌的雜散門限以及測得的噪聲頻譜。如圖 4 所示,使用 LTM8063 直接為電源軌供電并禁用擴頻頻率調制 (SSFM) 時,會在 LTM8063 的基波工作頻率處產生紋波,并產生超過門限的諧波。特別是,紋波在1.1 MHz時超出限值0.57 mV,表明需要后置穩壓器和濾波器的某種組合來抑制來自開關穩壓器的噪聲。?

如果僅添加一個LC濾波器(無LDO穩壓器),則開關頻率處的紋波剛好達到最大允許紋波,可能沒有足夠的設計裕量來確保收發器的最佳性能。添加一個 ADP1764 LDO 后置穩壓器并開啟 LTM8063 的擴頻模式可降低整個頻譜內的基波開關紋波幅度及其諧波,并降低 1/f 區域 SSFM 引起的噪聲峰值。通過打開SSFM并添加LDO穩壓器和LC濾波器,可以降低開關動作引起的剩余噪聲,從而從最大允許紋波中留下~18 dB裕量,從而獲得最佳結果。

擴頻調頻在更寬的頻帶上傳播噪聲,從而降低開關頻率及其諧波處的峰值和平均噪聲。這是通過3 kHz三角波上下調制開關頻率來實現的。這在3 kHz處引入了新的紋波,由LDO穩壓器處理。

當SSFM使能時,產生的低頻紋波及其諧波在圖5和圖6所示的VDDA_1P8和VDDA_3P3輸出頻譜中分別很明顯。如圖5所示,啟用SSFM的LTM8074的噪聲頻譜為VDDA_1P8軌的最大允許紋波提供最小~8 dB裕量。因此,無需后置穩壓器濾波即可滿足該電源軌的噪聲要求。

圖5.LTM8074 (SSFM 接通時) 為VDDA_1P8軌供電的輸出噪聲頻譜,以及該供電軌的最大允許紋波。

圖6.為VDDA_3P3軌供電的 LTM8074 (在各種配置中) 的輸出噪聲頻譜,以及該供電軌的最大允許紋波。請注意,電源軌對低頻紋波的敏感性,因為這種噪聲可能會在3.3 V供電時鐘中引起相位抖動。

圖6顯示了LTM8074 μModule穩壓器各種配置的噪聲頻譜,以及3.3 V VDDA_3P3軌的最大噪聲要求。對于該電源軌,我們將使用 LTM8074 靜音開關器 μModule 穩壓器來檢查結果。僅 LTM8074 配置(無濾波器或 LDO 后置穩壓器)會產生超過限值的噪聲,無論擴頻模式是使能還是禁用。?

兩種替代配置的結果符合噪聲規格,裕量為>6 dB:未使能SSFM的LTM8074加上一個LC濾波器,以及帶LDO后置穩壓器的SSFM啟用的LTM8074。雖然兩者都滿足了足夠裕量的要求,但LDO后置穩壓器解決方案在這方面具有優勢。這是因為VDDA_3P3軌還提供3P3V_CLK1時鐘電源,因此降低1/f噪聲相對更重要,因為如果不加以解決,這里的噪聲可能會轉化為本振中的相位抖動。

圖7.一款針對采用LTM8063和LTM8074 μModule穩壓器的ADRV9009收發器的優化PDN。

優化的解決方案

根據上述測試結果,圖7顯示了一種優化的解決方案,在ADRV9009收發器板上使用時,可提供>6 dB的噪聲容限。

表 1 顯示了優化后的 PDN 與標準 PDN 的比較。組件面積減少29.8%,效率從65.7%提高到69.9%,整體節能0.6W。

為了驗證這種優化電源解決方案在系統噪聲性能方面的功效,我們進行了相位噪聲測量。圖7中的優化解決方案與控制案例進行了比較,控制案例是ADRV9009評估板的工程發布版本,即使用圖1所示PDN的AD9378評估板。使用相同的電路板,但使用PDN,如圖7所示,并比較了相位噪聲結果。理想情況下,優化的解決方案滿足或超過數據手冊參考圖。

圖8.AD9378在LO = 1900 MHz、PLL帶寬 = 425 kHz、穩定性= 8時,ADP5054與μModule器件的PSU之間的相位噪聲性能比較。

圖8顯示了采用基于標準ADP5054電源的AD9378評估板的相位噪聲結果與使用基于LTM8063和LTM8074的電源的同一評估板的相位噪聲結果的比較。μModule電源解決方案的性能略好,約為2 dB,優于ADP5054電源解決方案。如圖8和表2所示,由于外部本振使用了低相位噪聲信號發生器,兩種電源解決方案的測量結果明顯低于數據手冊規格。

| 偏移頻率(兆赫) | 相位噪聲 (dBc/Hz) | ||

| 數據表規格 | 評價結果 | ||

| ADP5054 | LTM8063 和 LTM8074 | ||

| 0.1 | ?100 | ?137.74 | ?137.77 |

| 0.2 | ?115 | ?143.16 | ?143.32 |

| 0.4 | ?120 | ?147.37 | ?147.20 |

| 0.6 | ?129 | ?149.02 | ?149.04 |

| 0.8 | ?132 | ?151.81 | ?151.96 |

| 1.2 | ?135 | ?151.73 | ?151.22 |

| 1.8 | ?140 | ?153.97 | ?153.76 |

| 6 | ?150 | ?155.10 | ?154.80 |

| 10 | ?153 | ?154.51 | ?154.36 |

使用兩種電源解決方案的收發器SFDR測量結果(如表3所示)顯示了兩種電源解決方案的性能相當,但LO = 3800 MHz除外,其中ADP5054的開關紋波開始在載波信號輸出頻譜上產生調制雜散,如圖9所示。

| LO 頻率 (兆赫) | SFDR (dBc) | ||||

| 數據表規格 | Tx1 | Tx2 | |||

| ADP5054 | LTM8063 和 LTM8074 | ADP5054 | LTM8063 和 LTM8074 | ||

| 800 | 70.00 | 86.03 | 86.95 | 86.62 | 86.63 |

| 1800 | 70.00 | 85.94 | 87.30 | 86.01 | 85.90 |

| 2600 | 70.00 | 85.98 | 86.01 | 85.50 | 85.78 |

| 3800 | 70.00 | 73.87 | 77.42 | 73.93 | 77.31 |

| 4800 | 70.00 | 71.44 | 71.98 | 71.10 | 71.82 |

圖9.變送器1載波信號和雜散頻率是由于電源開關頻率引起的。測量是在LO = 3800 MHz,Fbb = 7 MHz,–10 dBm下進行的。

結論

不同應用的不同要求可能需要進一步改進或改變評估板的配電網絡。能夠量化信號處理IC的噪聲要求,為設計其電源甚至優化現有電源解決方案提供了一種更有效的方法。對于ADRV9009等高性能RF收發器,在PDN中設置噪聲注入以確定可容忍的電源噪聲量有助于我們在空間要求、效率以及關鍵的熱性能方面改善當前的PDN。請繼續關注此電源系統優化系列,了解后續條目。

審核編輯:郭婷

-

電源

+關注

關注

185文章

18283瀏覽量

255067 -

收發器

+關注

關注

10文章

3659瀏覽量

107414 -

RF收發器

+關注

關注

1文章

72瀏覽量

24806 -

RF

+關注

關注

65文章

3171瀏覽量

168527 -

電源開關

+關注

關注

12文章

1181瀏覽量

46151

發布評論請先 登錄

高度集成的MAX2830 RF收發器解決方案

優化信號鏈的電源系統 — 第3部分:RF收發器

XilinxVirtex?Ultrascale?FPGA多路千兆位收發器MGT電源解決方案

CC110L TI超值系列收發器

用于Xilinx Ultrascale Kintex FPGA多路千兆位收發器(MGT)的電源解決方案

基于nRF24L01P RF收發器的解決方案

Wi-Fi和RF捷變收發器在寬帶無線應用方面有哪些優缺點?

如何采用RF收發器實現體內通信系統的設計?

優化信號鏈的電源系統 — RF收發器

優化信號鏈的電源系統 — 第3部分:RF收發器

優化信號鏈的電源系統 — RF收發器

MAX2830 直接變頻RF收發器

新型RF收發器AT86RF233將用于電池供電的無線應用中

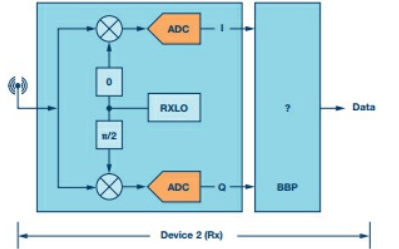

如何使用RF收發器實現簡單的基帶處理器

Ultrascale FPGA多路千兆位收發器電源解決方案

RF收發器實現優化電源的解決方案

RF收發器實現優化電源的解決方案

評論