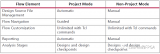

Vivado支持Project模式也支持Non-Project模式。兩者既可以支持圖形界面也支持Tcl命令,但用到的Tcl命令是不同的,不能混用。通常,Project模式應用更廣,便于初學者學習,同時也便于工程管理。Non-Project模式編譯時間會比Project模式短,因為所有數據存儲在內存,直接內存讀取數據比硬盤讀取要快一些。這里我們探討一下使用Non-Project模式時可能碰到的一些問題。

如何讀取SystemVerilog文件?

在Non-Project模式下,可以通過read_*命令將設計用到的文件添加到工程中,例如:read_verilog可讀取設計所需的Verilog文件(文件后綴為.v或.vh),當為.vh時,表明該文件為Verilog Header文件,在Non-Project模式下并不需要特別指明。但是如果讀取的是SystemVerilog文件(文件后綴為.sv)或者使用了SystemVerilog語法的Verilog文件時,就需要在read_verilog命令后添加選項-sv。

如何讀取VHDL-2008文件?

類似地,可以通過read_vhdl讀取設計所需的VHDL文件,文件后綴為.vhd。但如果VHDL文件使用了VHDL-2008語法,在使用該命令時就要添加選項-vhdl2008。

如何同時讀取多個同類型的設計源文件?

使用Non-Project模式時,通常建議將所有的待綜合的HDL文件無論是Verilog/VHDL/SystemVerilog放在同一個文件目錄下,例如放置在src/hdl目錄下,這樣可以方便地對同一類文件進行快速讀取。例如,讀取所有的VHDL文件可用如下命令,這里使用了Tcl命令glob,這種情況下該命令可返回所有的VHDL文件。如果要讀取所有的Verilog文件,就用glob ./src/hdl/*.v即可。 read_vhdl [glob ./src/hdl/*.vhd]

如何處理IP?

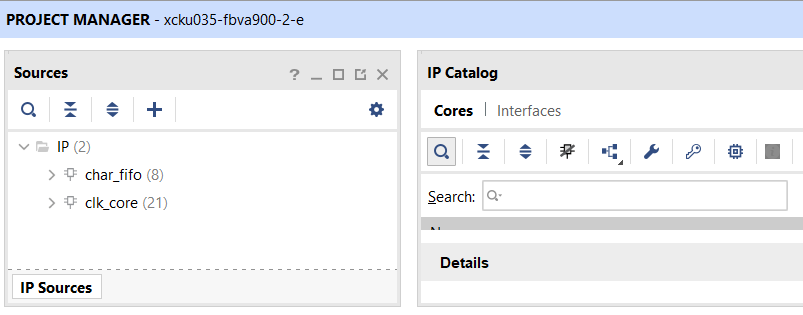

設計中我們不可避免地會用到IP,無論是Project模式還是Non-Project模式,都建議創建IP工程,以單獨管理IP,如下圖所示,這對于后續維護和升級IP都大有裨益。

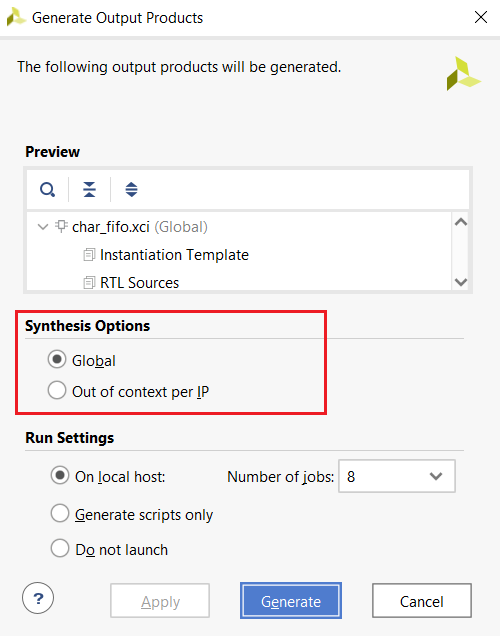

IP即可采用全局綜合方式,又可采用OOC綜合方式,這在生成IP輸出文件時就要確定,也只能在此界面確定而無法通過屬性修改,如下圖所示。

可以通過命令read_ip讀入IP,但該命令只能讀入.xci文件,并不會讀入預先生成的dcp文件。如果已在IP工程中完成了對IP的OOC綜合,那么無需在Non-Project模式下再次對IP進行綜合。否則,要先對IP通過命令synth_ip進行OOC綜合,此時要用到如下兩個命令。get_ips后也可跟隨具體的IP名稱。執行了synth_ip之后才可以對整個設計執行綜合。

generate_target all [get_ips]

synth_ip [get_ips] -force

在Non-Project模式下對IP通過synth_ip執行OOC綜合時,要先指定芯片型號,否則工具會按默認的芯片型號進行綜合。指定芯片型號要用set_part命令,如下所示:

set_part [get_parts xcku035-fbva900-2-e]

如何處理第三方綜合工具提供的網表文件?

審核編輯:湯梓紅

-

Verilog

+關注

關注

28文章

1365瀏覽量

111799 -

System

+關注

關注

0文章

166瀏覽量

37565 -

project

+關注

關注

0文章

35瀏覽量

13445 -

Vivado

+關注

關注

19文章

828瀏覽量

68206

原文標題:關于Vivado Non-project,我們應知道的…

文章出處:【微信號:Lauren_FPGA,微信公眾號:FPGA技術驛站】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

請教關于GAL的一些問題

關于H橋的一些問題?

VIVADO從此開始高亞軍編著

請教一些關于CC2541F256這顆芯片的一些問題

如何用Tcl實現Vivado設計流程介紹

VCS獨立仿真Vivado IP核的一些方法總結

Vivado設計流程指導手冊

關于Vivado Non-project,我們應知道的一些問題

關于Vivado Non-project,我們應知道的一些問題

評論