電子發燒友網報道(文/程文智)三星電子今年7月25日在韓國京畿道華城園區V1生產線(EUV專用)為采用了新一代全環繞柵極(Gate All Around,簡稱GAA)晶體管制程節點的3nm芯片晶圓代工產品舉行了出廠儀式。才過4個月不到,韓國媒體Naver就爆出,三星3nm制程的良率非常低,不足20%。而且其5nm和4nm節點的良率問題也遲遲沒有得到改善。

其實,三星電子從2000年初就已經開始了對GAA晶體管結構的研究。自2017年開始,將其正式應用到3納米工藝,并于今年6月宣布啟動利用GAA技術的3納米工藝的量產。是全球首家將GAA晶體管結構用于晶圓制造的代工企業。據悉,我國的一家礦機芯片企業PanSemi(磐矽半導體)是三星電子的第一家客戶,目前也可能是其唯一的客戶。

據報道,三星電子為了解決良率問題,找到了美國的Silicon Frontline Technology,向這家企業尋求幫助。據說目前進展情況還不錯。

那么,三星電子在GAA上花的時間超過了20年,為何良率問題遲遲沒有得到解決呢?問題究竟出在了哪里?我們先從芯片的最基礎單元------晶體管結構的發展說起,然后看看有什么應對之策。

晶體管結構的發展歷史

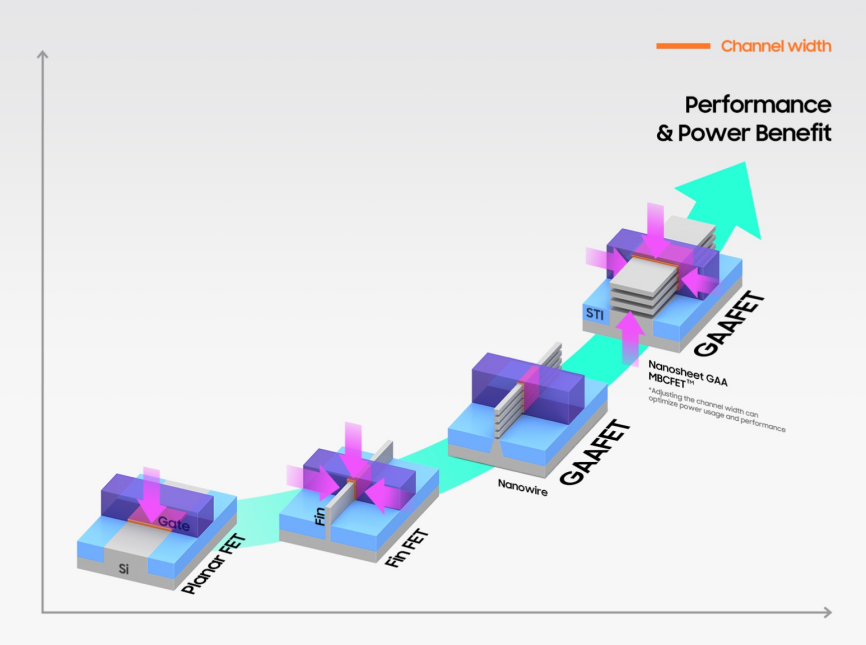

半導體芯片其實是眾多晶體管(Transistor)的集合,而晶體管其實就是一個小的開關。一個晶體管就代表了一個0或者1,也就是所謂的一個位元。在20nm以上的制程中,使用的晶體管被稱為金屬氧化物半導體場效應管(MOSFET:Metal Oxide Semiconductor FET);20nm~3nm,采用的是鰭式場效應晶體管(Fin FET:Fin Field Effected Transistor);3nm以下,采用的則是全環繞柵極場效應晶體管(GAAFET:Gate All Around Field Effect Transistor)。

良率問題低迷該怎么辦?

結語

原文標題:芯片制程到3nm后如何突破良率難題?

文章出處:【微信公眾號:電子發燒友網】歡迎添加關注!文章轉載請注明出處。

-

電子發燒友網

+關注

關注

1011文章

544瀏覽量

165336

原文標題:芯片制程到3nm后如何突破良率難題?

文章出處:【微信號:elecfans,微信公眾號:電子發燒友網】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

性能殺手锏!臺積電3nm工藝迭代,新一代手機芯片交戰

三星3nm良率僅20%,仍不放棄Exynos 2500處理器,欲打造“十核怪獸”

芯片制程到3nm后如何突破良率難題?

芯片制程到3nm后如何突破良率難題?

評論