FPGA配置基本介紹

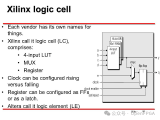

與CPLD不同,F(xiàn)PGA是基于門(mén)陣列方式為用戶(hù)提供可編程資源的,其內(nèi)部邏輯結(jié)構(gòu)的形成是由配置數(shù)據(jù)決定的。FPGA的配置方式分為主動(dòng)式和被動(dòng)式。

1配置引腳

FPGA的配置引腳可分為兩類(lèi):專(zhuān)用配置引腳和非專(zhuān)用配置引腳。專(zhuān)用配置引腳只有在配置時(shí)起作用,而非專(zhuān)用配置引腳在配置完成后則可以作為普通的I/O口使用。

專(zhuān)用的配置引腳有:配置模式腳M2、M1、M0;配置時(shí)鐘CCLK;配置邏輯異步復(fù)位PROG,啟動(dòng)控制DONE及邊界掃描TDI,TDO,TMS,TCK。非專(zhuān)用配置引腳有Din,D0:D7,CS,WRITE,BUSY,INIT。

在不同的配置模式下,配置時(shí)鐘CCLK可由FPGA內(nèi)部產(chǎn)生,也可以由外部控制電路提供。

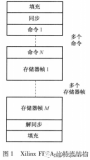

2配置過(guò)程

(1)初始化

系統(tǒng)上電后,如果FPGA滿(mǎn)足以下條件:Bank2的I/O輸出驅(qū)動(dòng)電壓Vcc0_2大于lv;器件內(nèi)部的供電電壓Vccint為2.5v,器件便會(huì)自動(dòng)進(jìn)行初始化。在系統(tǒng)上電的情況下,通過(guò)對(duì)PROG引腳置低電子,便可以對(duì)FPGA進(jìn)行重新配置。初始化過(guò)程完成后,DONE信號(hào)將會(huì)變低。

(2)清空配置存儲(chǔ)器

在完成初始化過(guò)程后,器件會(huì)將INIT信號(hào)置低電平,同時(shí)開(kāi)始清空配置存儲(chǔ)器。在清空完配置存儲(chǔ)器后,INIT信號(hào)將會(huì)重新被置為高電平。用戶(hù)可以通過(guò)將PROG或INIT信號(hào)(1NIT為雙向信號(hào))置為低電平,從而達(dá)到延長(zhǎng)清空配置存儲(chǔ)器的時(shí)間,以確保存儲(chǔ)器被清空的目的。

(3)加載配置數(shù)據(jù)

配置存儲(chǔ)器的清空完成后,器件對(duì)配置模式腳M2、N1、M0進(jìn)行采樣,以確定用何種方式來(lái)加載配置數(shù)據(jù)。

(4)CRC錯(cuò)誤檢查

器件在加載配置數(shù)據(jù)的同時(shí),會(huì)根據(jù)一定的算法產(chǎn)生一個(gè)CRC值,這個(gè)值將會(huì)和配置文件中內(nèi)置的CRC值進(jìn)行比較,如果兩者不一致,則說(shuō)明加載發(fā)生錯(cuò)誤,INIT引腳將會(huì)被置低電平,加載過(guò)程被中斷。此時(shí)若要進(jìn)行重新配置,只需將PROG置為低電平即可。

(5)START-UP

在START-UP階段中,F(xiàn)PGA會(huì)進(jìn)行一下操作:

①將DONE信號(hào)置高電平,若DONE信號(hào)沒(méi)有置高,則說(shuō)明數(shù)據(jù)加載過(guò)程失敗;

②在配置過(guò)程中,器件的所有I/O引腳均為三態(tài),此時(shí),全局三態(tài)信號(hào)GTS置低電平,這些I/O腳將會(huì)從三態(tài)切換到用戶(hù)設(shè)置的狀態(tài);

③全局復(fù)位信號(hào)GSR置低電平,所有觸發(fā)器進(jìn)入工作狀態(tài);

④全局寫(xiě)允許信號(hào)GWE置低電平,所有內(nèi)部RAM有效;

整個(gè)過(guò)程共有8個(gè)時(shí)鐘周期C0-C7。在默認(rèn)的情況下,這些操作都和配置時(shí)鐘CCLK同步,在DONE信號(hào)置高電子之前,GTS,GSR,GWE都保持高電平。

審核編輯 :李倩

-

FPGA

+關(guān)注

關(guān)注

1643文章

21956瀏覽量

614016 -

存儲(chǔ)器

+關(guān)注

關(guān)注

38文章

7633瀏覽量

166391

原文標(biāo)題:淺析FPGA的配置引腳以及配置過(guò)程

文章出處:【微信號(hào):gh_9d70b445f494,微信公眾號(hào):FPGA設(shè)計(jì)論壇】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

用FPGA配置ADS5562怎么確認(rèn)寄存器是否配置正常?

FPGA通過(guò)SPI對(duì)DAC進(jìn)行了配置,用頻譜儀測(cè)不到輸出是怎么回事?

FPGA 在人工智能中的應(yīng)用

FPGA與ASIC的區(qū)別 FPGA性能優(yōu)化技巧

FPGA基礎(chǔ)知識(shí)及設(shè)計(jì)和執(zhí)行FPGA應(yīng)用所需的工具

如何通過(guò)FPGA配置CDCI6214?

nginx負(fù)載均衡配置介紹

PCM5142如何在FPGA中通過(guò)SPI配置寄存器?

固化FPGA配置芯片的方式

一種簡(jiǎn)單高效配置FPGA的方法

分享一本書(shū) 《從零開(kāi)始設(shè)計(jì) FPGA 最小系統(tǒng)》

FPGA如何估算分析功耗

一文了解FPGA比特流的內(nèi)部結(jié)構(gòu)

FPGA配置基本介紹

FPGA配置基本介紹

評(píng)論