多核、超線程和高速 DMA 等現代處理器功能旨在優化平均案例執行時間。但是,這些優化通常以犧牲最壞情況的執行時間為代價,并使系統更難綁定。這種情況給安全關鍵型軟件的開發人員帶來了重大挑戰,他們必須針對最壞情況進行設計。因此,以下討論探討了為什么在軟件開發過程中關注最壞情況的行為,以及安全關鍵軟件開發人員面臨的一些與處理器相關的關鍵挑戰以及解決這些問題的方法。

為什么要關注最壞的情況行為?

在安全關鍵型軟件環境中,必須確保三個關鍵事項:

首先,每個周期線程(或任務)必須始終以其定義的速率(例如,100 Hz)執行。這很重要,因為每個線程必須以給定的速率執行,否則系統可能會變得不穩定,因此不安全。

其次,必須為每個周期線程分配一個不能超過的固定時間預算(例如,100 Hz 時為 200 微秒)。這很重要,因為它允許底層 RTOS 強制執行時間分區。

第三,每個周期線程的固定時間預算必須足以覆蓋線程的最壞情況行為。這很重要,因為許多安全關鍵線程必須在每個周期內執行以完成。否則,系統可能會變得不穩定,從而導致不安全。

請注意,這組要求與非關鍵軟件系統形成鮮明對比,在非關鍵軟件系統中,人們希望整體性能處于最高水平,但可以容忍性能低于平均水平的偶爾“故障”。

多核和緩存/內存爭用

自 1985 年以來,CPU 吞吐量大約每 18 個月翻一番,這與摩爾定律一致。然而,由于三個關鍵因素,這一趨勢在2005年左右開始放緩。主要原因是內存速度跟不上CPU性能,在同一時間段內每年僅增加約10%。較大的緩存有助于緩解此問題,但內存子系統仍然是重要的性能瓶頸。

從理論上講,更高的并行性應該通過使CPU能夠同時處理多個指令來提高峰值性能。然而,流水線、分支預測和推測執行等技術已經開始“碰壁”,這使得利用這種并行性變得越來越困難。

散熱因素也減緩了 CPU 吞吐量的推進速度。隨著工作頻率的增加,功耗和發熱也會成比例地增加。在許多環境中,散發這種熱量提出了艱巨的挑戰,特別是對于被動冷卻的嵌入式系統。

最近,多核處理器已經發展到可以應對其中的許多挑戰。例如,為了提高內存吞吐量,每個 CPU 內核都配備了自己的 L1 緩存。更緊密的物理封裝還通過縮短內核之間的信號運行來提高性能,從而使數據傳輸成比例地更快、更可靠。同時,多內核使處理器能夠在每個時鐘周期執行更多指令。這使得每個內核都能以較低的頻率運行,從而消耗更少的功率并產生更少的熱量。

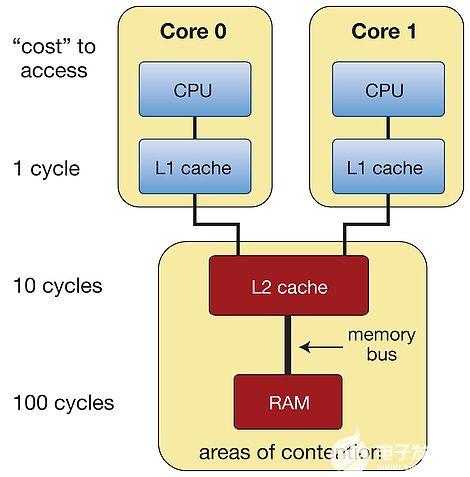

盡管取得了這些進步,但多核處理器仍然給安全關鍵型軟件的開發人員帶來了挑戰:主要是對二級緩存和內存子系統等共享資源的爭用增加。圖 1 顯示了一個簡單的雙核處理器,每個內核都有自己的 CPU 和 L1 緩存,兩個內核共享一個 L2 緩存和一個 RAM 子系統。

圖1:一個簡單的雙核處理器,每個內核都有自己的CPU和L1緩存,兩個內核共享一個L2緩存和一個RAM子系統

左側列出的值表示每個 CPU 在訪問給定資源時產生的“成本”。例如,假設 CPU 訪問其本地 L1 緩存需要一個周期。如果訪問未命中,并且 CPU 必須轉到 L2 緩存,則需要 10 個周期。如果二級緩存未命中并且CPU必須轉到RAM,則成本為100個周期。如果緩存“臟”并且需要“回寫”,則性能會更差。請注意,這些數字并不準確,并且會因處理器而異,但相對數量級是典型的。重要的一點是,CPU 訪問數據的距離越遠,數據傳輸所需的時間就越多。

當 CPU 上的多線程進程同時爭用該內核的 L1 緩存時,以及當多個內核同時競爭共享的 L2 緩存和內存子系統時,就會發生爭用。即使使用單核處理器,CPU 也很容易使內存子系統不堪重負。在多核系統中,多個內核必須爭用共享內存資源,內存訪問瓶頸要嚴重得多。

松弛調度和緩存分區

開發人員可以減少內存爭用并利用多核的強大功能,同時仍滿足最壞情況的執行要求的一種方法是利用針對安全關鍵型應用程序優化的實時操作系統。例如,DDC-I 的 Deos 提供緩存分區和松弛調度功能,可緩解內存訪問瓶頸,增強確定性,并提高跨一個或多個內核的安全關鍵應用程序的 CPU 利用率。

緩存分區使設計人員能夠將一部分緩存專用于每個內核,從而減少內存爭用和最壞情況下的執行時間。通過這種物理分區,每個核心可用的緩存總量將減少。但是,由于多個內核不再共享同一資源,因此總體爭用減少了。

同時,Slack 調度利用了平均線程執行時間通常比最壞情況執行時間短得多的事實。對于那些實際執行時間小于最壞情況預算時間的線程,RTOS回收未使用的時間并將其重新分配給其他線程,從而提高整體系統性能。

超線程 (HT)

HT 允許通過復制存儲特定應用程序狀態的處理器部分而不復制處理器的主處理引擎 (CPU) 來提高計算的并行化。這樣,HT 處理器在 RTOS 中顯示為兩個邏輯處理器。超線程技術還可用于多核設置,其中每個內核有兩個邏輯內核。

超線程處理器的優點是提高了應用程序代碼的并行化,并縮短了反應和響應時間。例如,與非HT處理器相比,某些HT處理器的性能提高了30%。不幸的是,使用安全關鍵型軟件很難實現此性能,因為 HT 增加了對緩存和內存子系統的爭用,并使系統更難綁定。因此,在許多安全關鍵應用中必須禁用HT。

動態頻率縮放 (DFS)

DFS(也稱為 CPU 節流)允許實時調整處理器時鐘的頻率,以節省功率或減少芯片產生的熱量。雖然DFS主要用于電池供電的移動設備,但也可用于被動冷卻的航空電子系統,該系統必須僅使用環境空氣來滿足嚴格的熱分布。DFS通常與動態電壓調節(DVS)結合使用,因為頻率與工作電壓成正比,功耗隨著電壓的平方而增加。

DFS 和 DVS 可以節省功耗并減少熱量,但在安全關鍵環境中,它們存在問題,因為它們還可以減少處理器在給定時間內可以發出的指令數量(包括減慢內存總線訪問速度)。因此,性能可能會以難以綁定的不可預測的方式降低。如果功耗不是門控因素,則可以禁用 DFS 和 DVS。或者,想要利用DFS和DVS的設計人員可以通過測量最壞情況的性能來實現,同時在較低頻率/電壓下運行處理器,然后相應地進行預算。

直接內存訪問 (DMA)

DMA 允許設備在不涉及 CPU 的情況下將大量數據(包括地圖顯示和地形數據庫)移入和移出系統內存,從而提高性能,從而釋放 CPU 以執行其他工作。對于安全關鍵型軟件,DMA 的主要缺點是它在 CPU 和內存管理單元 (MMU) 的控制之外運行。因此,DMA 控制器中的缺陷可能會破壞空間分區。緩解此問題的一種方法是將RTOS與滿足最高設計保證的特殊DMA控制器軟件一起使用。

在像Deos這樣的RTOS的幫助下,安全關鍵型系統的設計人員可以獲得具有多核、高速DMA和DFS的高級處理器的性能優勢,而不會影響最壞情況下的執行時間。然而,并非所有高級處理器功能都非常適合安全關鍵型應用。有些(如超線程)雖然是提高平均性能的理想選擇,但只是缺乏安全關鍵應用程序所需的確定性,必須禁用。

審核編輯:郭婷

-

處理器

+關注

關注

68文章

19813瀏覽量

233622 -

cpu

+關注

關注

68文章

11040瀏覽量

216049

發布評論請先 登錄

DS5003安全微處理器芯片技術手冊

光子 AI 處理器的核心原理及突破性進展

自主創新,安全可控:申威SW831處理器與國產終端產品推薦

低功耗處理器的優勢分析

處理器和芯片的區別是什么 處理器是指cpu嗎

量子處理器是什么_量子處理器原理

云計算HPC軟件關鍵技術

處理器指令的獲取過程

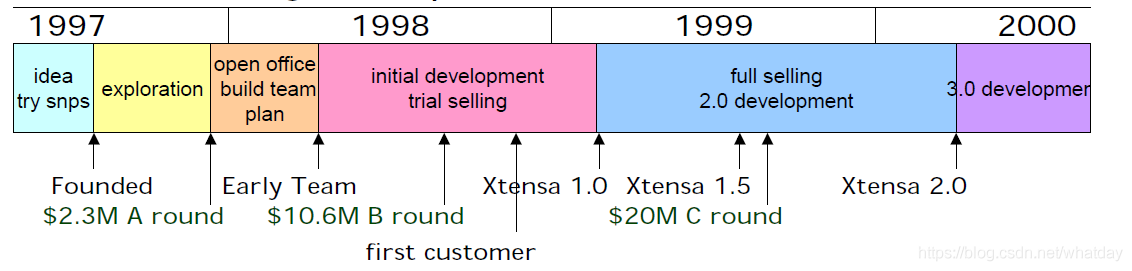

Tensilica處理器及Xtensa LX7處理器介紹

ARM處理器和CISC處理器的區別

簡述微處理器的發展歷史

解決安全關鍵型軟件的處理器挑戰

解決安全關鍵型軟件的處理器挑戰

評論