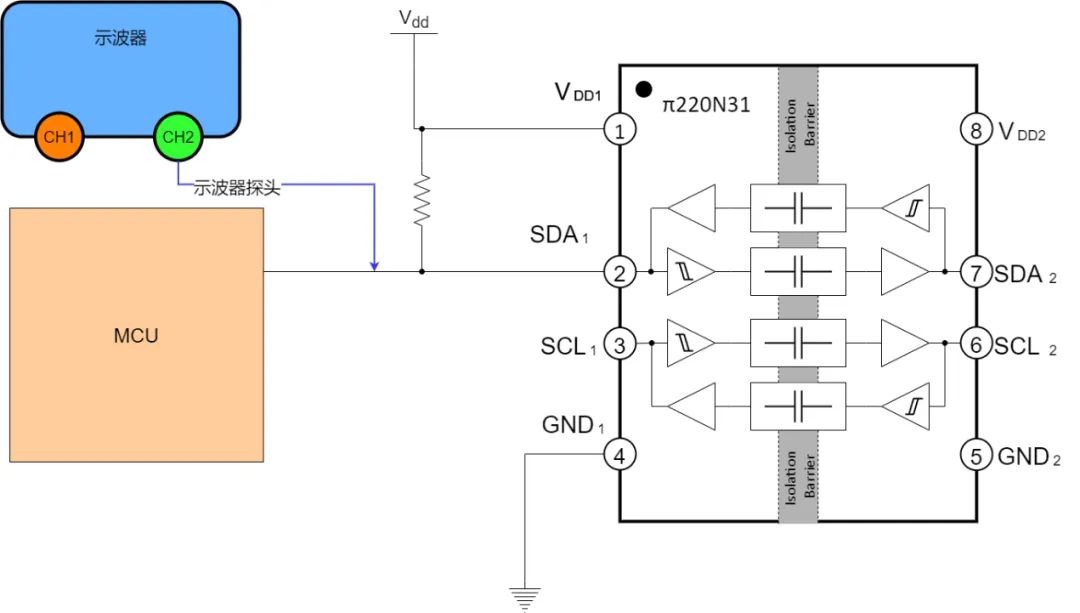

工程師在調(diào)試IIC通訊總線時(shí),一般會(huì)將示波器探頭加掛到IIC隔離器邏輯側(cè)端口上,去觀察通信過(guò)程中波形是否有誤碼,如下圖所示:

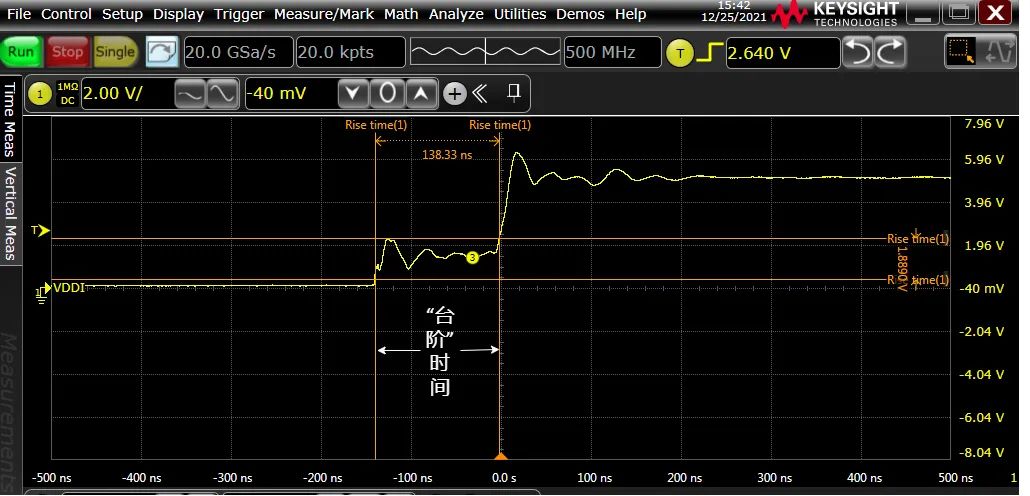

若在MCU向220N31/220N61的SDA1或SCL1端口發(fā)送信號(hào)的同時(shí)觀察波形,工程師們會(huì)發(fā)現(xiàn)波形上升過(guò)程中會(huì)出現(xiàn)一個(gè)明顯的“臺(tái)階”,通過(guò)調(diào)整外部電路無(wú)法消除;如果斷開(kāi)IIC隔離器和MCU之間的連接之后直接觀察MCU輸出的信號(hào),會(huì)看不到這個(gè)“臺(tái)階”。這個(gè)“臺(tái)階”并非由電路設(shè)計(jì)不當(dāng)或者器件故障導(dǎo)致的,而是所有雙向信號(hào)通道的IIC隔離器必然會(huì)出現(xiàn)的正常現(xiàn)象,無(wú)需擔(dān)心。

這個(gè)“臺(tái)階”持續(xù)的時(shí)間被稱(chēng)為為IIC隔離器的環(huán)路延時(shí),是IIC隔離器件的關(guān)鍵性能參數(shù)之一。IIC隔離器自身的時(shí)序性能和隔離器總線側(cè)外圍參數(shù)都會(huì)影響環(huán)路延時(shí)的大小。

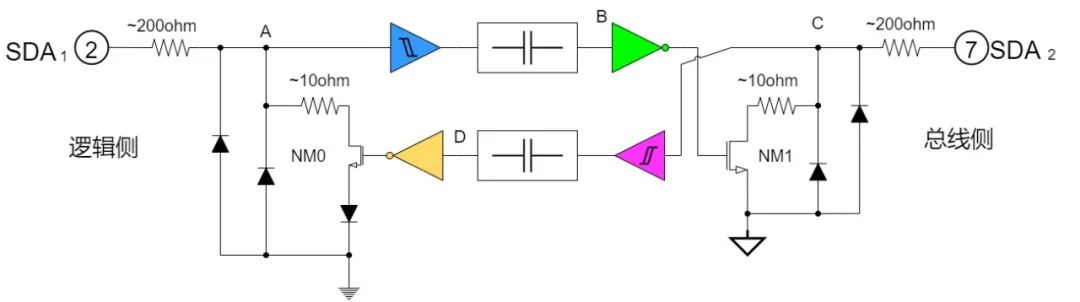

榮湃IIC隔離器雙向信號(hào)通道的內(nèi)部示意結(jié)構(gòu)如圖所示,以SDA通道為例。可以看到,每個(gè)端口既可以作為輸出,也可以作為輸入,是復(fù)用的。邏輯側(cè)下拉NMOS下面的二極管提供了一個(gè)對(duì)地的電壓差,可以防止整個(gè)電路被鎖死在低電平。

當(dāng)MCU輸出給IIC隔離器的信號(hào)從低電平上升到高電平的時(shí)候,A點(diǎn)電壓會(huì)超過(guò)邏輯側(cè)輸入閾值即600mv,藍(lán)色的輸入模塊會(huì)向綠色的輸出模塊發(fā)送高電平信號(hào)。此時(shí),D點(diǎn)依然為低電平信號(hào)狀態(tài)、通過(guò)反向器輸出高電壓使NM0導(dǎo)通,所以外部的電壓無(wú)法上拉到VDD,波形出現(xiàn)臺(tái)階。經(jīng)過(guò)一個(gè)傳播延時(shí)之后,B點(diǎn)從低電平變?yōu)楦唠娖剑偩€側(cè)NM1關(guān)斷,C點(diǎn)電壓通過(guò)外部上拉電阻開(kāi)始上升。當(dāng)C點(diǎn)的電壓達(dá)到0.7x VDD時(shí),紫色的輸入模塊識(shí)別到高電平,向黃色的輸出模塊發(fā)送高電平。再經(jīng)過(guò)一個(gè)傳播延時(shí)之后,D點(diǎn)變?yōu)楦唠娖剑壿媯?cè)NM0關(guān)斷,A點(diǎn)電壓從“臺(tái)階”電平升高到VDD1電壓。

過(guò)程時(shí)序圖如下:

以上就是IIC隔離器邏輯側(cè)端口波形出現(xiàn)“臺(tái)階”的原因。可以看到,“臺(tái)階”的持續(xù)時(shí)間由邏輯側(cè)至總線側(cè)傳播延時(shí)、總線側(cè)端口外部上升時(shí)間和總線側(cè)至邏輯側(cè)傳播延時(shí)共同構(gòu)成。榮湃pai220N31、Pai220N61的傳播延時(shí)低至45ns,配合總線側(cè)端口外部100歐姆上拉,整體環(huán)路延時(shí)可控制在120ns以內(nèi),能夠支持高速的IIC通信。

審核編輯:湯梓紅

-

示波器

+關(guān)注

關(guān)注

113文章

6534瀏覽量

188187 -

IIC

+關(guān)注

關(guān)注

11文章

306瀏覽量

39154 -

隔離器

+關(guān)注

關(guān)注

4文章

841瀏覽量

39041

原文標(biāo)題:技術(shù)課堂之十八 | IIC邏輯側(cè)波形出現(xiàn)“臺(tái)階”原因的探討

文章出處:【微信號(hào):gh_fb935efbb3e1,微信公眾號(hào):榮湃半導(dǎo)體】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

ADP2443 SW側(cè)無(wú)法輸出正常PWM波形的原因是什么?

采用AD62P29進(jìn)行模數(shù)轉(zhuǎn)換,對(duì)正弦信號(hào)的轉(zhuǎn)換后的波形不連續(xù),會(huì)出現(xiàn)臺(tái)階?為什么?

CAN總線冷知識(shí)-邊沿臺(tái)階是怎么來(lái)的?

IIC的通信原理及分析IIC的真實(shí)波形

STM32F334 ADC輸入時(shí)會(huì)產(chǎn)生一個(gè)脈沖臺(tái)階是什么原因導(dǎo)致的,怎么解決

邏輯電平互連出現(xiàn)電流倒灌的原因及解決措施

邏輯電平互連出現(xiàn)電流倒灌的原因及解決措施

從IIC實(shí)測(cè)波形入手,搞懂IIC通信

[轉(zhuǎn)]從IIC實(shí)測(cè)波形入手,搞懂IIC通信

![[轉(zhuǎn)]從<b class='flag-5'>IIC</b>實(shí)測(cè)<b class='flag-5'>波形</b>入手,搞懂<b class='flag-5'>IIC</b>通信](https://file.elecfans.com/web1/M00/D9/4E/pIYBAF_1ac2Ac0EEAABDkS1IP1s689.png)

IIC邏輯側(cè)波形出現(xiàn)“臺(tái)階”原因的探討

IIC邏輯側(cè)波形出現(xiàn)“臺(tái)階”原因的探討

評(píng)論