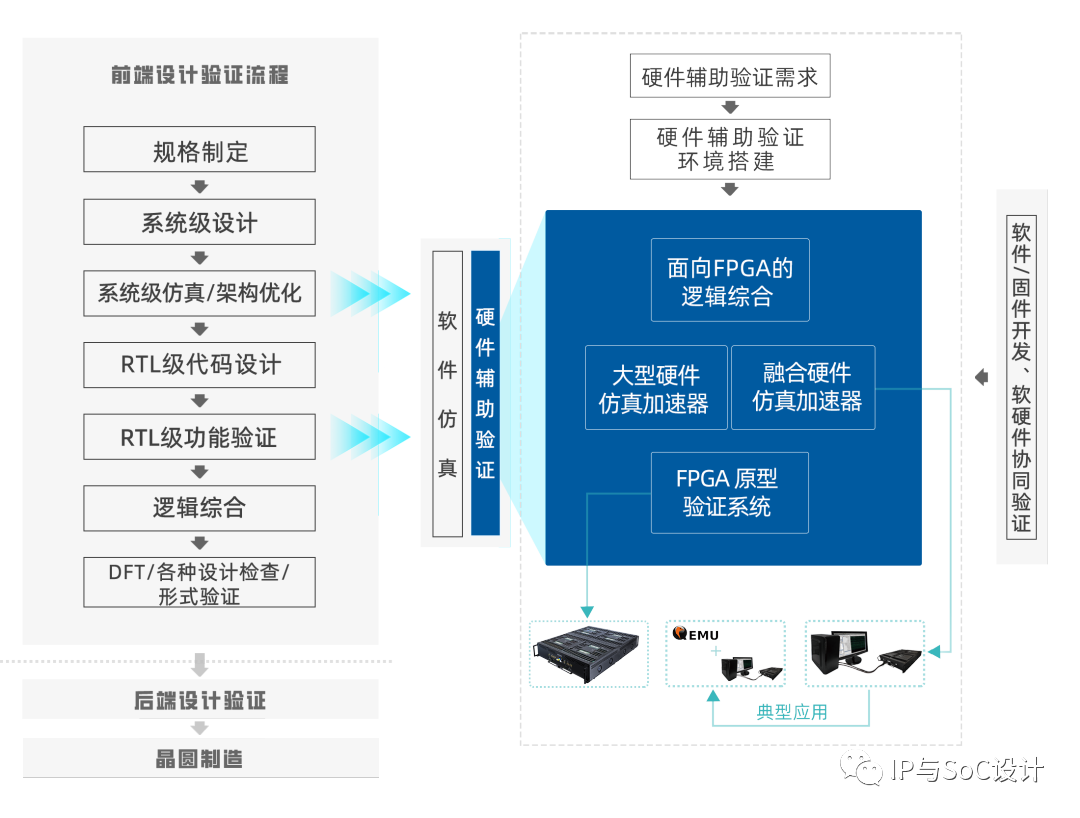

近年來,芯片規模,功能復雜度以及集成度的不斷增加,驗證工作面臨著非常大的挑戰。軟件仿真(Simulation),FPGA原型驗證(FPGA Based Prototyping)和硬件仿真加速(Emulation)這三種有效的功能驗證的方法,在驗證流程中發揮著非常重要的作用。

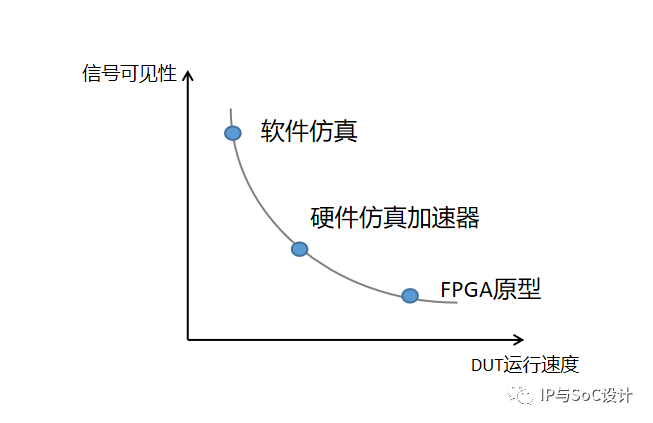

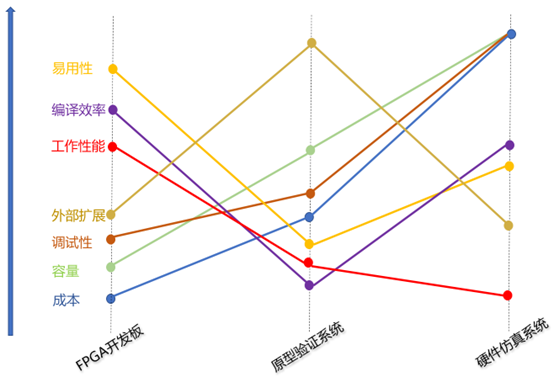

軟件仿真有著出色的信號可見性,FPGA原型驗證有著極強的實時性和系統開發性,硬件仿真加速則兼具了信號可見性,可調試性,以及仿真加速的能力,這幾種驗證方法在芯片前端設計的功能性驗證階段發揮著重要的作用。FPGA原型驗證和硬件仿真加速作為硬件輔助驗證的兩種手段,在芯片設計的過程中相輔相成,互為補充,為芯片成功流片保駕護航。

硬件仿真加速階段,一般用于代碼還不很成熟的開發的中后期階段,需要能夠提供更大的系統容量,更方便的調試手段和方法,主要用來驗證設計的RTL代碼,兼顧軟硬件協同驗證和軟件開發。而FPGA原型驗證階段一般應用于代碼比較成熟的的偏后階段,主要是做軟件開發和軟硬件協同驗證。

圖一 硬件輔助驗證在流程中的位置

幾種不同的仿真驗證手段的效果對比

(一)基于硬件輔助驗證工具的仿真加速方法

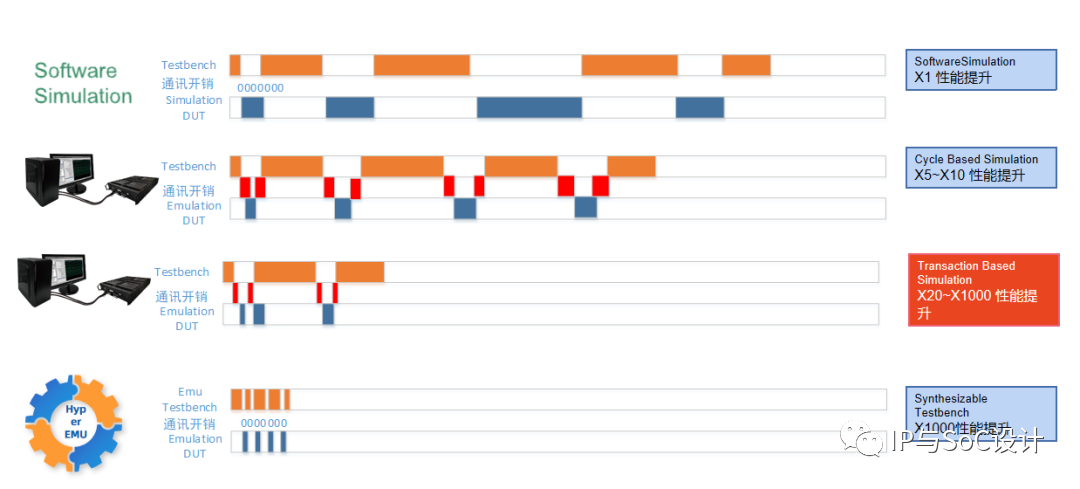

一般意義上,我們將FPGA原型驗證和硬件仿真加速都歸為硬件輔助驗證手段,比較有效和最為常見的仿真加速方式分為:軟件仿真(Software Simulation),周期精確級的仿真加速(Cycle Based Simulation ),事務級的仿真加速(Transaction Based Simulation),和完全可綜合的仿真加速(Synthesizable Simulation)這幾種方法。通過不同的仿真加速方法,對驗證速度能夠有接近千倍的提升。

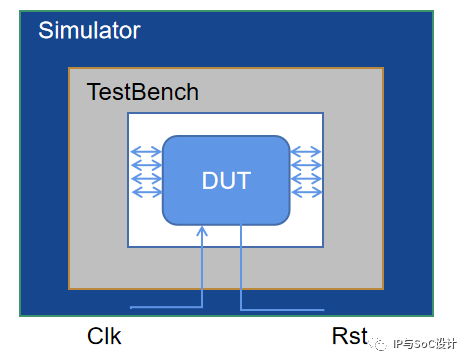

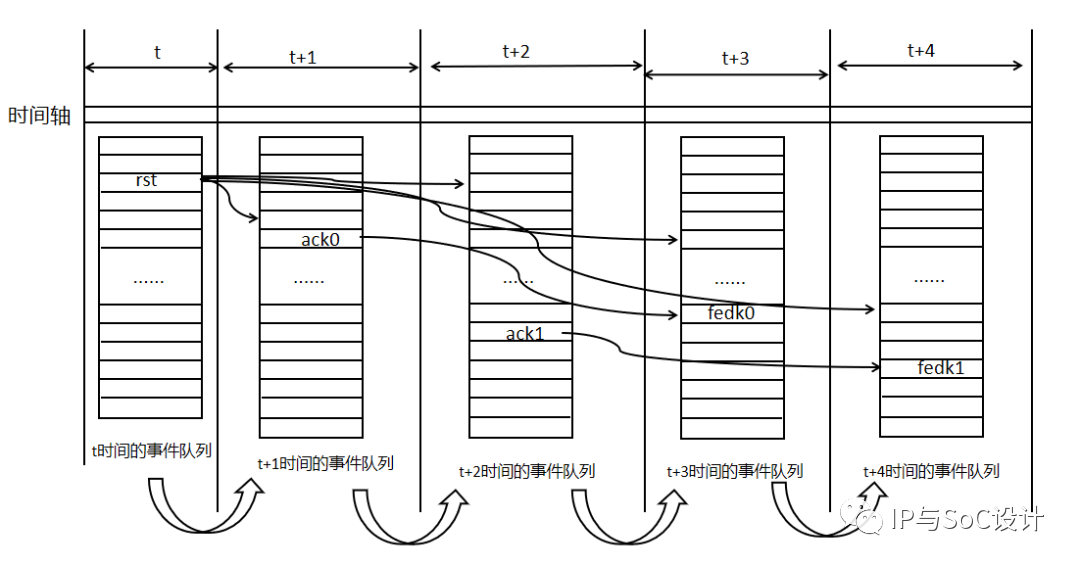

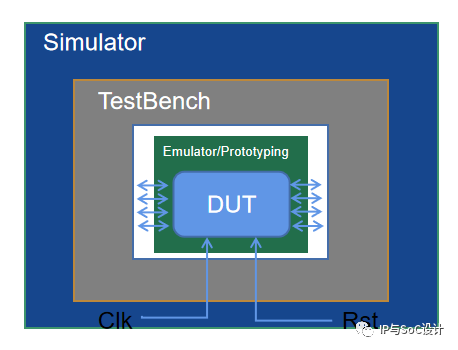

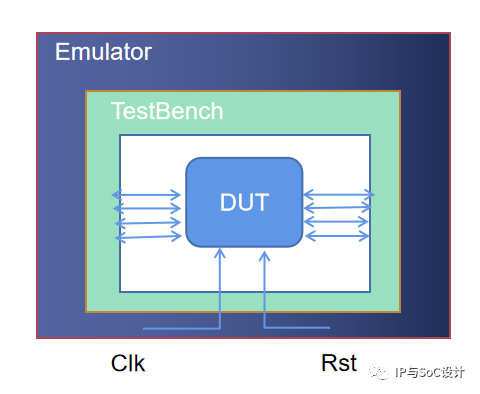

第一種,軟件仿真(Software Simulation),最常見的仿真方法,將Testbench和DUT都在仿真軟件中運行。最主流的仿真軟件的算法機制大部分都是“基于事件的算法”這種算法更適合處理離散的時間,狀態和變量。仿真器首先在編譯數據結構的時候會建立一個事件隊列,仿真從時間0開始,在時間0的所有事件隊列處理完畢以后,才可以進入下一個時間周期。而在同一個時間周期內的事件在“硬件”上都是并行的。

圖二 Simulator仿真的結構

圖三 基于事件的Simulator算法

第二種:周期精確級的仿真加速(Cycle Based Simulation Acceleration )

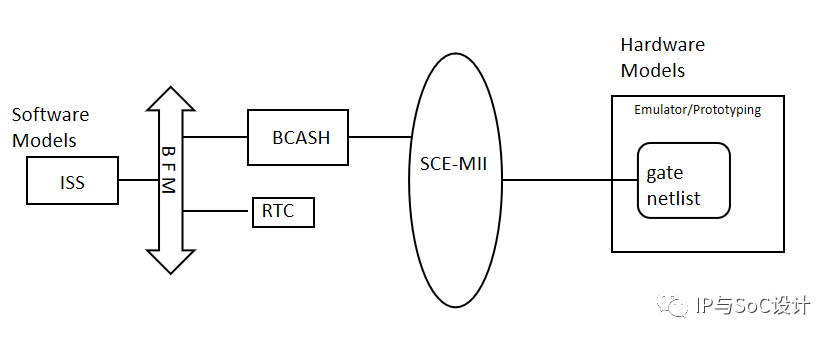

我們在針對軟硬件聯合仿真的方式做說明之前,需要對SCE-MI/MII(標準協同仿真建模接口)做一下說明,該接口是為了標準化軟件模型和硬件平臺之間的通訊而定義的,屬于Accellera標準,目的是使用者將DUT和Testbench做連接,通過事務器模型(Transactor)能夠輕松的實現互聯。下圖是該協議的基本結構說明。

圖四 SCE-MII基本結構

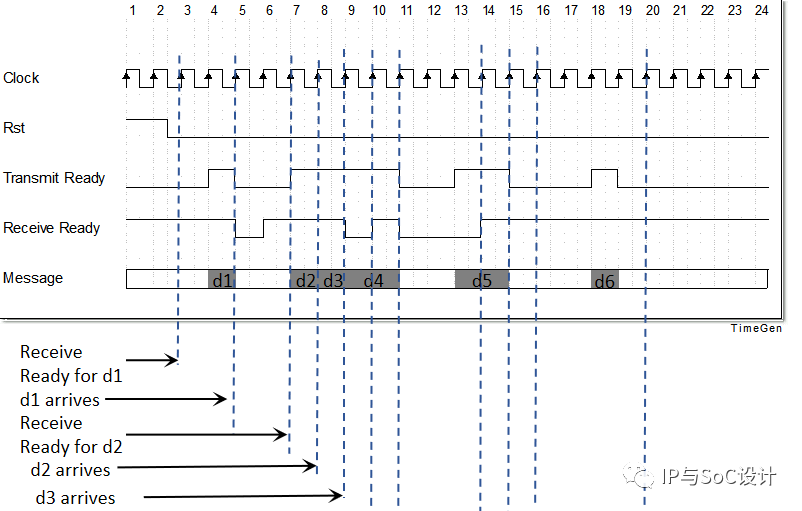

周期精確級的仿真加速,是通過專用的硬件來運行用戶設計,通過仿真軟件運行Testbench,根據專用的軟硬件協同工作的協議來進行軟件硬件側的數據轉換和交付,從而實現軟件仿真加速的一種方法。

該方法在軟硬件兩側交互的周期中,嚴格按照時間單位推進每一步的協議轉換,并且采用雙握手的方式進行通訊確認,這將產生大量的軟硬件之間的交互開銷,所以在加速的效果上不是十分的理想。這種方式的優點是針對一些非標協議的轉換和時鐘同步結構的設計有很大的靈活性。

圖五:周期精確級的仿真加速結構

圖六:雙握手協議示意

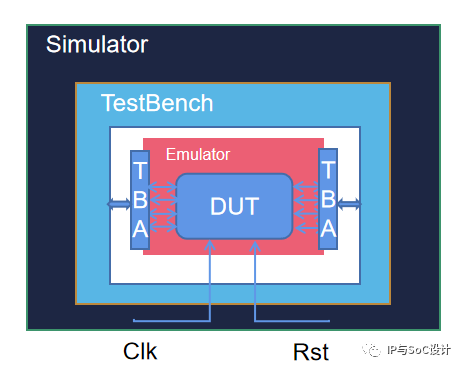

第三種:事務級的仿真加速(Transaction Based Acceleration)

事務級的仿真加速是將DUT和部分Testbench運行在硬件輔助驗證工具之中,通過事務器與仿真器中運行的Testbench進行通訊,可以實現將無時序激勵變為有時序功能的交互。這是因為軟件側的一個操作所花費的時間在一般情況下會遠大于硬件側的時鐘周期。

當發送一個帶時序的激勵時,軟件側需要花更多的時間進行時序的構建,會在一定程度上影響軟硬件協同仿真平臺的性能。所以在軟硬件驗證過程中,事務級仿真加速能夠很好的解決這類型的問題。

比如對于一個擁有AXI或者AHB接口的DUT,軟件側需要按照AXI或者AHB的時序規則構建激勵,而擴展了無時序激勵變有時序功能時,僅需要將AXI或者AHB的總線數據按順序發送至硬件側,硬件側可以自動完成時序的構建,這樣的功能結構能夠大幅度提高仿真的效率。

圖七:事務級的仿真加速結構

第四種:完全可綜合的仿真加速(Synthesizable Testbench Simulation )

圖八:完全可綜合的仿真加速結構

這種仿真加速方式相較于Transaction的仿真加速,是需要將用戶的DUT和測試激勵完全綜合進仿真加速器,這樣可以大大的減少因為軟硬件的交互而產生的通訊開銷,從而可以極大地提高仿真速度。

不同的軟硬件結合的仿真加速方式能夠帶來不同的加速比,周期精確級的仿真加速因為通訊開銷帶來的影響,相較于軟件仿真基本上可以做到5-100倍的仿真加速;基于事務級的仿真加速則能夠為用戶帶來20-1000倍的加速體驗,尤其適用于各種專用的算法實現,比如:視頻編解碼的處理,交互數據量巨大的通訊芯片驗證等。而完全可綜合的仿真加速則可以針對全流程的設計驗證提供最有效的仿真加速手段。

圖九:幾種不同的仿真加速的加速比

(二)利用硬件輔助驗證工具實現混合仿真

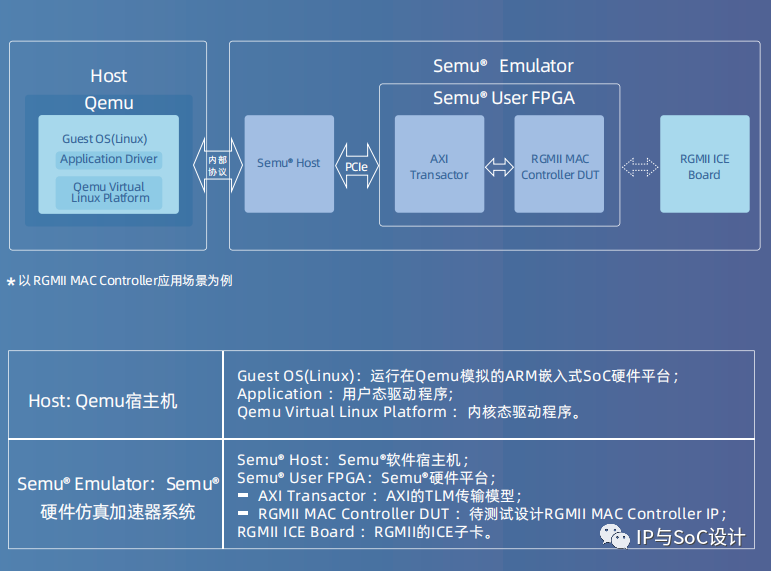

基于硬件輔助驗證的混合仿真是指利用硬件仿真加速器和虛擬原型同時運行SoC的不同設計模塊,在SoC整體架構硬件實現之前提供嵌入式軟件和硬件的協同仿真,從而加速SoC的研發進程。

可以實現硅前硬件和嵌入式軟件協同混合驗證,為系統架構的優化、嵌入式軟件以及RTL的早期開發提供準確,即時的仿真驗證環境,有力推動產品開發左移。

一般的混合仿真系統由Qemu宿主機和硬件仿真加速系統兩部分構成,其中,宿主機的操作系統中會運行基于開源環境的目標嵌入式處理器和基于Qemu Virtual Linux Platform的內核驅動程序以及用戶態的驅動程序。

通過專有協議實現軟件和用戶設計的通訊,將運行硬件仿真加速工具的宿主機和硬件平臺,通過TLM(Transaction Level Model)的傳輸模型,將用戶設計的IP和實現硬件結構的功能子卡進行聯合,從而實現一個完整的混合仿真系統。

圖十:混合驗證工作流程

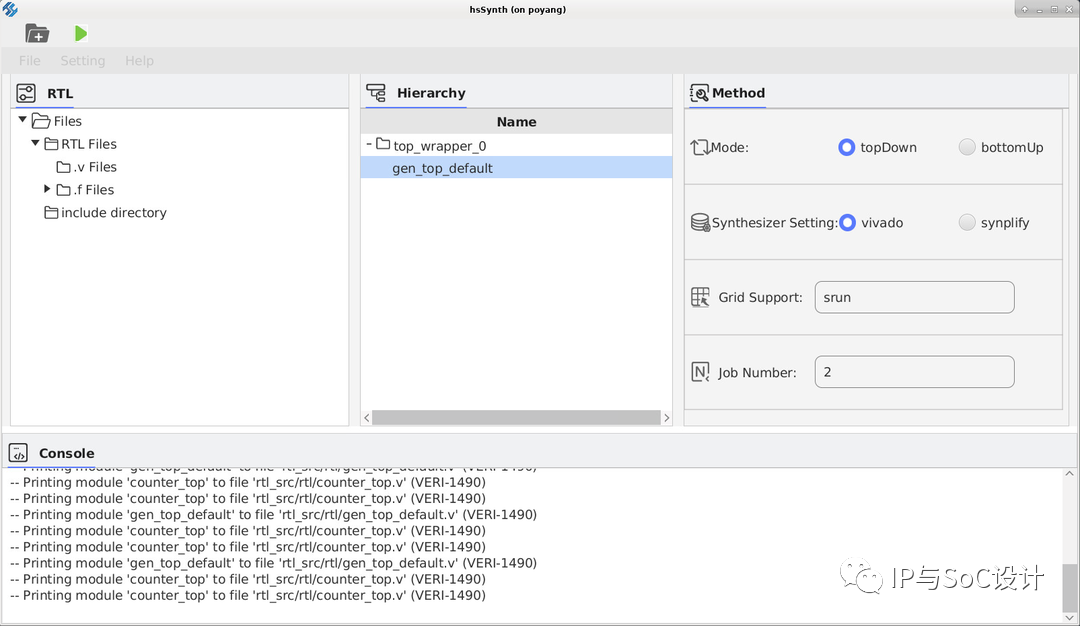

(三)集成高效的并行邏輯綜合工具提升硬件輔助驗證效率

設計驗證過程綜合時間長,迭代頻率高,需要設計工程師和驗證工程師花費大量的工作時間和精力。近年來,隨著多種圖像處理器,人工智能加速算法,大數據采集,多處理器應用等應用方向的芯片設計增加,各種GPU,TPU,XPU等大邏輯量的IP被集成至單顆芯片內,造成設計、仿真和驗證的數據量出現了指數級的增長,所以綜合和仿真等過程都展現出“過長的編譯綜合時間”、“編譯迭代耗時過長”等情況,工程師大量的時間浪費在了等待綜合編譯上。

流程節點不同,存在不同的綜合策略需求。硬件仿真加速階段,一般用于代碼還不很成熟的開發的中后期階段,需要能夠提供更大的系統容量,更方便的調試手段和方法,主要用來驗證設計的RTL代碼,兼顧軟硬件協同驗證和軟件開發。而原型驗證階段一般應用于代碼比較成熟的的偏后階段,主要是做軟件開發和軟硬件協同驗證。

在以上兩個流程階段,綜合加速的需求各有側重點。硬件仿真加速階段代碼的成熟度不高,迭代頻繁,需要更高速的編譯速度來提高迭代效率,以及對RTL代碼的忠實的一致反映以便于調試;而原型驗證階段代碼相對成熟,需要產生出更高效的功能等效系統來提高運行速度。

高效并行綜合是將用戶的RTL代碼按照不同模組分類,分別調用綜合工具,同時進行綜合,從而實現快速綜合的目的,按照不同的階段,可以設置不同的綜合流程,可以實現“Top-down”和“Bottom-up”兩種方式;支持多種的邏輯綜合器,比如:Xilinx Vivado, Synposys Synplify和其他的一些開源的邏輯綜合器,支持GUI和Batch模式,用戶可以靈活選擇功能展現模式;可以支持模組并行化處理,既支持本地多線程并行處理,也可以有效的支持多種作業調度系統;可以設置不同的參數來制定不同的綜合策略,從而實現綜合效率的最大化,比如:面積優先,速度優先,最大化、小化優先等策略。

通過并行邏輯綜合方案可以提供出色的自動化流程,大大縮短編譯所需時間,提高整體的效率和利用率,極大的提高生產率。

圖十一:并行綜合處理界面

(四)高效的在線邏輯分析工具提升硬件輔助驗證效率

FPGA產品自帶的在線邏輯分析儀工具(ILA 或 SignalTap)可以為FPGA提供觀測信號的便捷性,但因為其本身的屬性問題,存在了諸多的短板,例如:數據波形存儲在片上的RAM中,需要均衡用戶設計占用的存儲資源和用于調試的存儲資源;受限于FPGA片上RAM的容量,對待抓取的信號的位寬和深度都有限制;待抓取波形需要從FPGA的RAM資源中通過JTAG導出到工作站中,由于傳輸速度過慢,當數據量巨大時,傳輸時間占用更加的明顯;芯片邏輯容量增加,原廠的邏輯分析儀無法滿足調試需求。

硬件輔助驗證工具中的專用邏輯分析儀有效的解決了以上的幾個問題。

1)波形數據存儲在FPGA外部存儲,幾乎不占用FPGA的片上ram資源;FPGA器件因為其工藝特殊性,一般會集成一些RAM資源在FPGA種,但是該種資源的深度和位寬都非常的小,無法滿足超大容量的存儲需求,亞科鴻禹新研發的hsTrace,在系統內部集成有專用的外置存儲空間,可以完全不占用FPGA的RAM資源。

2)外接存儲容量最高可支持16GB的存儲空間,極大地提高了波形數據的采樣大小;硬件輔助驗證工具外置專用的存儲空間,可以使數據存儲和讀取的資源加大,也就意味著可以提供更深的存儲空間和更寬的存儲位寬,為解決當下驗證功能的需求提供了基礎。

3)波形數據的傳輸通過網口(或PCIE)實現,傳輸速率也得到了極大的提升。FPGA原廠提供在線邏輯分析儀的調試通道是通過JTAG接口完成的,JTAG的最大傳輸速度只能到12Mhz,我們選用的PCIE的傳輸帶寬能夠到5Gbps,這為大數據量吞吐提供了硬件通道。

4)支持多顆FPGA的硬件輔助驗證工具,實現多FPGA的系統級debug。

5)每顆FPGA可以設置4K*10組的采樣信號量;通過專用的傳輸接口和存儲器,可以針對單顆FPGA的采樣信號進行增加,這意味著可以有更多和更深的信號被采樣到,也就是可以完成更多數量的觀測,適應當前的復雜協議的應用。

(五)硬件輔助驗證的發展趨勢

硬件輔助驗證工具可以有效加速軟件仿真速度,用于驗證設計的RTL代碼、軟硬件協同驗證和軟件開發。近些年,硬件輔助驗證出現了一些明顯的發展趨勢:

1)企業級和桌面化的硬件仿真加速需求快速增長。當前,以GPU,5G,存算一體為代表的超大型的集成電路設計層出不窮,對系統仿真速度和代碼快速簽核提出了大量的需求。由于數據計算量大,用戶測試場景復雜所以需要能夠在超大型的硬件仿真加速工具下進行用戶設計和驗證環境的部署。

企業級的硬件仿真加速器可以為用戶提供指數級的邏輯驗證容量,高效的糾錯能力,信號可見和功耗分析的特征。桌面化的硬件仿真加速器可以為用戶提供混合驗證環境,能夠為各類型的CPU用戶,提供更早期的環境驗證。企業級硬件仿真加速器側重在多用戶,多區域訪問的特性,桌面化能夠提供更加便利的調試手段,所以兩種不同的應用方向各自發展。

2)硬件仿真加速器的專用化越來越明顯。加密算法,WIFI應用等各種測試數據量巨大,而算法相對單一的用戶,對仿真需求增大。而傳統的仿真加速器并不能非常有效的解決這類用戶的問題。所以,針對各類型應用而專用的仿真加速器產品非常適合這種類型的應用。集中固定的硬件擴展卡或者專用的降速橋都可以為某些類型的應用提供完整的加速環境。

3)全流程驗證需要在硬件仿真加速工具中完成。早期的硬件仿真加速器出現在代碼設計的后端,用于確認代碼功能的正確性。現在隨著設計的時間需求進坡度增加,越來越多的流程會被集成至硬件仿真加速工具中來實現。早期的功耗分析,系統環境搭建,邏輯調試等功能都逐漸的被集成至硬件仿真加速工具中。

4)仿真和驗證環境有統一性的趨勢。仿真代碼和用戶芯片設計代碼是分開處理的,涉及到一些無法綜合的代碼可以分別在仿真和驗證場景中實現,但是用戶期望的是設計代碼和測試代碼保持一致。所以硬件仿真加速工具會增加大量的功能屬性用于統一仿真代碼和設計代碼,從而減少因為設計不一致而造成的功能風險。

5)需要支持多種的軟件仿真工具。因為硬件仿真加速器的歷史原因,各家的工具分別只能支持自己家的軟件仿真工具,而對于不同的用戶來說,有一些訴求是能夠支持不同家的仿真工具的。

6)待驗設計的運行頻率逐漸升高。硬件仿真加速器的運行頻率,因為軟硬件交互的原因,會產生大量的通訊開銷,會對待驗設計的運行速率有很大的影響,絕大多數情況下只能運行在幾百K-幾兆Hz,隨著各種專用算法的出現,驗證的實時性也相當的重要。所以對于硬件仿真加速器來說,能夠提供比較實時的運行頻率,是非常關鍵的。

審核編輯:劉清

-

FPGA設計

+關注

關注

9文章

428瀏覽量

27340 -

RTL

+關注

關注

1文章

389瀏覽量

61079 -

AHB總線

+關注

關注

0文章

18瀏覽量

9790 -

DUT

+關注

關注

0文章

191瀏覽量

12951

原文標題:利用硬件輔助驗證工具加速功能仿真

文章出處:【微信號:IP與SoC設計,微信公眾號:IP與SoC設計】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

推動硬件輔助驗證平臺增長的關鍵因素

芯片前端設計中常用的軟件和工具

硬件輔助驗證(HAV) 對軟件驗證的價值

DevEco Studio AI輔助開發工具兩大升級功能 鴻蒙應用開發效率再提升

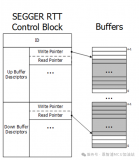

Segger RTT調試工具的使用方法

求助,關于iMX DDR3寄存器編程輔助問題求解

新思科技推出全新硬件輔助驗證產品組合

西門子Veloce硬件輔助驗證平臺升級

dbForge Studio for PostgreSQL:PostgreSQL數據庫多功能集成開發環境

如何通過智能布線提升新建筑的功能性?

EDA在物聯網設計中的應用

利用仿真技術進行智能制動系統的開發

SD NAND測試套件:提升存儲芯片驗證效率

利用硬件輔助工具加速芯片前端設計的功能性驗證階段

利用硬件輔助工具加速芯片前端設計的功能性驗證階段

評論