硬件加速和基于FPGA的原型設(shè)計(jì)誕生于1980年代中期,開(kāi)發(fā)者將當(dāng)時(shí)初露頭角的現(xiàn)場(chǎng)可編程門陣列(FPGA)率先應(yīng)用于硅前設(shè)計(jì)的原型驗(yàn)證,由此催生了一種全新的驗(yàn)證工具,打破了軟件仿真的主導(dǎo)局面。

最初,硬件加速的實(shí)現(xiàn)過(guò)程不僅復(fù)雜且依賴專業(yè)知識(shí),因此發(fā)展受限。然而,在簡(jiǎn)化啟動(dòng)和調(diào)試方面,通過(guò)軟件與架構(gòu)層面的持續(xù)優(yōu)化與創(chuàng)新,推動(dòng)了這項(xiàng)技術(shù)的發(fā)展。從1990年代中期到21世紀(jì)初,硬件加速逐漸成熟,成為驗(yàn)證復(fù)雜處理器和顯卡設(shè)計(jì)的關(guān)鍵方法。在這一時(shí)期,在線硬件加速(ICE)興起,它將被測(cè)設(shè)計(jì)(DUT)部署在預(yù)期的物理目標(biāo)系統(tǒng)中,這種方法與FPGA原型設(shè)計(jì)密切相關(guān)。

硬件加速與FPGA原型設(shè)計(jì)的融合,形成了硬件輔助驗(yàn)證(HAV)平臺(tái),標(biāo)志著下一階段的到來(lái)。HAV利用硬件加速實(shí)現(xiàn)了大規(guī)模設(shè)計(jì)的快速啟動(dòng)和同步系統(tǒng)的全面調(diào)試——一個(gè)模塊中的一步操作會(huì)觸發(fā)整個(gè)設(shè)計(jì)的協(xié)同推進(jìn)。FPGA原型設(shè)計(jì)則更注重執(zhí)行速度,能夠?qū)崿F(xiàn)與最終設(shè)計(jì)非常接近的復(fù)雜異步操作。盡管這種方法提高了性能,但需要更長(zhǎng)的啟動(dòng)周期。與此同時(shí),分割工具的進(jìn)步使得大規(guī)模原型的開(kāi)發(fā)突破了十億門的門檻。

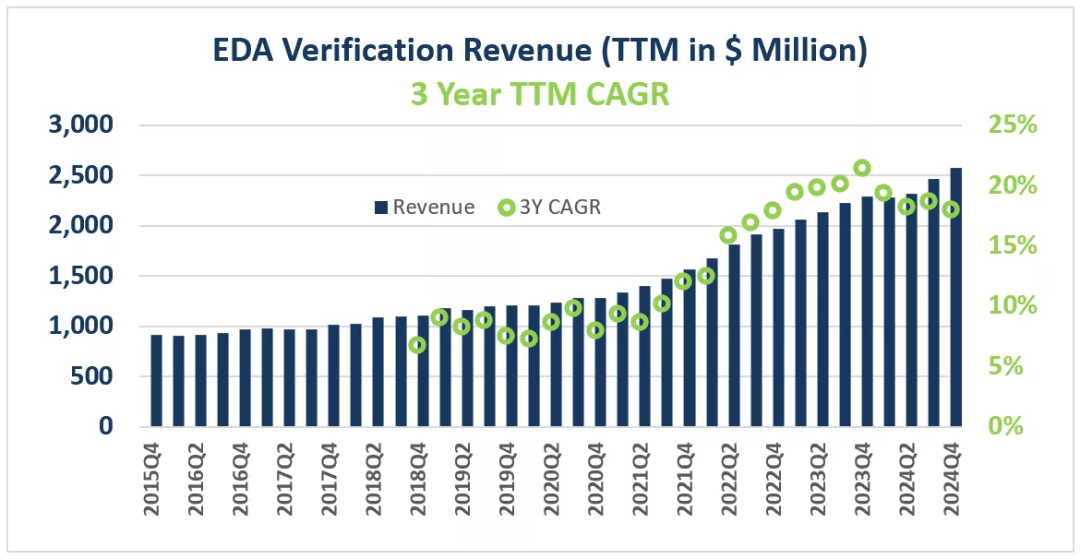

盡管HAV在2010年代中期之前發(fā)展相對(duì)停滯,但自2018年起,HAV的采用率大幅上升,總收入迅速增長(zhǎng),標(biāo)志著HAV開(kāi)始復(fù)興。如下圖所示,在整體驗(yàn)證收入中,HAV是目前占比最大的組成部分。

▲EDA驗(yàn)證收入增長(zhǎng)(來(lái)源:ESDA)

推動(dòng)HAV增長(zhǎng)的因素

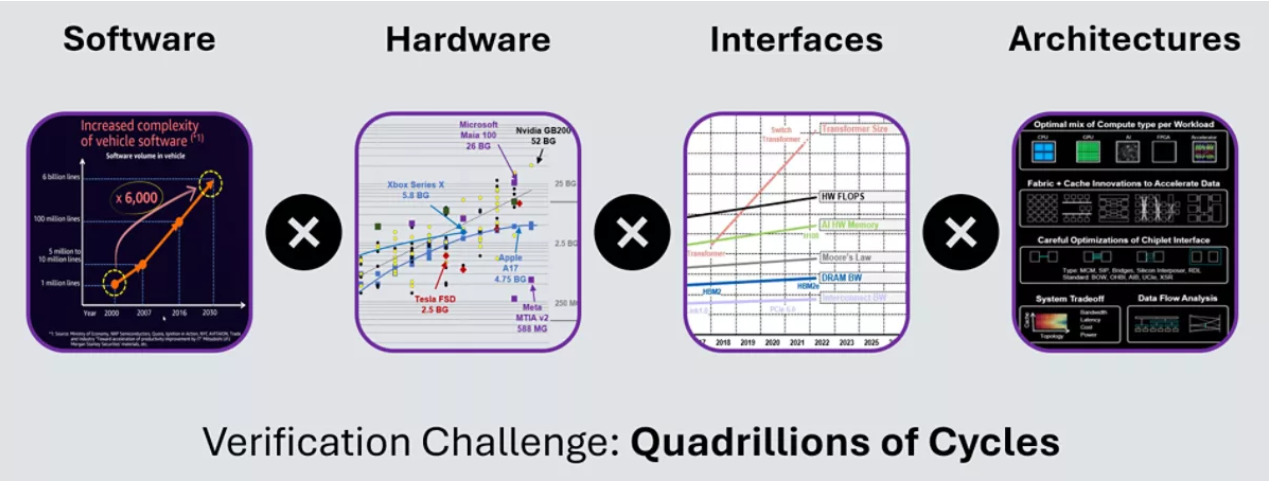

HAV增長(zhǎng)的主要推動(dòng)力在于當(dāng)今片上系統(tǒng)(SoC)的硬件和軟件組件日益復(fù)雜。隨著硬件設(shè)計(jì)規(guī)模的擴(kuò)大,完成全面驗(yàn)證所需的周期數(shù)相應(yīng)增加。軟件的日益密集也迫使進(jìn)行更多測(cè)試,以確保功能和性能。將設(shè)計(jì)復(fù)雜度和軟件復(fù)雜度(即驗(yàn)證周期數(shù))分別繪制在x軸和y軸上,得出的面積即代表總驗(yàn)證工作量。總驗(yàn)證工作量在兩個(gè)維度快速增長(zhǎng),凸顯出對(duì)HAV解決方案日益迫切的需求。

另一個(gè)同樣重要的增長(zhǎng)推動(dòng)力在于新型AI硬件的根本特性。與擅長(zhǎng)運(yùn)行軟件程序的傳統(tǒng)中央處理器(CPU)不同,AI加速器基于專為大規(guī)模并行計(jì)算設(shè)計(jì)的架構(gòu),以滿足機(jī)器學(xué)習(xí)算法的處理需求。

CPU與專用AI加速器之間的本質(zhì)區(qū)別源于它們不同的設(shè)計(jì)理念和目標(biāo)工作負(fù)載。CPU是通用計(jì)算的主力,針對(duì)指令順序處理進(jìn)行了優(yōu)化,尤其擅長(zhǎng)運(yùn)行以逐步執(zhí)行任務(wù)為主的軟件應(yīng)用程序。盡管如今的CPU集成了多個(gè)內(nèi)核以實(shí)現(xiàn)并行處理,但其固有架構(gòu)仍面向串行運(yùn)算,在應(yīng)對(duì)當(dāng)前人工智能需求時(shí)存在擴(kuò)展瓶頸。最尖端的服務(wù)器CPU,如AMD的EPYC系列就采用了這種設(shè)計(jì),內(nèi)核數(shù)高達(dá)192個(gè),但在面對(duì)AI需求時(shí)仍顯不足。

相比之下,AI加速器(包括圖形處理單元GPU、張量處理單元TPU和定制專用集成電路ASIC)在架構(gòu)上專為執(zhí)行AI算法而設(shè)計(jì),能夠同時(shí)處理大型語(yǔ)言模型(LLM)中數(shù)以千億計(jì)的參數(shù)。AI加速器的核心優(yōu)勢(shì)在于能夠同時(shí)執(zhí)行大量計(jì)算,特別是神經(jīng)網(wǎng)絡(luò)計(jì)算中至關(guān)重要的矩陣乘法和卷積操作,需要并行處理海量數(shù)據(jù),而CPU通常難以勝任。

例如,英偉達(dá)的頂尖產(chǎn)品Blackwell GB202 GPU,擁有24,576個(gè)計(jì)算內(nèi)核,就體現(xiàn)了這種范式轉(zhuǎn)變。然而,AI加速器的真正優(yōu)勢(shì)在于其集成到大規(guī)模系統(tǒng)中的能力。CPU的擴(kuò)展受制于軟件和架構(gòu),而AI加速器則不同,可以通過(guò)高帶寬技術(shù)互連,形成統(tǒng)一的處理中心。英偉達(dá)的GB200 NVL72集成了72個(gè)Blackwell GPU和36個(gè)Grace CPU,有效地將單個(gè)系統(tǒng)內(nèi)的AI內(nèi)核總數(shù)推高至一百萬(wàn)個(gè)以上。這種大規(guī)模并行處理能力對(duì)于運(yùn)行復(fù)雜的AI模型至關(guān)重要,因?yàn)樾枰瑫r(shí)處理海量數(shù)據(jù)集并執(zhí)行復(fù)雜計(jì)算。

盡管存在架構(gòu)差異,但CPU和AI加速器都需要通過(guò)執(zhí)行軟件工作任務(wù),進(jìn)行嚴(yán)格的硅前驗(yàn)證。此過(guò)程涉及運(yùn)行業(yè)界基準(zhǔn)程序和最終用戶應(yīng)用程序;AI加速器,還需要運(yùn)行LLM。此外,內(nèi)核間的協(xié)同一致性測(cè)試進(jìn)一步擴(kuò)展了驗(yàn)證范圍。以RISC-V為例,驗(yàn)證ISA擴(kuò)展會(huì)進(jìn)一步增加CPU硅前驗(yàn)證的復(fù)雜性。由于每天需要多次迭代執(zhí)行軟件工作任務(wù),因此為完成全面測(cè)試,需要數(shù)千萬(wàn)億個(gè)驗(yàn)證周期。

AI處理器的驗(yàn)證

在驗(yàn)證AI處理器時(shí),一個(gè)獨(dú)特挑戰(zhàn)在于AI模型具有雙重運(yùn)行模式:訓(xùn)練和推理。訓(xùn)練需要處理海量數(shù)據(jù),以對(duì)深嵌在多層深度神經(jīng)網(wǎng)絡(luò)內(nèi)的網(wǎng)絡(luò)參數(shù)進(jìn)行微調(diào)。該計(jì)算密集型階段可能持續(xù)數(shù)周甚至數(shù)月,要求達(dá)到每秒數(shù)PFLOP吞吐量和TB級(jí)內(nèi)存帶寬。推理階段由于數(shù)據(jù)集較小,因此對(duì)原始計(jì)算的要求不高,但更加注重低延遲,以便在嚴(yán)格的能耗和成本約束下實(shí)現(xiàn)實(shí)時(shí)輸出。

這些運(yùn)算的體量驚人。驗(yàn)證AI硬件加速器和復(fù)雜計(jì)算集群(其中協(xié)同一致性至關(guān)重要)時(shí),通常需要數(shù)千萬(wàn)億個(gè)驗(yàn)證周期,以確保性能、能效、準(zhǔn)確性和可靠性達(dá)到預(yù)期。如此龐大的測(cè)試量遠(yuǎn)遠(yuǎn)超出了軟件仿真工具的能力,在面對(duì)AI工作任務(wù)的復(fù)雜性和并行性時(shí)也顯得力不從心。

▲導(dǎo)致千萬(wàn)億個(gè)驗(yàn)證周期需求的主要因素

HAV化解困局

隨著AI模型越來(lái)越復(fù)雜、工作負(fù)載規(guī)模愈加龐大,部署HAV平臺(tái)勢(shì)在必行。

硬件加速器和FPGA原型提供了周期精確、運(yùn)行高速的環(huán)境運(yùn)行這些工作負(fù)載,使開(kāi)發(fā)者能夠在硅前階段識(shí)別并修正設(shè)計(jì)缺陷。

HAV持續(xù)增長(zhǎng)的原因顯而易見(jiàn):AI的興起引發(fā)了單靠軟件仿真已無(wú)法應(yīng)對(duì)的驗(yàn)證環(huán)節(jié)瓶頸。在通過(guò)實(shí)際工作負(fù)載來(lái)驗(yàn)證復(fù)雜的AI硬件時(shí),面對(duì)速度、容量和可擴(kuò)展性的高要求,軟件仿真和HAV平臺(tái)的角色已然發(fā)生改變。盡管軟件仿真憑借強(qiáng)大的調(diào)試能力,在IP、模塊和子系統(tǒng)設(shè)計(jì)的驗(yàn)證中仍不可替代,但HAV平臺(tái)已經(jīng)成為全系統(tǒng)、Multi-Die和芯粒(即系統(tǒng)之系統(tǒng),SoS)驗(yàn)證的基石,可實(shí)現(xiàn)大規(guī)模的硅前驗(yàn)證。

展望未來(lái)

推動(dòng)HAV崛起的幾個(gè)關(guān)鍵趨勢(shì),將繼續(xù)促進(jìn)HAV的普及。首先,AI模型日益復(fù)雜,新型架構(gòu)(尤其是在內(nèi)存和通信接口方面快速演進(jìn)的架構(gòu))不斷涌現(xiàn),將需要更強(qiáng)大且可擴(kuò)展的驗(yàn)證工具。其次,AI系統(tǒng)對(duì)能效和軟件安全日益重視,將推動(dòng)HAV平臺(tái)的部署,用于在實(shí)際工作負(fù)載中對(duì)峰值和平均功耗進(jìn)行精確分析并開(kāi)展全面的安全驗(yàn)證。再者,AI被廣泛應(yīng)用于自動(dòng)駕駛、醫(yī)療健康等各種場(chǎng)景,針對(duì)不同領(lǐng)域的定制化驗(yàn)證方法將變得愈發(fā)重要。

為了滿足這些不斷變化的需求,HAV平臺(tái)必須采用多項(xiàng)關(guān)鍵創(chuàng)新。AI分析工具將提升錯(cuò)誤檢測(cè)和根本原因分析能力,從而顯著提高驗(yàn)證效率。基于云的硬件加速和原型驗(yàn)證將提供可擴(kuò)展性和可訪問(wèn)性,使設(shè)計(jì)工作流程更加靈活。標(biāo)準(zhǔn)化的驗(yàn)證方法和基準(zhǔn)將促進(jìn)行業(yè)協(xié)作與互操作性。在計(jì)算、AI訓(xùn)練、邊緣AI、汽車、消費(fèi)電子及有線/無(wú)線應(yīng)用領(lǐng)域,由于驗(yàn)證設(shè)置各不相同,模塊化驗(yàn)證對(duì)于管理超過(guò)600億門級(jí)別的超大設(shè)計(jì)和復(fù)雜的SoS配置至關(guān)重要。此外,硬件加速和原型驗(yàn)證的融合將帶來(lái)更順暢和一體化的驗(yàn)證流程。

總之,AI的快速發(fā)展及軟件開(kāi)發(fā)日益增長(zhǎng)的復(fù)雜性與成本,直接促成了硬件輔助驗(yàn)證平臺(tái)的復(fù)興。由于AI硬件加速器在大規(guī)模并行、高算力工作任務(wù)及性能與功耗方面的嚴(yán)苛要求,HAV已成為設(shè)計(jì)過(guò)程中的關(guān)鍵環(huán)節(jié)。

隨著AI不斷發(fā)展并全面滲透現(xiàn)代科技,HAV在確保性能、低功耗、準(zhǔn)確性、可靠性和軟件安全方面的作用將愈發(fā)重要。通過(guò)持續(xù)創(chuàng)新并適應(yīng)AI的發(fā)展趨勢(shì),HAV平臺(tái)將在下一代硬件開(kāi)發(fā)中繼續(xù)發(fā)揮關(guān)鍵作用。

-

FPGA

+關(guān)注

關(guān)注

1643文章

21979瀏覽量

614513 -

硬件

+關(guān)注

關(guān)注

11文章

3463瀏覽量

67238 -

AI

+關(guān)注

關(guān)注

88文章

34378瀏覽量

275616 -

新思科技

+關(guān)注

關(guān)注

5文章

855瀏覽量

51260

原文標(biāo)題:AI 算力革命中,硬件輔助驗(yàn)證(HAV)如何點(diǎn)亮硬件加速之路?

文章出處:【微信號(hào):Synopsys_CN,微信公眾號(hào):新思科技】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

影響電機(jī)使用壽命的關(guān)鍵因素

硬件輔助驗(yàn)證(HAV) 對(duì)軟件驗(yàn)證的價(jià)值

影響接地電阻柜價(jià)格的關(guān)鍵因素?

DeepSeek推動(dòng)AI算力需求:800G光模塊的關(guān)鍵作用

選擇光纖線需考慮哪些關(guān)鍵因素

新思科技推出全新硬件輔助驗(yàn)證產(chǎn)品組合

焊接質(zhì)量評(píng)估:關(guān)鍵因素與檢測(cè)方法綜述

西門子Veloce硬件輔助驗(yàn)證平臺(tái)升級(jí)

鋰電池品牌廠家影響光伏逆變器效率提升的兩個(gè)關(guān)鍵因素

解析選購(gòu)LED大屏幕的關(guān)鍵因素

IT資源遷移到云服務(wù)器的關(guān)鍵因素

工控機(jī)選型的八大關(guān)鍵因素

硅谷VPS優(yōu)勢(shì)及關(guān)鍵因素

超詳細(xì)!晶振電路設(shè)計(jì)的7個(gè)關(guān)鍵因素,小白也能變高手!

推動(dòng)硬件輔助驗(yàn)證平臺(tái)增長(zhǎng)的關(guān)鍵因素

推動(dòng)硬件輔助驗(yàn)證平臺(tái)增長(zhǎng)的關(guān)鍵因素

評(píng)論