1、超時判斷機制

在設(shè)計中,為了增加異常處理能力,保證設(shè)備的正常運行,常常需要進行超時判斷。

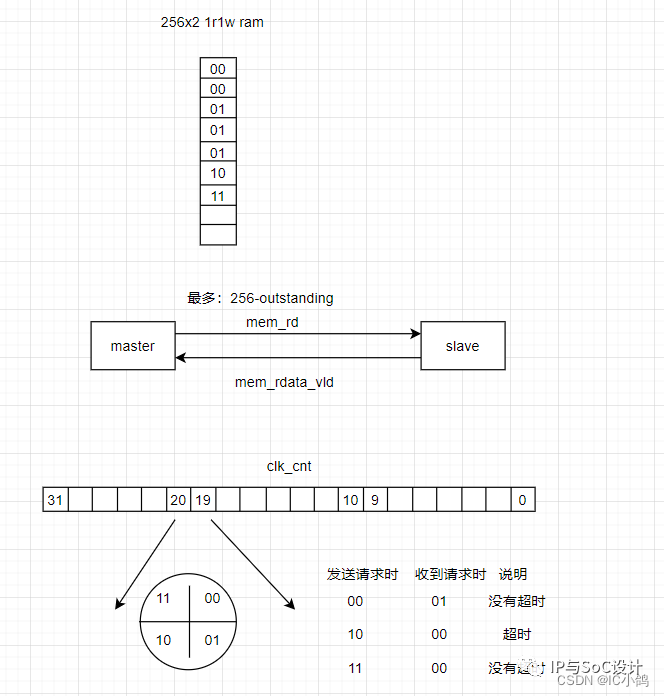

如下圖,當(dāng)master發(fā)起mem讀請求后,收到讀返回數(shù)據(jù)時,進行超時判斷,如果超時,則數(shù)據(jù)丟棄,如果沒有超時,則數(shù)據(jù)正常接收。

2、一種簡單的超時機制

如果在數(shù)據(jù)發(fā)送過程中,發(fā)送者向接收者發(fā)送數(shù)據(jù),通常需要接收者通知發(fā)送者自身是否可以接收數(shù)據(jù)

采用一個公共的32bit clk_cnt作為時間基準,根據(jù)不同的超時精度,采用32bit中的連續(xù)2bit,1GHz時鐘,每個周期1n,例如采用clk_cnt[20:19],可以記錄2^21ns級別的精度,即2ms級別的時間精度。

本文中master能夠發(fā)起256個outstanding請求,req_id[7:0]從0到255,且工作時鐘clk為1Ghz,發(fā)起的mem讀請求,且在1us后都沒有收到數(shù)據(jù),則認為超時。

步驟1:master發(fā)起mem_rd請求時,以req_id作為地址,將clk_cnt[20:19]作為data,寫入256x2 1r1w_ram中。

步驟2:當(dāng)master收到讀返回數(shù)據(jù)時,以req_id作為地址從ram中讀取data,記作clk_cnt_record

步驟3:提取當(dāng)前時刻clk_cnt[20:19],記錄為clk_cnt_now,如果clk_cnt_now-clk_cnt_record 的絕對值大于1,則表示超時。

案例:

clk_cnt_record 為 10,clk_cnt_now為00,則表示超時。

clk_cnt_record 為 10,clk_cnt_now為11,則認為不超時。

3、特點說明

優(yōu)點:此類設(shè)計比較簡單,所需的邏輯資源較少,并且可以調(diào)節(jié)超時時間精度。

缺點:

1.如果超時時間過長,已經(jīng)從clk_cnt_record翻轉(zhuǎn)了一圈再返回時,則無法判斷是否為超時。即clk_cnt_record(10)-->11-->00-->01-->10-->11(clk_cnt_now),實際已超時,但是判斷為沒有超時。

2.沒有讀返回數(shù)據(jù)時,無法判斷是否超時。

verilog語法:幾種可綜合的for循環(huán)語句

1、采用int實現(xiàn)不同信號賦值的循環(huán)

在同一個.v文件中,在不同的場景中,我們想例化不同的ram,如果不使用宏定義,那么該怎么實現(xiàn)呢?

直接采用for(int*)類型格式,可以在一個else分支中使用,不需要使用generate,使用更加靈活,使用范圍更廣。

input [1024-1:0] func_mode_in;reg [512-1:0] func_id_vld;always@(posedge clk)if(~rst_n) beginfunc_id_vld <= 512'b0 ;end else beginfor(int i=0; i<512;i=i+1) begin : func_id_vld_genfunc_id_vld[i] <= (func_mode_in[2*i+:2]==2'b01) ;endend

2、采用int實現(xiàn)同一個信號賦值的循環(huán)

下圖所示,采用for(int*)類型格式實現(xiàn)了一個16mux1的循環(huán)賦值語句,實現(xiàn)不同條件一下,對debug_test_16mux1的賦值操作,即16mux1的邏輯。

input [128*16-1:0] debug_test_in;input [4-1:0] cfg_16mux1_mode;reg [128-1:0] debug_test_16mux1;begindebug_test_16mux1 = 128'd0;i=0; i<16;i=i+1) begin : debug_test_16mux1_gen==i) begindebug_test_16mux1 = debug_test_in[128*i+:128] ;break ;endendend

如上for循環(huán)語句實現(xiàn)了如下的case語句效果

begincase(cfg_16mux1_mode)0 : debug_test_16mux1 = debug_test_in[127 :0 ];1 : debug_test_16mux1 = debug_test_in[255 :128 ];2 : debug_test_16mux1 = debug_test_in[383 :256 ];3 : debug_test_16mux1 = debug_test_in[511 :384 ];4 : debug_test_16mux1 = debug_test_in[639 :512 ];5 : debug_test_16mux1 = debug_test_in[767 :640 ];6 : debug_test_16mux1 = debug_test_in[895 :768 ];7 : debug_test_16mux1 = debug_test_in[1023 :896 ];8 : debug_test_16mux1 = debug_test_in[1151 :1024 ];9 : debug_test_16mux1 = debug_test_in[1279 :1152 ];10: debug_test_16mux1 = debug_test_in[1407 :1280 ];11: debug_test_16mux1 = debug_test_in[1535 :1408 ];12: debug_test_16mux1 = debug_test_in[1663 :1536 ];13: debug_test_16mux1 = debug_test_in[1791 :1664 ];14: debug_test_16mux1 = debug_test_in[1919 :1792 ];15: debug_test_16mux1 = debug_test_in ;endcaseend

NOTE:在for(int*)語句中,debug_test_16mux1 = debug_test_in[128*i+127:128*i] ; 會報語法錯誤,語法錯誤,只識別debug_test_in[128*i+:128]而無法識別debug_test_in[128*i+127:128*i] ,否則VCS會報語法錯誤。

審核編輯 :李倩

-

數(shù)據(jù)

+關(guān)注

關(guān)注

8文章

7239瀏覽量

90990 -

IC設(shè)計

+關(guān)注

關(guān)注

38文章

1346瀏覽量

105234 -

機制

+關(guān)注

關(guān)注

0文章

24瀏覽量

9915

原文標題:IC知識點:超時機制、verilog語法

文章出處:【微信號:IP與SoC設(shè)計,微信公眾號:IP與SoC設(shè)計】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

電機選型計算公式與知識點匯總

嵌入式硬件雜談:推挽、開漏、高阻態(tài)、上拉電阻

MCUX SDK FreeRTOS I2C驅(qū)動程序中沒有超時選項是怎么回事?

一種基于點、線和消失點特征的單目SLAM系統(tǒng)設(shè)計

電氣工程師必知必會的100個電?知識點分享

華邦電子安全閃存關(guān)鍵知識點

Aigtek功率放大器應(yīng)用:電感線圈的知識點分享

后悔沒有早點看到:天線設(shè)計中的知識點!

接口測試理論、疑問收錄與擴展相關(guān)知識點

IC設(shè)計知識點:一種簡單超時機制

IC設(shè)計知識點:一種簡單超時機制

評論