Cadence Allegro現(xiàn)在幾乎已成為高速板設(shè)計(jì)中實(shí)際上的工業(yè)標(biāo)準(zhǔn),最新版本是Allegro 16.5。與其前端產(chǎn)品Capture相結(jié)合,可完成高速、高密度、多層的復(fù)雜 PCB 設(shè)計(jì)布線工作。

01

Q:高頻信號(hào)布線時(shí)要注意哪些問題?

A:信號(hào)線的阻抗匹配;與其他信號(hào)線的空間隔離;對(duì)于數(shù)字高頻信號(hào),差分線效果會(huì)更好。

02

Q:在布板時(shí),如果線密,孔就可能要多,當(dāng)然就會(huì)影響板子的電氣性能,怎樣提高板子的電氣性能?

A:對(duì)于低頻信號(hào),過孔不要緊,高頻信號(hào)盡量減少過孔。如果線多可以考慮多層板。

03

Q:是不是板子上加的去耦電容越多越好?

A:去耦電容需要在合適的位置加合適的值。例如,在模擬器件的供電端口就需要加,并且需要用不同的電容值去濾除不同頻率的雜散信號(hào)。

04

Q:一個(gè)好的板子它的標(biāo)準(zhǔn)是什么?

A:布局合理、電源線功率冗余度足夠、高頻阻抗、低頻走線簡潔。

05

Q:通孔和盲孔對(duì)信號(hào)的差異影響有多大?應(yīng)用的原則是什么?

A:采用盲孔或埋孔是提高多層板密度、減少層數(shù)和板面尺寸的有效方法,并大大減少了鍍覆通孔的數(shù)量。

但相比較而言,通孔在工藝上好實(shí)現(xiàn),成本較低,所以一般設(shè)計(jì)中都使用通孔。

06

Q:在涉及模擬數(shù)字混合系統(tǒng)的時(shí)候,有人建議電層分割,地平面采取整片敷銅,也有人建議電地層都分割,不同的地在電源端點(diǎn)接,但是這樣對(duì)信號(hào)的回流路徑就遠(yuǎn)了,具體應(yīng)用時(shí)應(yīng)如何選擇合適的方法?

A:如果有高頻》20MHz信號(hào)線,并且長度和數(shù)量都比較多,那么需要至少兩層給這個(gè)模擬高頻信號(hào)。一層信號(hào)線,一層大面積地,并且信號(hào)線層需要打足夠的過孔到地。這樣的目的是:

對(duì)于模擬信號(hào),這提供了一個(gè)完整的傳輸介質(zhì)和阻抗匹配;

地平面把模擬信號(hào)和其他數(shù)字信號(hào)進(jìn)行隔離;

地回路足夠小,因?yàn)槟愦蛄撕芏噙^孔,地又是一個(gè)大平面。

07

Q:在電路板中,信號(hào)輸入插件在PCB最左邊沿,MCU在靠右邊,那么在布局時(shí)是把穩(wěn)壓電源芯片放置在源靠近接插件(電源 IC輸出5V經(jīng)過一段比較長的路徑才到達(dá)MCU),還是把電源IC放置到中間偏右(電源IC的輸出5V的線到達(dá)MCU就比較短,但輸入電源段線就經(jīng)過比較長一段PCB板)?或是有更好的布局?

A:首先信號(hào)輸入插件是否是模擬器件?如果是模擬器件,建議電源布局應(yīng)盡量不影響到模擬部分的信號(hào)完整性。因此有幾點(diǎn)需要考慮:

首先穩(wěn)壓電源芯片是否是比較干凈,紋波小的電源?模擬部分的供電,對(duì)電源的要求比較高;

模擬部分和MCU是否是一個(gè)電源,在高精度電路的設(shè)計(jì)中,建議把模擬部分和數(shù)字部分的電源分開;

對(duì)數(shù)字部分的供電需要考慮到盡量減小對(duì)模擬電路部分的影響。

08

Q:在高速信號(hào)鏈的應(yīng)用中,對(duì)于多ASIC都存在模擬地和數(shù)字地,究竟是采用地分割,還是不分割地?既有準(zhǔn)則是什么?哪種效果更好?

A:迄今為止沒有定論。一般情況下可以查閱芯片的手冊(cè)。ADI所有混合芯片的手冊(cè)中都是推薦你一種接地的方案,有些是推薦共地、有些是建議隔離地,這取決于芯片設(shè)計(jì)。

09

Q:何時(shí)要考慮線的等長?如果要考慮使用等長線的話,兩根信號(hào)線之間的長度之差最大不能超過多少?如何計(jì)算?

A:差分線計(jì)算思路:如果傳一個(gè)正弦信號(hào),長度差等于它傳輸波長的一半,相位差就是180度,這時(shí)兩個(gè)信號(hào)就完全抵消了。所以這時(shí)的長度差是最大值。以此類推,信號(hào)線差值一定要小于這個(gè)值。

10

Q:高速中的蛇形走線,適合在哪種情況?有什么缺點(diǎn)沒?比如對(duì)于差分走線,又要求兩組信號(hào)是正交的。

A:蛇形走線,因?yàn)閼?yīng)用場合不同而具有不同的作用:

如果蛇形走線在計(jì)算機(jī)板中出現(xiàn),其主要起到一個(gè)濾波電感和阻抗匹配的作用,用于提高電路的抗干擾能力。計(jì)算機(jī)主機(jī)板中的蛇形走線,主要用在一些時(shí)鐘信號(hào)中,如PCI-Clk、AGPCIK、IDE、DIMM等信號(hào)線。

若在一般普通PCB板中,除了具有濾波電感的作用外,還可作為收音機(jī)天線的電感線圈等等。如2.4G的對(duì)講機(jī)中就用作電感。

對(duì)一些信號(hào)布線長度要求必須嚴(yán)格等長,高速數(shù)字PCB板的等線長是為了使各信號(hào)的延遲差保持在一個(gè)范圍內(nèi),保證系統(tǒng)在同一周期內(nèi)讀取的數(shù)據(jù)的有效性(延遲差超過一個(gè)時(shí)鐘周期時(shí)會(huì)錯(cuò)讀下一周期的數(shù)據(jù))。

如INTELHUB架構(gòu)中的HUBLink,一共13根,使用233MHz的頻率,要求必須嚴(yán)格等長,以消除時(shí)滯造成的隱患,繞線是惟一的解決辦法。

一般要求延遲差不超過1/4時(shí)鐘周期,單位長度的線延遲差也是固定的,延遲跟線寬、線長、銅厚、板層結(jié)構(gòu)有關(guān),但線過長會(huì)增大分布電容和分布電感,使信號(hào)質(zhì)量有所下降。所以時(shí)鐘 IC引腳一般都接端接,但蛇形走線并非起電感的作用。

相反地,電感會(huì)使信號(hào)中的上升沿中的高次諧波相移,造成信號(hào)質(zhì)量惡化,所以要求蛇形線間距最少是線寬的兩倍。信號(hào)的上升時(shí)間越小,就越易受分布電容和分布電感的影響。

蛇形走線在某些特殊的電路中起到一個(gè)分布參數(shù)的LC濾波器的作用。

11

Q:在設(shè)計(jì)PCB時(shí),如何考慮電磁兼容性EMC/EMI,具體需要考慮哪些方面?采取哪些措施?

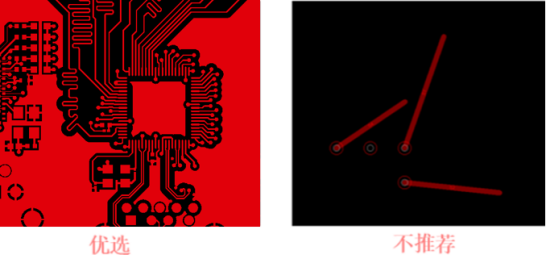

A:EMI/EMC設(shè)計(jì)必須一開始布局時(shí)就要考慮到器件的位置,PCB疊層的安排,重要聯(lián)機(jī)的走法, 器件的選擇等。

例如時(shí)鐘發(fā)生器的位置盡量不要靠近對(duì)外的連接器,高速信號(hào)盡量走內(nèi)層并注意特性阻抗匹配與參考層的連續(xù)以減少反射,器件所推的信號(hào)之斜率(slew rate)盡量小以降低高頻成分,選擇去耦合(decoupling/bypass)電容時(shí)注意其頻率響應(yīng)是否符合需求以降低電源層噪聲。

另外,注意高頻信號(hào)電流之回流路徑使其回路面積盡量小(也就是回路阻抗loop impedance盡量小)以減少輻射。還可以用分割地層的方式以控制高頻噪聲的范圍。

最后,適當(dāng)?shù)倪x擇PCB與外殼的接地點(diǎn)(chassis ground)。

12

Q:請(qǐng)問射頻寬帶電路PCB的傳輸線設(shè)計(jì)有何需要注意的地方?傳輸線的地孔如何設(shè)置比較合適,阻抗匹配是需要自己設(shè)計(jì)還是要和PCB加工廠家合作?

A:這個(gè)問題要考慮很多因素。比如PCB材料的各種參數(shù),根據(jù)這些參數(shù)最后建立的傳輸線模型,器件的參數(shù)等。阻抗匹配一般要根據(jù)廠家提供的資料來設(shè)計(jì)。

13

Q:在模擬電路和數(shù)字電路并存的時(shí)候,如一半是FPGA或單片機(jī)數(shù)字電路部分,另一半是DAC和相關(guān)放大器的模擬電路部分。各種電壓值的電源較多,遇到數(shù)模雙方電路都要用到的電壓值的電源,是否可以用共同的電源,在布線和磁珠布置上有什么技巧?

A:一般不建議這樣使用,這樣使用會(huì)比較復(fù)雜,也很難調(diào)試。

14

Q:在進(jìn)行高速多層PCB設(shè)計(jì)時(shí),關(guān)于電阻電容等器件的封裝的選擇的,主要依據(jù)是什么?常用哪些封裝,能否舉幾個(gè)例子。

A:0402是手機(jī)常用;0603是一般高速信號(hào)的模塊常用;依據(jù)是封裝越小寄生參數(shù)越小,當(dāng)然不同廠家的相同封裝在高頻性能上有很大差異。建議你在關(guān)鍵的位置使用高頻專用元件。

15

Q:一般在設(shè)計(jì)中雙面板是先走信號(hào)線還是先走地線?

A:這個(gè)要綜合考慮。在首先考慮布局的情況下,考慮走線。

16

Q:在進(jìn)行高速多層PCB設(shè)計(jì)時(shí),最應(yīng)該注意的問題是什么?能否做詳細(xì)說明問題的解決方案。

A:最應(yīng)該注意的是設(shè)計(jì),就是信號(hào)線、電源線、地、控制線這些你是如何劃分在每個(gè)層的。

一般的原則是模擬信號(hào)和模擬信號(hào)地至少要保證單獨(dú)的一層。電源也建議用單獨(dú)一層。

17

Q:請(qǐng)問具體何時(shí)用2層板,4層板,6層板?在技術(shù)上有沒有嚴(yán)格的限制(除去體積原因)?是以CPU的頻率為準(zhǔn)還是其和外部器件數(shù)據(jù)交互的頻率為準(zhǔn)?

A:采用多層板首先可以提供完整的地平面,另外可以提供更多的信號(hào)層,方便走線。

對(duì)于CPU要去控制外部存儲(chǔ)器件的應(yīng)用,應(yīng)以交互的頻率為考慮,如果頻率較高,完整的地平面是一定要保證的,此外信號(hào)線最好要保持等長。

18

Q:PCB布線對(duì)模擬信號(hào)傳輸?shù)挠绊懭绾畏治觯绾螀^(qū)分信號(hào)傳輸過程中引入的噪聲是布線導(dǎo)致還是運(yùn)放器件導(dǎo)致?

A:這個(gè)很難區(qū)分,只能通過PCB布線來盡量避免布線引入額外噪聲。

19

Q:對(duì)高速多層PCB來說,電源線、地線與信號(hào)線的線寬設(shè)置為多少是合適的,常用設(shè)置是怎樣的,能舉例說明嗎?例如工作頻率在300Mhz的時(shí)候該怎么設(shè)置?

A:300MHz的信號(hào)一定要做阻抗仿真計(jì)算出線寬和線和地的距離;電源線需要根據(jù)電流的大小決定線寬,在混合信號(hào)PCB的時(shí)候一般就不用“線”來表示地了,而是用整個(gè)平面,這樣才能保證回路電阻最小,并且信號(hào)線下面有一個(gè)完整的平面。

20

Q:怎樣的布局才能達(dá)到最好的散熱效果?

A:PCB中熱量的來源主要有三個(gè)方面:電子元器件的發(fā)熱;PCB本身的發(fā)熱;其它部分傳來的熱。

在這三個(gè)熱源中,元器件的發(fā)熱量最大,是主要熱源,其次是PCB板產(chǎn)生的熱,外部傳入的熱量取決于系統(tǒng)的總體熱設(shè)計(jì),暫時(shí)不做考慮。

那么熱設(shè)計(jì)的目的是采取適當(dāng)?shù)拇胧┖头椒ń档驮骷臏囟群蚉CB板的溫度,使系統(tǒng)在合適的溫度下正常工作。主要是通過減小發(fā)熱,和加快散熱來實(shí)現(xiàn)。

審核編輯 :李倩

-

電路板

+關(guān)注

關(guān)注

140文章

5086瀏覽量

101489 -

PCB設(shè)計(jì)

+關(guān)注

關(guān)注

396文章

4775瀏覽量

89175 -

去耦電容

+關(guān)注

關(guān)注

11文章

319瀏覽量

22810

原文標(biāo)題:Cadence使用技巧!PCB設(shè)計(jì)布線靈魂拷問20條!

文章出處:【微信號(hào):電子工程師寶典,微信公眾號(hào):硬件加油站】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

必學(xué)!PCB設(shè)計(jì)布線技巧、電機(jī)控制、電源管理設(shè)計(jì)教程等精華資料

每周推薦!PCB設(shè)計(jì)布線技巧、電機(jī)控制、電源管理芯片設(shè)計(jì)教程等精華資料

建議收藏,這31條PCB設(shè)計(jì)布線技巧

【PCB】四層電路板的PCB設(shè)計(jì)

電子工程師的PCB設(shè)計(jì)經(jīng)驗(yàn)

104條關(guān)于PCB布局布線的小技巧

12條PCB設(shè)計(jì)規(guī)則

專業(yè)PCB設(shè)計(jì),高速PCB設(shè)計(jì),PCB設(shè)計(jì)外包, PCB Layout,PCB Design,PCB畫板公司,PCB設(shè)計(jì)公司,迅安通科技公司介紹

AM62 PCB設(shè)計(jì)逃逸布線應(yīng)用說明

AM62x(AMC)PCB設(shè)計(jì)逃逸布線應(yīng)用說明

AM62Px PCB設(shè)計(jì)迂回布線

AM62x SiP PCB設(shè)計(jì)迂回布線

PCB設(shè)計(jì)布線靈魂拷問20條!

PCB設(shè)計(jì)布線靈魂拷問20條!

評(píng)論