為什么封裝現在很重要

封裝曾經是半導體制造過程中的事后想法,不被大家重視。當你創造了這一小塊神奇的硅片之后,然后把他用某種方法封裝起來,同時引出管腳,一顆芯片就誕生了。但是隨著摩爾定律的延伸,工程師們意識到,他們可以利用對芯片的所有部分,包括封裝在內進行優化和創新,來制造出最好的產品。

更令人驚訝的是,過去沒有一家封裝公司被認為像傳統的前端制造工藝那樣重要。封裝供應鏈通常被認為是"后端",并被視為成本中心,類似于銀行業的前臺和后臺。但現在,隨著前端難以更好的縮小芯片尺寸,一個全新的關注領域已經出現,這就是對先進封裝的重視。

接下來我們討論一下封裝的發展簡史,從簡單的DIP封裝一直到先進的2.5D或3D封裝。

封裝發展簡介

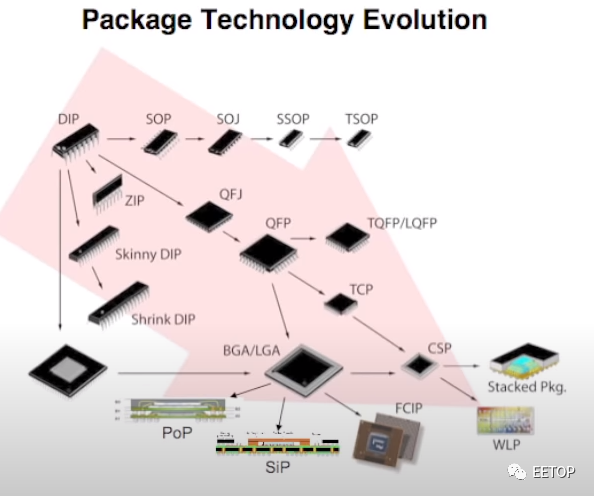

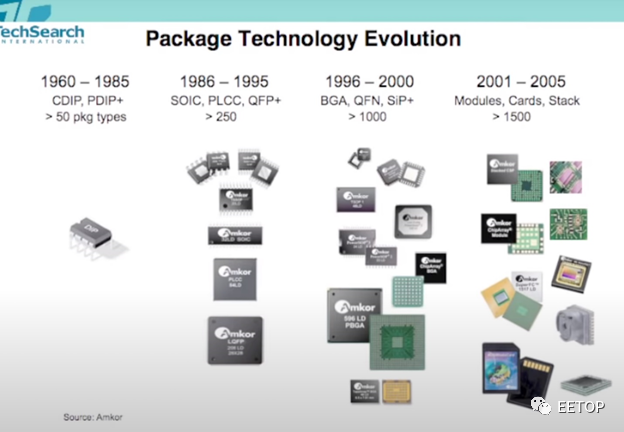

這是我從這個精彩的視頻座中發現的封裝技術的簡要層次結構。如果你有一些時間,可以看一下。(視頻發表于2012年,但是當時已經提到了現在最新的3D封裝技術,所以并不過時)

封裝技術一個簡化的演變過程是:DIP>QFP>BGA>POP/SiP>WLP

顯然,有很多不同的封裝技術,但我們要討論的是大致能代表每種類型的簡單技術,然后慢慢將其帶到現在。我也非常喜歡下圖這個高層次的概述(不過它已經過時了,但仍然正確)。

在封裝的最初階段,裸片通常采用陶瓷或金屬罐封(氣密),以實現最大的可靠性。這主要適用于航空航天和軍事應用,這些功能需要最高水平的可靠性。然而,對于我們的大多數日常用例來說,這并不是真正可行的,所以我們開始使用塑料封裝和雙列直插封裝(DIP)。

DIP封裝(1964-1980年代)

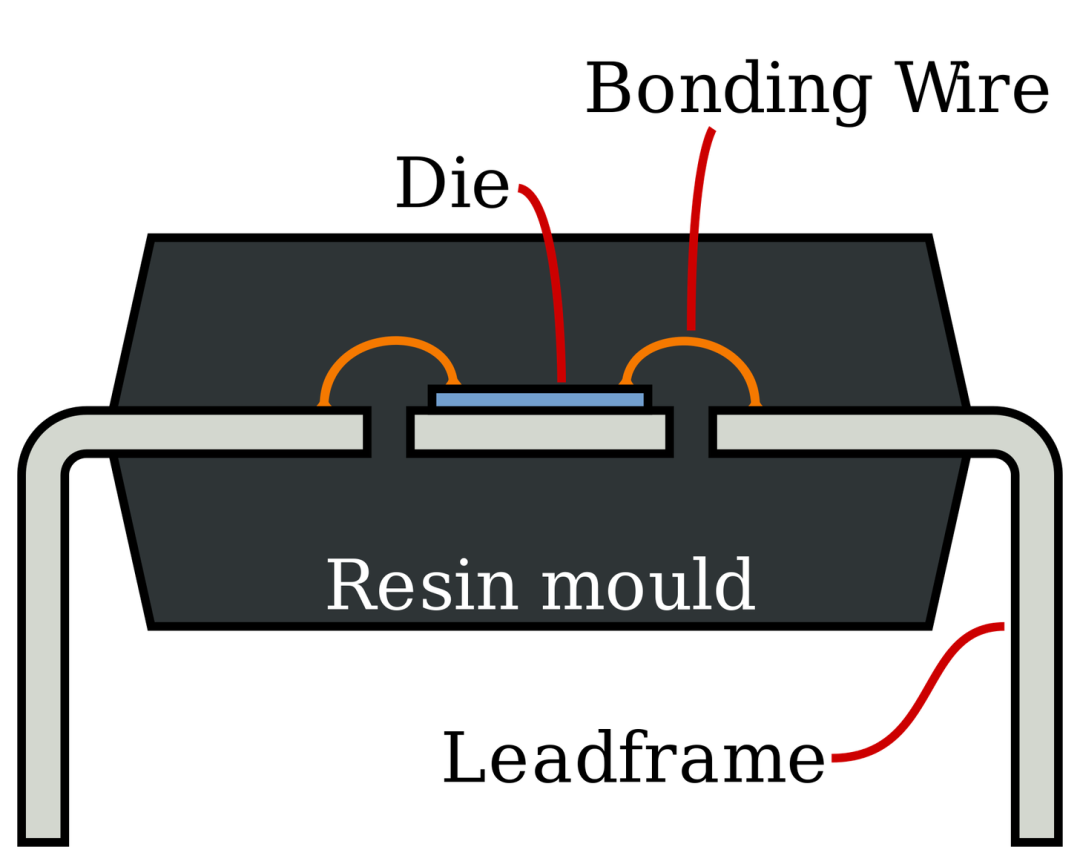

最早的DIP包裝元件是由仙童半導體司的Bryant Buck Rogers在1964年時發明,在表面貼裝技術問世之前的十年里,它被廣泛應用。DIP在實際的裸片周圍使用塑料封裝外殼(編輯注:實際上陶瓷封裝的軍品芯片也大批采用了DIP封裝),并有兩排平行的突出的引腳,稱為引線框架,與下面的PCB(印刷電路板)相連。

實際的芯片通過鍵合線連接到兩個引線框架,兩個引線框架可以連接到印刷電路板(PCB)。DIP封裝以復古的方式具有標志性,設計選擇是可以理解的。實際的裸片將完全密封在樹脂中,因此它帶來了高可靠性和低成本,并且許多首批標志性的半導體都是以這種方式封裝的。請注意,芯片通過導線連接到外部引線框架,這使其成為一種"引線鍵合"封裝方法。稍后將對此進行詳細介紹。

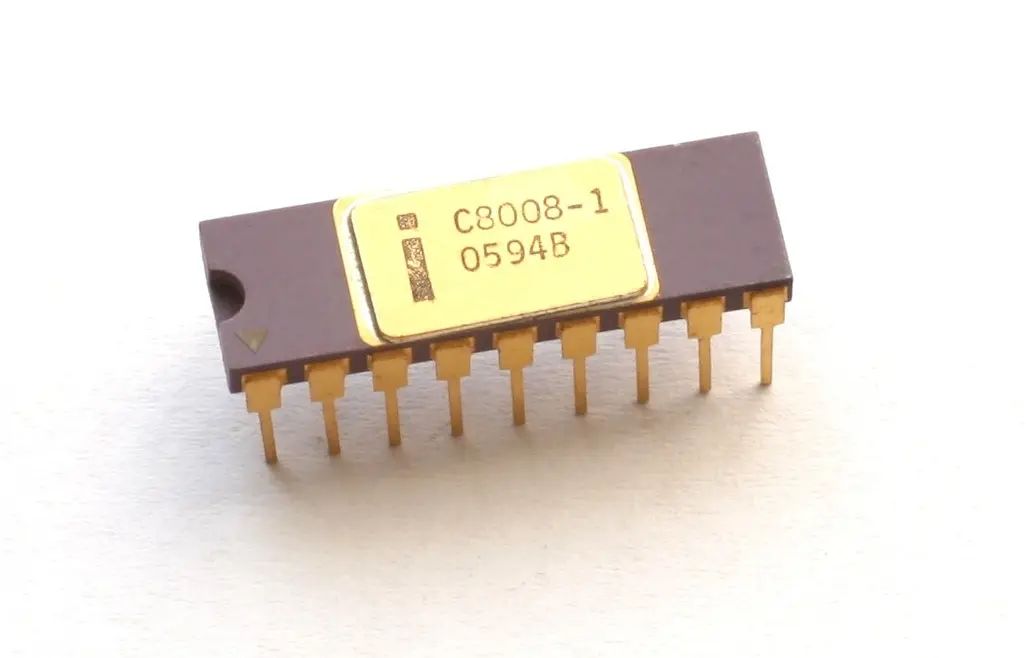

下面是英特爾8008--實際上是第一批現代微處理器之一。注意它的標志性DIP封裝。因此,如果你看到那些看起來像小蜘蛛的半導體的時髦照片,這只是一個DIP封裝類的半導體。

英特爾的原始微處理器,8008 家族

然后,這些小金插針中的每一個都被焊接到PCB上,在那里它與其他電氣元件和系統的其余部分接觸。以下是封裝如何焊接到PCB板上。

PCB本身通常是由銅或其他電氣元件由非導電材料層壓而成。然后,PCB板可以將電信號從一個地方輸送到另一個地方,并讓個元件相互連接和通信。

雖然DIP還有其他演繹版,但實際上是時候轉向始于20世紀80年代的下一個封裝技術范式或表面貼裝封裝了。

表面貼裝封裝(1980-1990年代)

下一步的變化不是通過DIP安裝產品,而是引入表面貼裝技術(SMT)。正如所暗示的那樣,封裝直接安裝在PCB的表面上,并允許在一塊基板上使用更多的元件并降低成本。下圖是典型的表面貼裝封裝。

這種封裝有許多變體,在半導體創新的鼎盛時期,這一直是很長一段時間的主力。值得注意的是,大部分芯片都是4個側面都有引腳。這遵循了封裝的一般愿望,即占用更少的空間并增加連接帶寬或I / O。每一項額外的進步都會考慮到這一點,并且是一種值得關注的模式。

這個過程曾經是手動的,但現在是高度自動化的。此外,這實際上為PCB創造了相當多的問題,如popcorning。封裝爆裂是指在焊接過程中,塑料封裝內的水分被加熱,由于快速加熱和冷卻,水分在PCB上造成問題。另一件需要注意的事情是,隨著封裝工藝的每一次提升,復雜性和故障也會隨之增加

球柵封裝和芯片級封裝(1990年代至2000年代)

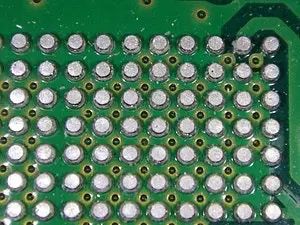

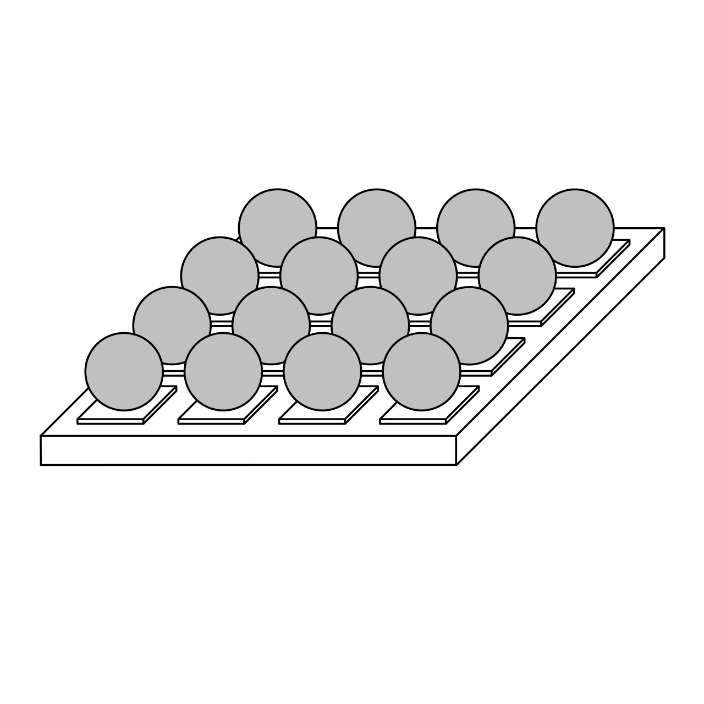

隨著對半導體速度的需求不斷提高,對更好封裝的需求也在不斷增加。雖然出現了QFN(四方扁平無引線)和其他表面貼裝技術,但我想向你介紹一種我們在未來必須了解的封裝設計的開端,這就是廣泛使用的球柵陣列(BGA)封裝的開始。

這些焊球或凸起被稱為焊料凸起/球

這就是球柵陣列的外觀,可以從下面直接將一塊硅片安裝到PCB或基板上,而不是像以前的表面貼裝技術那樣簡單地將所有4端的角落貼上膠帶。

因此,這只是我上面列出的趨勢的另一個延續,占用更少的空間,有更多的連接。現在,我們不再是用電線細細地連接每一側的封裝,而是直接將一個封裝連接到另一個。這導致了密度的增加,更好的I/O性能,以及現在增加的復雜性,即你如何檢查BGA封裝是否工作。在這之前,封裝主要是通過視覺檢查和測試。現在我們無法看到封裝,所以沒有辦法進行測試。我們可以X射線進行檢查,以及更復雜的技術。

現代封裝(2000-2010年代)

我們現在走進了現代封裝的時代。

上面描述的許多封裝方案今天仍在使用,但是,您將開始看到越來越多的封裝類型,并且這些封裝類型將來會變得更加相關。公平地說,許多這些即將到來的技術是在過去幾十年中發明的,但由于成本原因,直到后來才被廣泛使用。

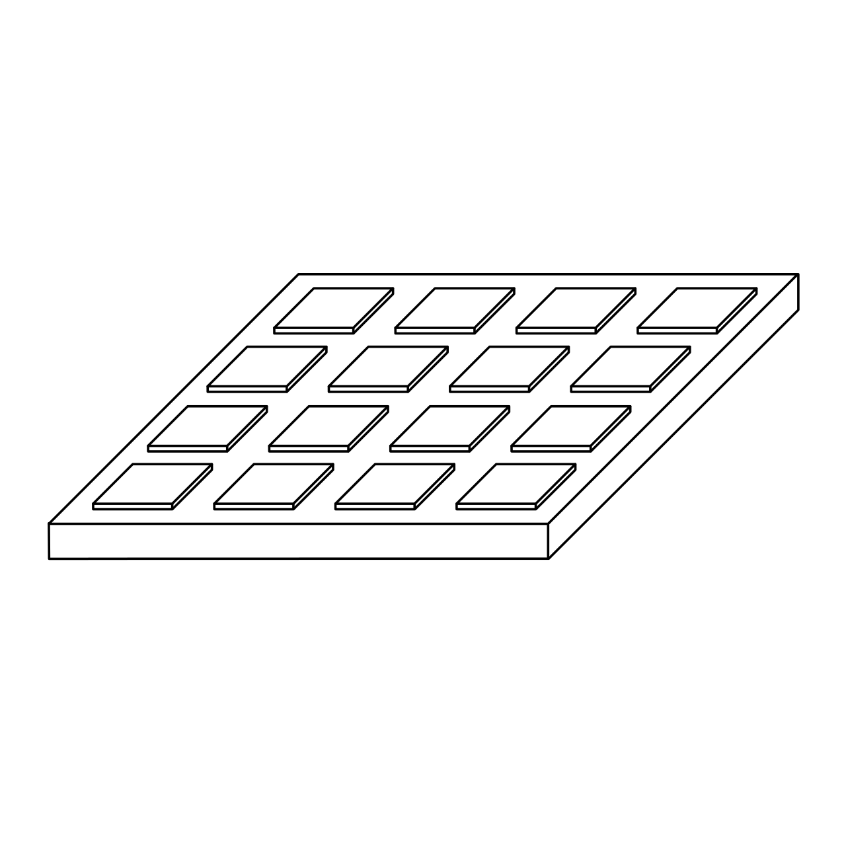

倒裝芯片

這是你可能會讀到或聽到的最常見的封裝之一。我很高興能為你定義它,因為到目前為止,我讀過的入門書中還沒有一個令人滿意的解釋。倒裝芯片是IBM很早就發明的,通常會被縮寫為C4。就倒裝芯片而言,它確實不是一種獨立的封裝形式,而是一種封裝風格。它幾乎就是只要在芯片上有一個焊接凸點就可以了。芯片不是用線粘合互連,而是翻轉過來面對另一個芯片,中間有一個連接基板,所以叫 "倒裝芯片"。

從維基百科上的解釋內容可以更好的理解什么是倒裝芯片:

1. 在晶圓上創建集成電路

2. 芯片表面的焊盤被金屬化

3. 每個焊盤上都沉積一個焊點

4. 芯片被切割

5. 芯片被翻轉和定位,以便焊球面向電路

6. 然后將焊球重新熔化

7.安裝好的芯片用電絕緣膠進行底部填充

引線鍵合請注意倒裝芯片與引線鍵合有何不同。上面介紹的DIP封裝這就是引線鍵合,其中芯片使用導線鍵合到另一種金屬上,然后焊接到PCB上。引線鍵合不是一種特定的技術,而是一套較舊的技術,涵蓋了許多不同類型的封裝。引線鍵合是倒裝芯片的前身。

先進封裝(2010年代至今)

我們一直在緩慢地進入"先進封裝"半導體時代,我現在想談談一些更高級的概念。實際上,有各種層次的"封裝"適合這個思維過程。我們之前講過的大多數封裝,都集中在芯片封裝到PCB上,但先進封裝的開始其實是從手機開始的。

手機在很多方面都是先進封裝諸多方面的巨大前奏。這是有道理的!對于手機需要在盡可能小的空間內集成大量的芯片,比筆記本電腦或臺式電腦密度大得多。所有東西都必須被動冷卻,當然也要盡可能薄。這將封裝推向了新的極限。我們討論的許多概念都是從智能手機封裝開始的,現在已經將自己推向了半導體行業的其他部分。

芯片級封裝(CSP)

芯片級封裝實際上比聽起來要寬一些,最初意味著芯片大小的封裝。技術定義是封裝尺寸不超過芯片本身的1.2倍,并且必須是單芯片且可連接的。實際上,我已經向您介紹了CSP的概念,那就是通過倒裝芯片。但CSP確實通過智能手機提升到了一個新的水平。

這張照片中的所有東西都是芯片芯片的1.2倍大小,并且專注于節省盡可能多的空間。CSP時代有很多不同的風格,包括倒裝芯片、右基板和其他技術,都屬于這一類。

晶圓級封裝(WLP)

但還有一個更小的級別--這就是 "終極 "芯片規模的封裝尺寸,或在晶圓級封裝。這幾乎就是把封裝放在實際的硅片本身。封裝的就是硅片。它更薄,具有最高水平的I/O,而且顯然會非常熱,很難制造。先進的封裝革命目前是在CSP的規模上,但未來將集中在晶圓上。

這是一個有趣的演變,封裝被實際的硅本身所包含。芯片是封裝,反之亦然。與僅僅將一些球焊接到芯片上相比,這真的很昂貴,那么我們為什么要這樣做呢?為什么現在對先進封裝如此癡迷?

先進封裝:未來

這是我長期以來一直在描述的趨勢的一個頂峰。異構計算不僅是專業化要做的事,而且是我們如何將所有這些專業化的碎片放在一起的事。先進的封裝是使這一切發揮作用的關鍵推動因素。

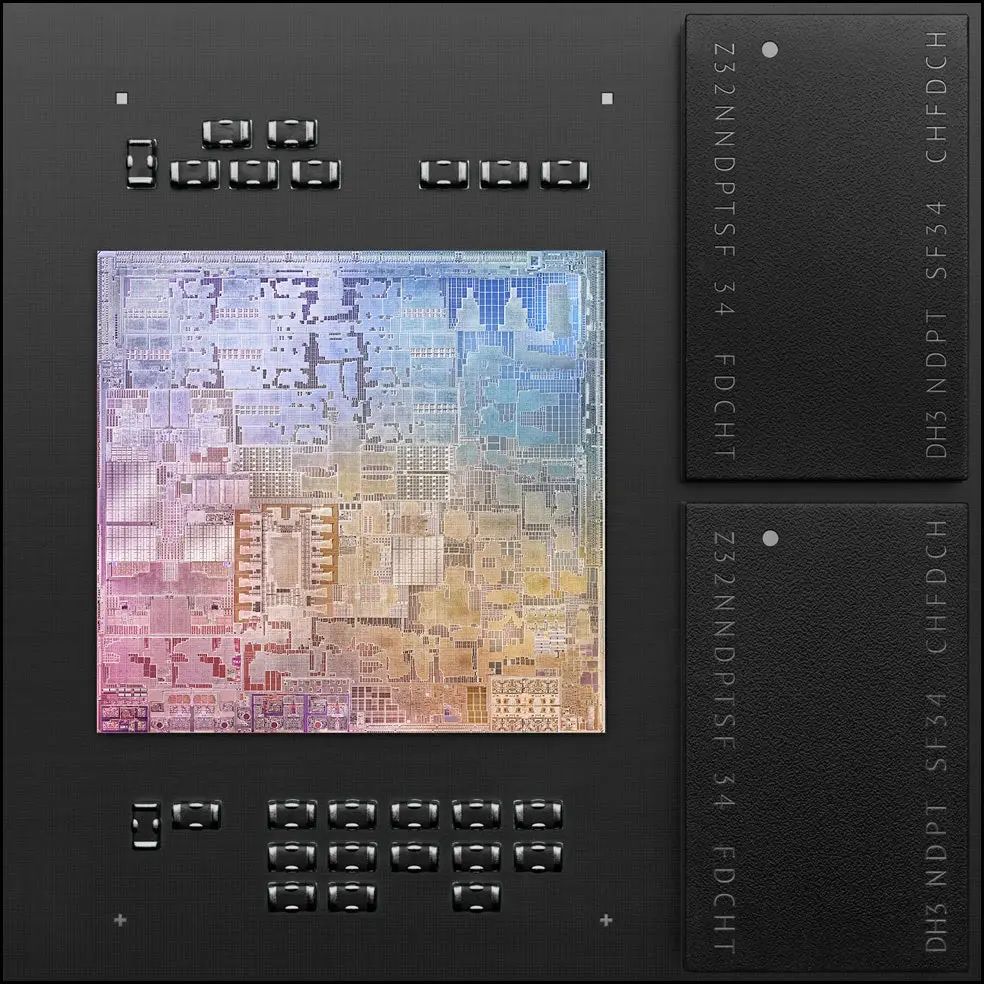

讓我們來看看蘋果M1 - 一種經典的異構計算配置,特別是其統一的內存結構。對我來說,M1的誕生不是一個 "嘩眾取寵 "的時刻,而是異構計算即將爆發的一個奇特時刻。

M1正在敲響未來的樣子,許多人很快就會效仿蘋果的做法。請注意,實際的SOC(片上系統)不是異構的--但是將內存靠近SOC的定制封裝是異構的。

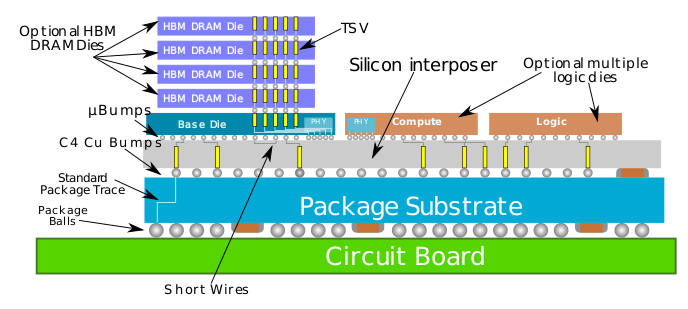

M1采用2.5D封裝將內存直接封裝到處理旁邊,不需要PCB連線,

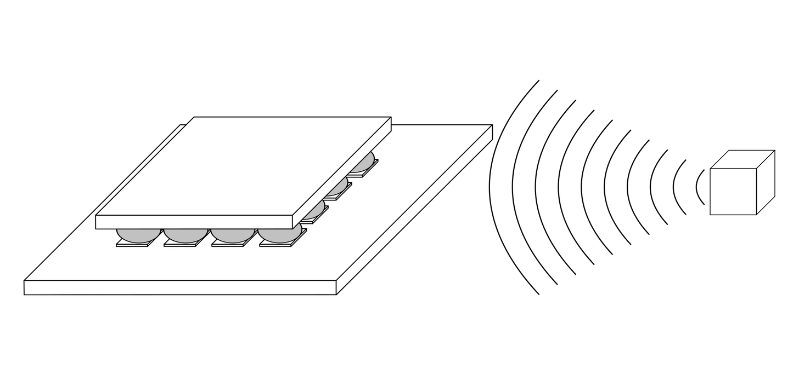

另一個非常好的高級封裝的好例子是Nvidia的新款A100。再次注意到PCB上沒有電線。

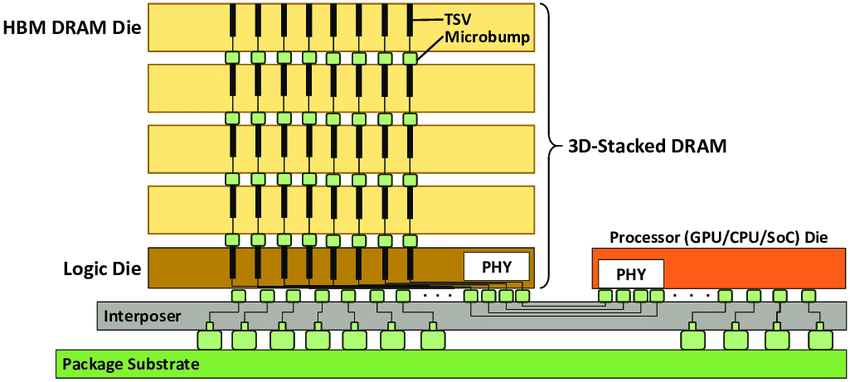

HBM2 不像傳統的 GDDR5 GPU 板設計那樣需要圍繞 GPU 的大量離散內存芯片,而是包括一個或多個多個內存芯片的垂直堆棧。存儲芯片使用微小的導線進行連接,這些導線由硅通孔和微凸起形成。一個 8 Gb HBM2 芯片包含 5,000 多個硅通孔。然后使用無源硅中介層連接內存堆棧和GPU芯片。HBM2 堆棧、GPU 芯片和硅中介層的組合封裝在單個 55mm x 55mm BGA 封裝中。有關 GP100 和兩個 HBM2 堆棧的圖示,請參見圖 9;有關具有 GPU 和內存的實際 P100 的顯微照片,請參見圖 10。

這里的結論是,世界上最好的芯片都是用一種方式制造出來的,而且這種革命不會停止。接下來介紹高級封裝的兩個主要類別,2.5D和3D封裝。

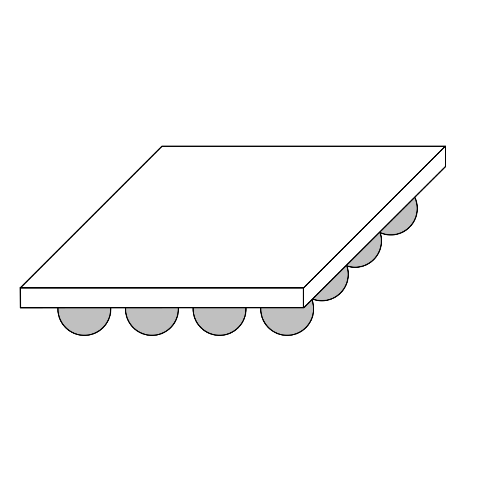

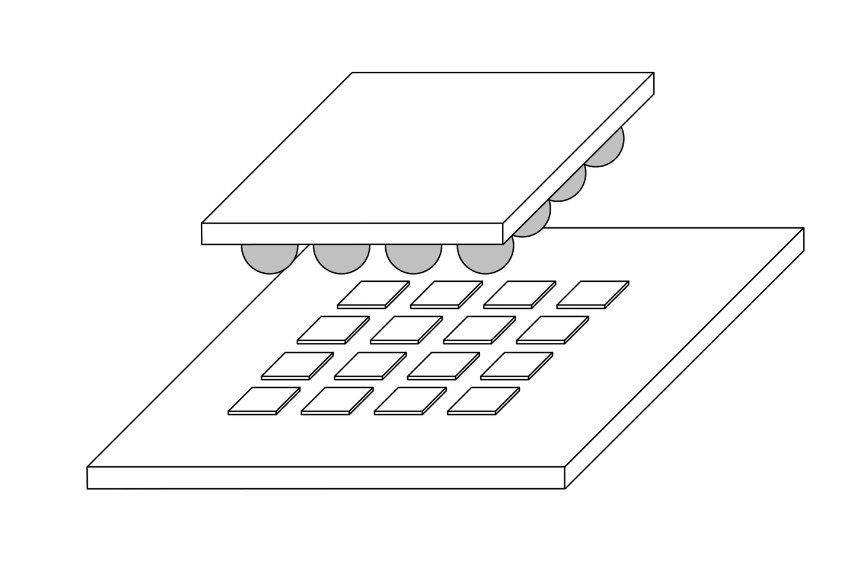

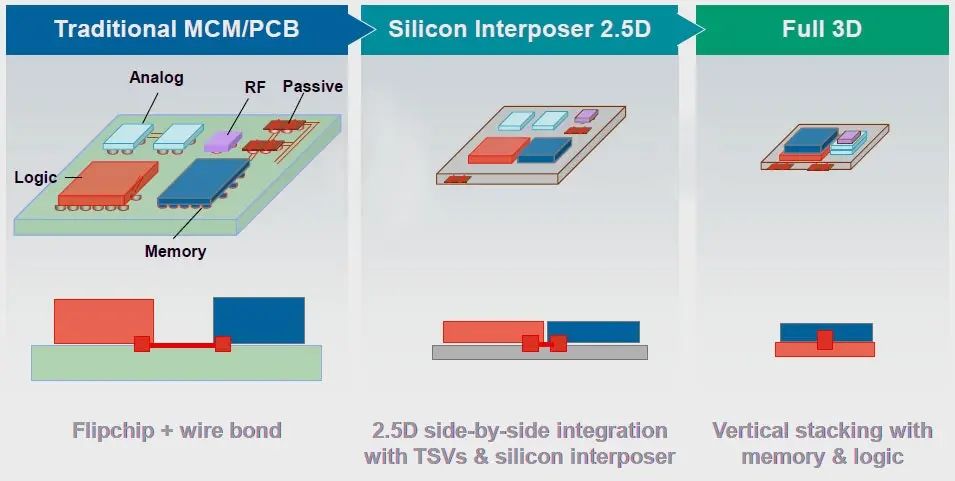

2.5D封裝

2.5D有點像我們上面提到的倒裝芯片的turbo版,但不是將單個裸片堆疊到PCB上,而是將裸片堆疊在單個中介層的頂部。我想這張圖很好地說明了這一點。

2.5D就像有一個地下室的門進入你鄰居的房子,物理上是一個凸點或TSV(通過硅通孔)進入你下面的硅插板,這就把你和你的鄰居連接起來。這并不比你實際的片上通信快,但由于你的凈輸出是由總的封裝性能決定的,降低的距離和增加的兩個硅片之間的互連超過了沒有在一個單一的SOC上的所有缺點。

這樣做的好處是你可以使用 設計好的“小芯片”來快速拼湊更大更復雜的封裝。如果能在一塊硅片上完成就更好了,但這種工藝使制造變得更容易,特別是在較小的尺寸上。

“小芯片”和2.5D封裝可能會使用很長時間,它比3D封裝更容易制造,也便宜得多。此外,它可以很好地擴展,并且可以與新的小芯片一起重復使用,從而通過更換小芯片來制造相同封裝格式的新芯片。AMD的新的Zen3改進就是這樣的,其中封裝相似,但一些小芯片得到了升級。

3D封裝

3D封裝是一個“圣杯”圣杯,是封裝的終極終結。可以這樣比喻,現在,與其在地面上擁有所有1層樓高并由地下室連接的獨立小房子,不如擁有一座巨大的摩天大樓,該摩天大樓是用適合功能所需的任何工藝定制的。這是3D封裝 - 現在所有的封裝都是在硅片本身上完成的。它是驅動更大、更復雜結構的最快、最節能的方法,這些結構是為任務而構建的,并將顯著延長摩爾定律。未來我們可能無法獲得更多的芯片尺寸收縮,但現在有了3D封裝,我們仍然可以在未來改進我們的芯片,類似于以前的摩爾定律。

而有趣的是,我們有一個整個半導體市場走向3D的明顯例子--內存。存儲器向3D結構的推進是對未來發展的一個很好的說明。NAND不得不采用3D結構的部分原因是它們在較小的幾何尺寸上難以擴展。想象一下,內存是一座大型的3D摩天大樓,每一層都由一個電梯連接起來。這些被稱為 "TSV "或通硅孔。

這就是未來的樣子,我們甚至有可能將GPU / CPU芯片堆疊在彼此上或在CPU上堆疊內存。這是最后的邊疆,而現在我們正在迅速接近的邊疆。在接下來的5年里,你可能會開始看到3D封裝一遍又一遍地出現。

2.5D/3D 封裝解決方案快速概述

我認為,與其進一步了解3D和2.5D封裝,不如直接介紹一些正在使用的、你可能已經聽說過的工藝。我想在這里重點談談晶圓廠所做的工藝,這些工藝是推動了3D/2.5D集成發展的。

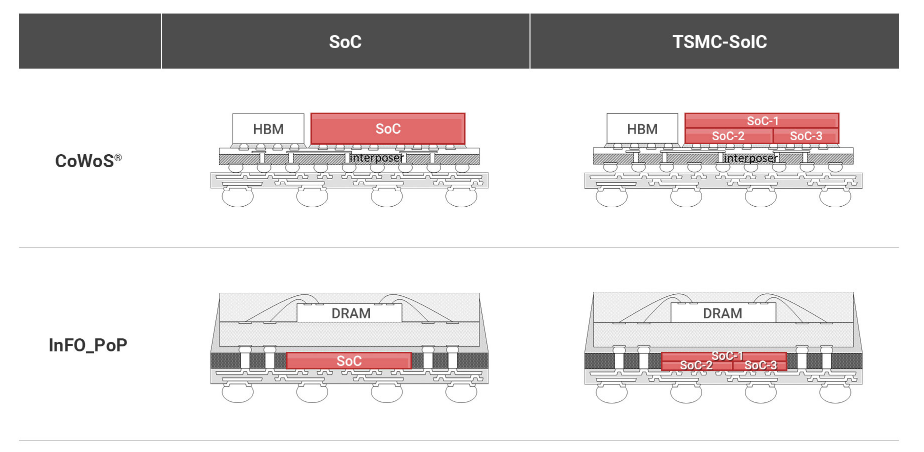

臺積電的CoWoS

這似乎是 2.5D 集成工藝的主力,由 Xilinx 率先推出。

該過程主要集中在將所有邏輯芯片放入硅中介層上,然后放到封裝基板上。一切都通過微凸起或球連接。這是一個經典的2.5D結構。

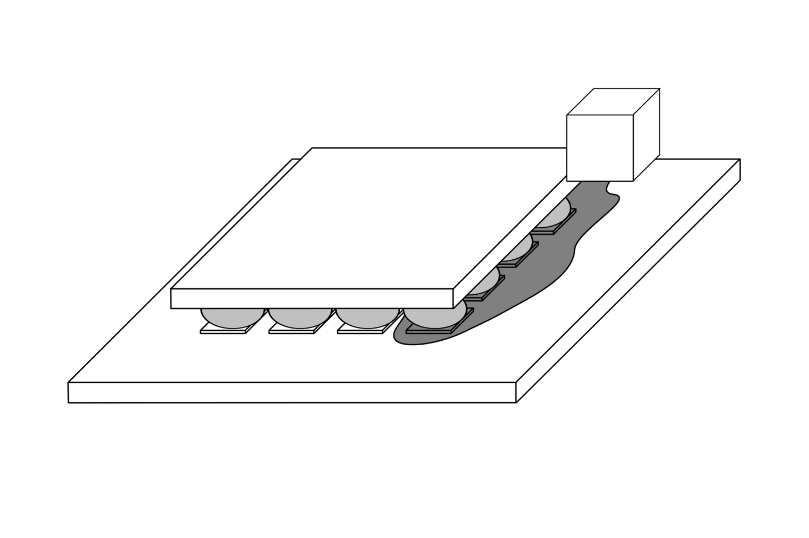

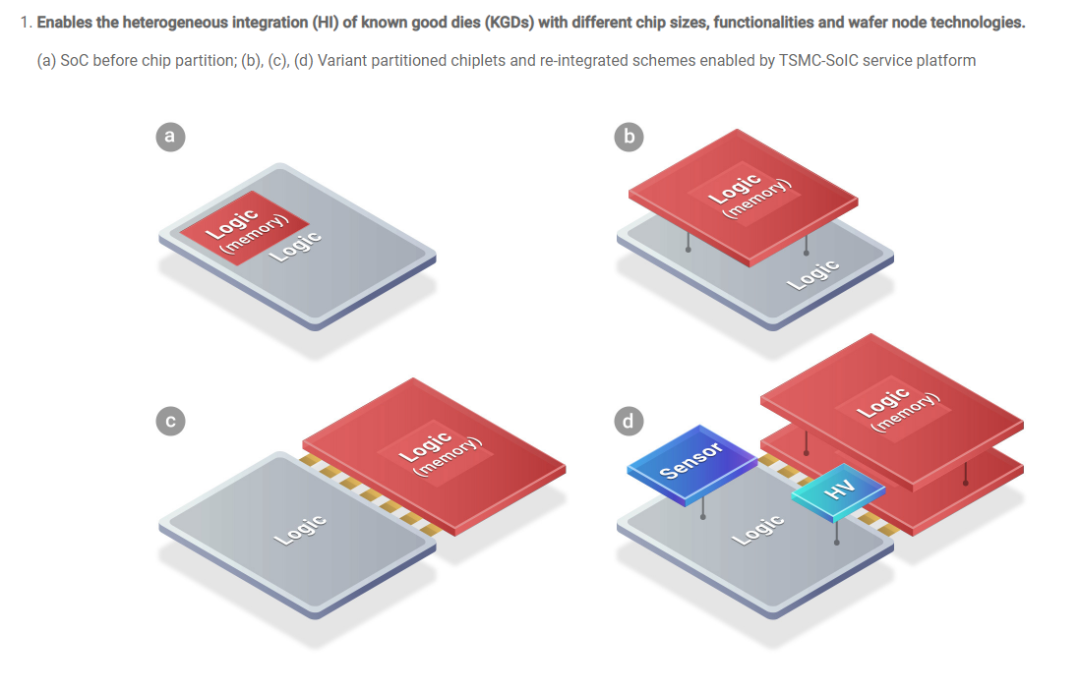

臺積電SOIC

這個臺積電的3D封裝平臺, 是一個相對較新的技術。。

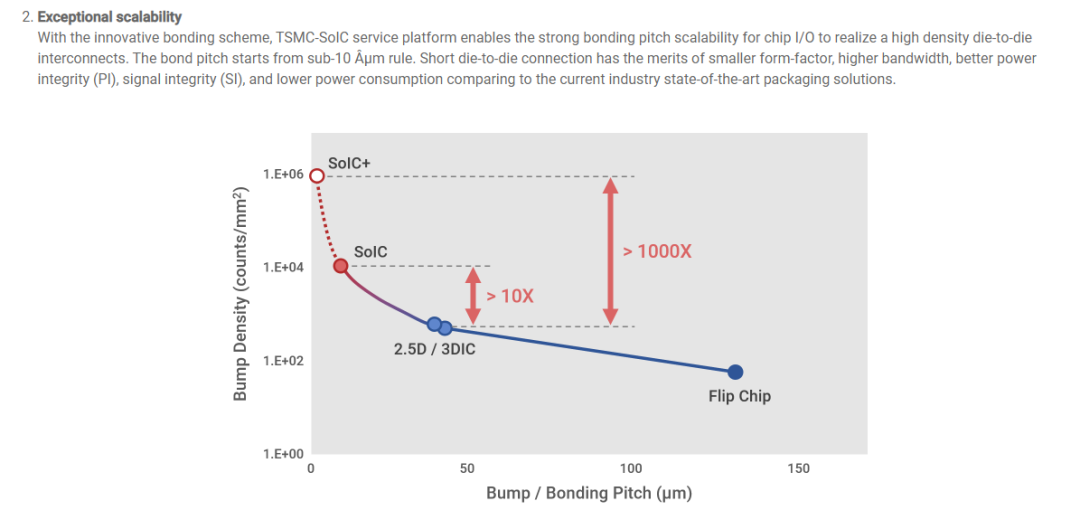

注意這個關于凸點密度和接合間距的驚人圖表,SoIC在尺寸上甚至沒有接近Flipchip或2.5D,而是在密度和特征尺寸方面幾乎是一個前端工藝。

這是對他們技術的一個很好的比較,但請注意,SoIC實際上有一個類似于3D堆疊的芯片堆疊,而不是中階層2.5D集成。

三星 XCube

近年來,三星已成為更重要的代工廠合作伙伴,當然,為了不被超越,三星擁有了新的3D封裝方案。在下面查看他們的XCube的視頻。

這里沒有太多的信息,但我想強調的是,A100是在三星工藝上制造的,所以這可能是為Nvidia最近的芯片提供動力的技術。此外,在這里所有的公司中,三星可能有最豐富的tsv經驗。

英特爾 Foveros

最后是英特爾的Foveros 3D封裝。我們可能會看到英特爾在未來7nm及以后的"混合CPU"工藝中實現更多。他們在架構日已經非常明確地表示,這是他們前進的重點。

有趣的是,在3D封裝過程中,三星,臺積電或英特爾之間并沒有太大的區別。

審核編輯 :李倩

-

芯片

+關注

關注

459文章

52181瀏覽量

436176 -

半導體

+關注

關注

335文章

28609瀏覽量

232575 -

封裝

+關注

關注

128文章

8501瀏覽量

144789

原文標題:芯片封裝簡史

文章出處:【微信號:HXSLH1010101010,微信公眾號:FPGA技術江湖】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

人形機靈巧手求推薦

你家也有“隱形守護者”?Rd-03雷達模組了解一下

初始化AFE4400的時候,哪些控制字是必須最先寫的?

“碰一下”支付背后的4G技術

支付寶發布新一代AI視覺搜索“探一下”

自感線圈斷電時燈泡為啥會閃亮一下

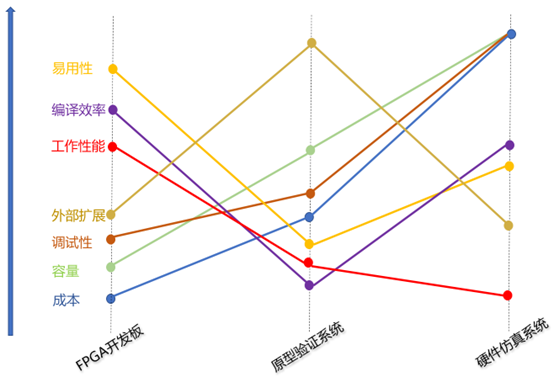

我們需要怎樣的硬件驗證產品

谷景科普大電流共模電感嘯叫對電路運行有影響嗎

飛凌嵌入式-ELFBOARD 從七種芯片封裝類型,看芯片封裝發展史

歡創播報 支付寶“碰一下”正式發布

為什么臺燈亮一下就滅了?

陷波濾波器的相關知識

討論一下封裝的發展簡史

討論一下封裝的發展簡史

評論