中國一站式IP和定制芯片領(lǐng)軍企業(yè)芯動(dòng)科技(INNOSILICON)宣布正式加入U(xiǎn)CIe產(chǎn)業(yè)聯(lián)盟,助力Chiplet標(biāo)準(zhǔn)化,致力于Chiplet創(chuàng)新、迭代和商用。同時(shí),芯動(dòng)自研的首套跨工藝、跨封裝物理層兼容UCIe國際標(biāo)準(zhǔn)Innolink Chiplet解決方案,已在全球范圍內(nèi)率先實(shí)現(xiàn)兼容各種應(yīng)用場景并成功商用落地。

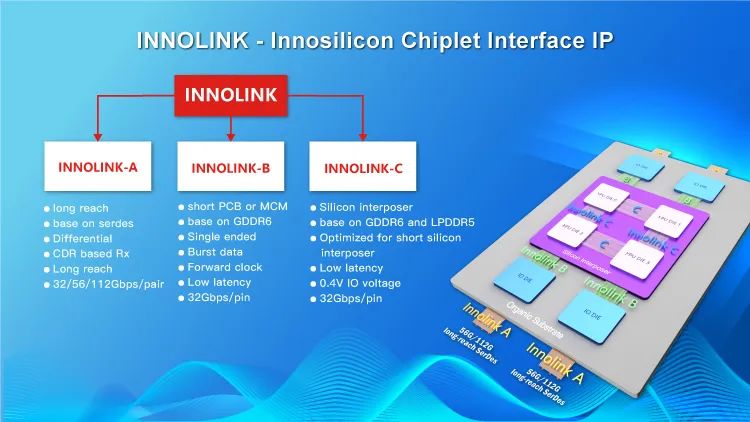

▲Innolink Chiplet A/B/C實(shí)現(xiàn)方法

INNOSILICON

加入U(xiǎn)CIe聯(lián)盟,首發(fā)UCIe Chiplet IP芯動(dòng)科技獨(dú)領(lǐng)風(fēng)騷

Chiplet技術(shù)對當(dāng)前突破AI和CPU/GPU等大型計(jì)算芯片的算力瓶頸具有重要戰(zhàn)略意義,設(shè)計(jì)靈活、成本低、上市周期短,能夠滿足包括云端、邊緣端、企業(yè)級、5G、汽車、高性能計(jì)算和移動(dòng)設(shè)備等在內(nèi)的整個(gè)計(jì)算領(lǐng)域,對算力、內(nèi)存、存儲(chǔ)和互連日益增長的高需求。此前,全球十大行業(yè)巨頭組成了UCIe(Universal Chiplet Interconnect Express)產(chǎn)業(yè)聯(lián)盟,攜手推動(dòng)Chiplet接口規(guī)范的標(biāo)準(zhǔn)化。作為在Chiplet互聯(lián)技術(shù)領(lǐng)域耕耘多年并率先成果產(chǎn)業(yè)化的IP領(lǐng)軍企業(yè),芯動(dòng)科技是國內(nèi)首批加入該聯(lián)盟的廠商之一。芯動(dòng)科技Chiplet架構(gòu)師高專認(rèn)為,“Chiplet聯(lián)盟的成立將形成開放互連的局面,統(tǒng)一標(biāo)準(zhǔn)將實(shí)現(xiàn)更強(qiáng)的賦能。但想要制定標(biāo)準(zhǔn)必須有領(lǐng)先的技術(shù)以及足夠的銷量,國內(nèi)在這方面比較薄弱,加入U(xiǎn)CIe產(chǎn)業(yè)聯(lián)盟是芯動(dòng)致力于推動(dòng)Chiplet商用進(jìn)程、提高國內(nèi)企業(yè)在Chiplet市場聲量的重要一步。”

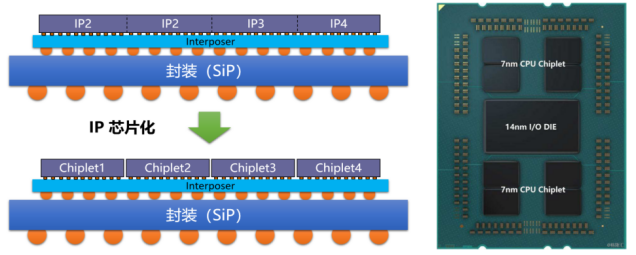

▲多芯粒互聯(lián)的Chiplet技術(shù)是實(shí)現(xiàn)高性能異構(gòu)系統(tǒng)的發(fā)展趨勢

近年來,Chiplet概念開花結(jié)果,AMD、蘋果和英偉達(dá)等國際巨頭都發(fā)布了標(biāo)志性的Chiplet旗艦產(chǎn)品,并在各個(gè)應(yīng)用領(lǐng)域取得極大成功。國內(nèi)上下游企業(yè)也將之視為傳統(tǒng)半導(dǎo)體產(chǎn)業(yè)鏈重構(gòu)的新機(jī)遇,諸多廠商正積極開發(fā)相關(guān)產(chǎn)品,然而商用成果寥寥無幾。芯動(dòng)科技可謂一枝獨(dú)秀。在UCle標(biāo)準(zhǔn)推出后不到三周,芯動(dòng)科技就宣布率先推出國產(chǎn)自主研發(fā)物理層兼容UCIe國際標(biāo)準(zhǔn)的IP解決方案-Innolink Chiplet,這是國內(nèi)首套跨工藝、跨封裝的Chiplet連接解決方案,且已在先進(jìn)工藝上量產(chǎn)驗(yàn)證成功,儼然成為全球Chiplet市場的一顆亮眼新星,也成為芯動(dòng)加入國際UCIe標(biāo)準(zhǔn)制定的敲門磚。INNOSIL

ICONInnolink Chiplet“押中題”

全球率先量產(chǎn)商用

能夠在UCIe標(biāo)準(zhǔn)發(fā)布同一時(shí)間宣布首發(fā)兼容UCIe國際標(biāo)準(zhǔn)的Chiplet解決方案,聽起來像押中高考大題的故事。對此,芯動(dòng)科技Chiplet架構(gòu)師高專表示,“芯動(dòng)在Chiplet技術(shù)領(lǐng)域積累了大量的客戶應(yīng)用需求經(jīng)驗(yàn),并且和臺(tái)積電、intel、三星、美光等業(yè)界領(lǐng)軍企業(yè)有密切的技術(shù)溝通和合作探索,兩年前就開始了Innolink Chiplet的研發(fā)工作,率先明確InnolinkB/C基于DDR的技術(shù)路線,并于2020年的Design Reuse全球會(huì)議上首次向業(yè)界公開Innolink A/B/C技術(shù)。得益于正確的技術(shù)方向和超前的布局規(guī)劃,Innolink 的物理層與UCIe的標(biāo)準(zhǔn)保持一致,成為國內(nèi)始發(fā)、世界先進(jìn)的自主UCIe Chiplet解決方案。”

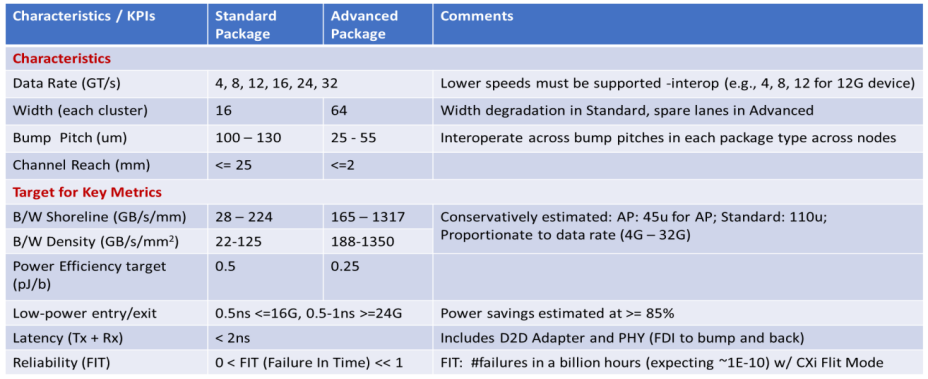

▲UCIe定義不同封裝標(biāo)準(zhǔn)的主要性能指標(biāo)

DDR技術(shù)滿足多芯粒互聯(lián)的高密度、低功耗、低延遲等綜合需求,可使多芯粒像單芯粒一樣工作,單芯粒總線延展至多芯粒。因此,芯動(dòng)在Innolink-B/C 采用了DDR的方式實(shí)現(xiàn),提供基于GDDR6/LPDDR5技術(shù)的高速、高密度、高帶寬連接方案。標(biāo)準(zhǔn)封裝使用MCM傳統(tǒng)基板或短距PCB作為Chiplet互聯(lián)的介質(zhì),具備成本便宜、集成容易等特點(diǎn),是對成本較為敏感的Chiplet應(yīng)用場景首選;先進(jìn)封裝如Silicon Interposer,具備密度高、功耗低、成本高等特點(diǎn),則是對價(jià)格不敏感的高性能應(yīng)用場景首選。在UCIe定義正式發(fā)布前,Innolink-B/C就提前實(shí)現(xiàn)了這兩種封裝場景的應(yīng)用,驗(yàn)證了其對市場前景和Chiplet技術(shù)趨勢的準(zhǔn)確判斷。

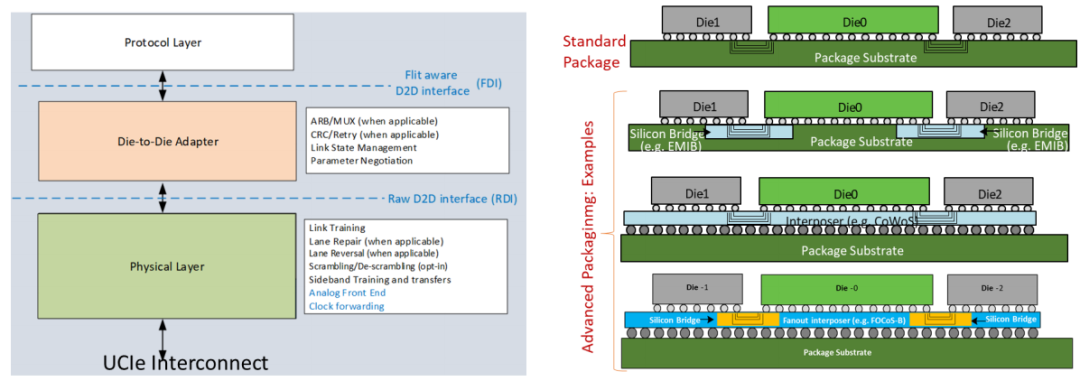

▲ UCIe的Chiplet架構(gòu)分層和先進(jìn)、標(biāo)準(zhǔn)封裝定義

圖中顯示UCIe分了3個(gè)層次,Protocol Layer協(xié)議層、Die to Die Adapter互聯(lián)層、Physical Layer物理層。其中協(xié)議層就是類似常用的PCIE、CXL等上層協(xié)議,底層的Die to Die Adapter和PHY物理層,即是和Innolink Chiplet同樣的實(shí)現(xiàn)方式。

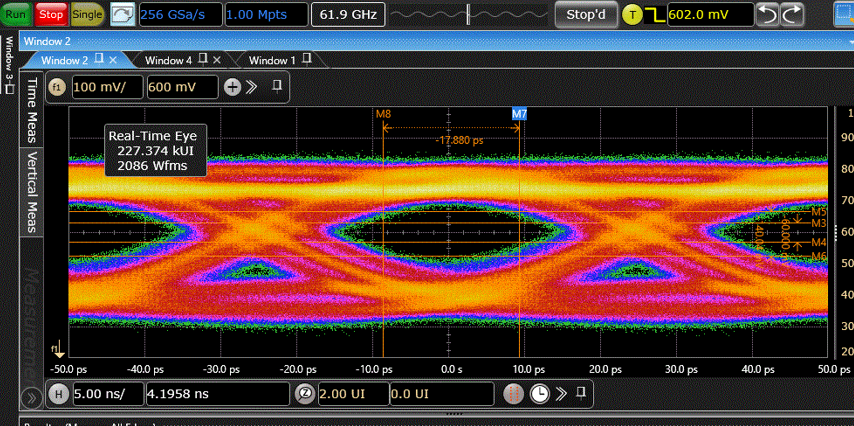

▲ Innolink B在跨13cm長距PCB和封裝下的20Gbps單端信號(hào)實(shí)測眼圖

高專表示,“UCle發(fā)布時(shí)我們就注意到,UCIe規(guī)范中有標(biāo)準(zhǔn)封裝和先進(jìn)封裝兩種規(guī)格,并且這兩種規(guī)格同芯動(dòng)科技的Innolink B/C在思路和技術(shù)架構(gòu)非常類似,都是針對標(biāo)準(zhǔn)封裝和先進(jìn)封裝單獨(dú)定義IO接口,都是單端信號(hào),都是forward clock,都有Data valid信號(hào),都有side band通道。基于Innolink B/C兩年多的研發(fā)和18Gbps/21Gbps的GDDR6/6X研發(fā)量產(chǎn)經(jīng)驗(yàn),芯動(dòng)科技迅速發(fā)布了兼容UCIe兩種規(guī)格的IP產(chǎn)品,可以賦能國內(nèi)外芯片設(shè)計(jì)公司,幫助他們快速推出兼容UCIe標(biāo)準(zhǔn)的Chiplet產(chǎn)品。芯動(dòng)科技的Chiplet解決方案不僅支持標(biāo)準(zhǔn)封裝和先進(jìn)封裝,還可以支持短距PCB場景,而且在多種應(yīng)用場景下,芯動(dòng)的Chiplet方案比傳統(tǒng)的Serdes方案都有延時(shí)、功耗、以及帶寬密度的優(yōu)勢。”圍繞著Innolink Chiplet技術(shù),芯動(dòng)同時(shí)還提供封裝設(shè)計(jì)、可靠性驗(yàn)證、信號(hào)完整性分析、DFT、熱仿真、測試方案等整套解決方案。

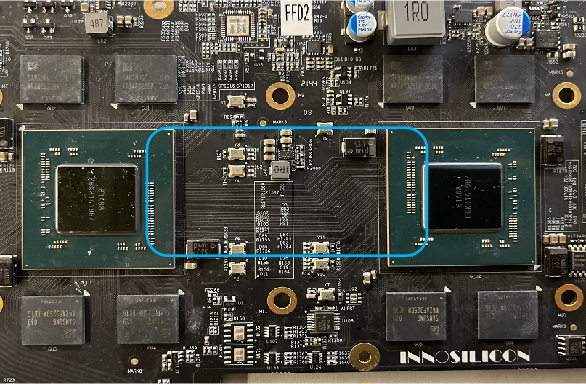

▲Innolink Chiplet廣泛應(yīng)用于高性能計(jì)算芯片量產(chǎn)

目前,Innolink Chiplet方案不僅用在風(fēng)華1號(hào)數(shù)據(jù)中心GPU上,實(shí)現(xiàn)了性能翻倍,還被授權(quán)給了眾多合作伙伴和客戶。通過復(fù)用芯動(dòng)科技的國產(chǎn)Innolink Chiplet技術(shù),芯片設(shè)計(jì)企業(yè)和系統(tǒng)廠商能夠快速便捷地實(shí)現(xiàn)多Die、多芯片之間的互連,有效簡化了設(shè)計(jì)流程。

INNOSILICON十六年厚積薄發(fā)領(lǐng)跑Chiplet水到渠成 凡事預(yù)則立,不預(yù)則廢。

“押中題”往往不是運(yùn)氣眷顧,而是“功夫不負(fù)有心人”的成竹在胸。能夠準(zhǔn)確地把握Chiplet技術(shù)方向,前瞻性地完成設(shè)計(jì)驗(yàn)證,與后來推出的UCIe技術(shù)方向一致,無疑是芯動(dòng)技術(shù)團(tuán)隊(duì)長期投入和耕耘的成果,離不開芯動(dòng)在高速接口領(lǐng)域的深厚積累和授權(quán)量產(chǎn)經(jīng)驗(yàn)的持續(xù)領(lǐng)先。Innolink背后的技術(shù)極為復(fù)雜,正因?yàn)樾緞?dòng)掌握了GDDR6/6X、LPDDR5/5X、DDR5/4、HBM3/HBM2E、32G/56G SerDes、基板和Interposer設(shè)計(jì)方案、高速信號(hào)完整性分析、先進(jìn)工藝封裝、測試方法等等世界前沿的核心技術(shù),并且經(jīng)過大量客戶需求落地和量產(chǎn)驗(yàn)證迭代,累計(jì)流片200次以上的驗(yàn)證經(jīng)驗(yàn),高端IP出貨超60億顆的量產(chǎn)應(yīng)用。尤其在DDR系列高帶寬技術(shù)上,芯動(dòng)科技堪稱業(yè)界天花板,不久前發(fā)布以先進(jìn)FinFet工藝量產(chǎn)了全球最快的LPDDR5/5X/DDR5 IP一站式解決方案,首次在普通PCB長距離上實(shí)現(xiàn)內(nèi)存顆粒過10Gbps的訪問速率。對創(chuàng)新的不斷追求和底層技術(shù)的長期積淀,鑄就了芯動(dòng)在高性能領(lǐng)域的洞察力和核心競爭力。

▲Innolink Chiplet內(nèi)部實(shí)現(xiàn)的基礎(chǔ)技術(shù)盤點(diǎn)

芯動(dòng)的先進(jìn)IP技術(shù),一方面引領(lǐng)行業(yè)技術(shù)的創(chuàng)新,塑造半導(dǎo)體企業(yè)的全球化長遠(yuǎn)發(fā)展視野,另一方面填補(bǔ)高性能芯片的應(yīng)用空白,助力國內(nèi)高端芯片發(fā)展。這也是芯動(dòng)科技能先人一步實(shí)現(xiàn)Chiplet商用落地、躋身UCIe國際聯(lián)盟之列的根源。

審核編輯:湯梓紅

-

芯動(dòng)科技

+關(guān)注

關(guān)注

2文章

96瀏覽量

10124 -

chiplet

+關(guān)注

關(guān)注

6文章

449瀏覽量

12840 -

UCIe

+關(guān)注

關(guān)注

0文章

49瀏覽量

1785

原文標(biāo)題:芯動(dòng)加入U(xiǎn)CIe聯(lián)盟助力標(biāo)準(zhǔn)化,首發(fā)國產(chǎn)兼容UCIe的Chiplet IP

文章出處:【微信號(hào):Innosilicon,微信公眾號(hào):芯動(dòng)科技Innosilicon】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

MEMS測試設(shè)備標(biāo)準(zhǔn)化:降本增效必經(jīng)之路

高鴻信安加入全國數(shù)據(jù)標(biāo)準(zhǔn)化技術(shù)委員會(huì)

井芯微電子受邀參加2024年汽車芯片標(biāo)準(zhǔn)會(huì)議

芯海科技加入星閃聯(lián)盟 共探新一代無線短距通信未來應(yīng)用

芯海科技引領(lǐng)智能化浪潮:標(biāo)準(zhǔn)化單鍵壓力按鍵解決方案賦能終端創(chuàng)新

CAN技術(shù)的標(biāo)準(zhǔn)化之旅

最新Chiplet互聯(lián)案例解析 UCIe 2.0最新標(biāo)準(zhǔn)解讀

英瑞沃加入中國運(yùn)動(dòng)控制產(chǎn)業(yè)聯(lián)盟

IMEC組建汽車Chiplet聯(lián)盟

博世攜手Tenstorrent共研汽車芯片標(biāo)準(zhǔn)化方案

加速國際標(biāo)準(zhǔn)制定與推廣,RDSA產(chǎn)業(yè)聯(lián)盟跑步入場

國產(chǎn)半導(dǎo)體新希望:Chiplet技術(shù)助力“彎道超車”!

消息稱三菱汽車將加入本田-日產(chǎn)聯(lián)盟

“芯”動(dòng)余杭:地芯科技引領(lǐng)產(chǎn)業(yè)新篇

芯動(dòng)科技加入U(xiǎn)CIe產(chǎn)業(yè)聯(lián)盟 助力Chiplet標(biāo)準(zhǔn)化

芯動(dòng)科技加入U(xiǎn)CIe產(chǎn)業(yè)聯(lián)盟 助力Chiplet標(biāo)準(zhǔn)化

評論