在第 2 部分中,我們將介紹如何在軟件中實現高精度 NCO。構建具有與最佳模擬振蕩器相似或更好的失真性能的高精度交流音調發生器。

在本系列的第 1 部分中,我們將了解如何基于直接數字頻率合成 (DDFS) 原理設計一個非常精確的正弦波發生器,但在浮點 DSP 處理器上以軟件實現。在第 2 部分中,我們將介紹如何在軟件中實現高精度 NCO。

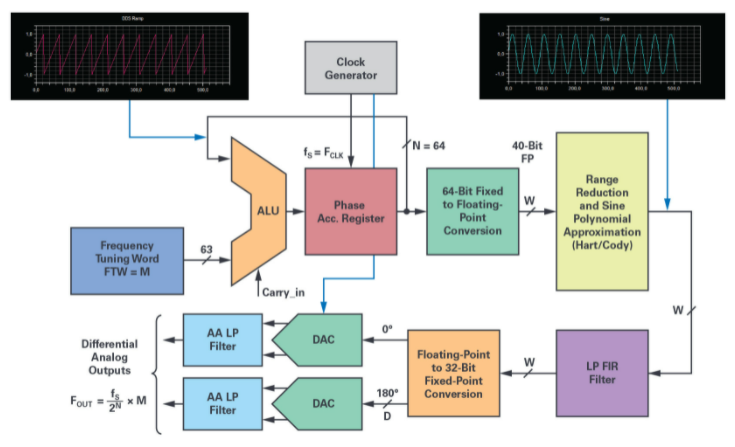

構建一個具有與最好的模擬振蕩器相似或更好的失真性能的高精度交流音發生器,如最著名的惠普分析儀或應用筆記 AN-1323 中所述,即使專用于音頻,也不是一件容易的事頻譜(直流至 20 kHz 范圍)。然而,如前所述,完整的軟件實現,使用嵌入式處理器的足夠算術精度執行相位計算 (ωt) 和正弦函數 (sin(ωt)) 近似,當然可以幫助最大限度地減少量化副作用、噪聲、以及由此產生的馬刺。這意味著圖 2 中的所有 NCO 功能塊都轉換為代碼行(沒有 VHDL!

對于相位到正弦幅度轉換引擎,完整的 LUT 方案或任何變化都需要過多的內存或過多的插值操作才能實現完美的正弦一致性。相反,用于正弦逼近的多項式方法通過允許使用成本非常低的通用 DSP,提供了非常好的復雜性與精度之間的折衷。多項式級數展開也非常有吸引力,因為它相對簡單,并且能夠在選擇冪級數類型時提供充分的靈活性,并為給定的精度定制算法。它不需要大的存儲空間、少于 100 行 SHARC DSP 裝配線,并且只需要幾個 RAM 位置來存儲多項式系數和變量,因為正弦值僅在采樣時刻計算。

首先,正弦逼近函數的明顯選擇是使用具有適當階數的直線 Taylor/MacLaurin 冪級數來滿足目標精度。然而,由于冪級數往往在端點處失效,因此在執行任何多項式評估之前,必須將參數輸入范圍縮小到更小的區間。在沒有參數范圍縮減的情況下,只有非常高階的多項式才能支持函數域上的高精度,例如 [–π, +π]。因此,需要對初等函數應用一些變換以得到簡化參數,例如 sin(|x|) = sin(f + k × π/2) 和 sin(f) = sin(x – k × π/ 2) 0≤f《π/2。因此,應特別注意三角函數以避免減法抵消,這將導致嚴重的精度損失并產生災難性的結果,尤其是在算術精度較差的情況下。在我們的例子中,當相位輸入較大或接近 π/2 的整數倍時,可能會發生這種情況。

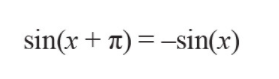

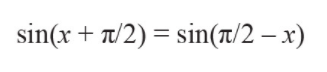

除了周期性和模 2π 重復之外,sin(x) 函數的對稱特性還可用于進一步減小逼近范圍。鑒于正弦函數在區間 [0, 2π] 中關于點 x = π 反對稱,因此可以使用以下關系:

將范圍縮小到 [0, π]。以同樣的方式,sin(x) 顯示了關于區間 [0, π] 中由 x = π/2 定義的線的對稱性,使得:

對于區間 [0, π/2] 中的 x,這進一步減小了角度輸入逼近范圍。進一步將參數減少到更小的區間(例如 [0, π/4] 以提高準確性)效率不高,因為它需要同時評估正弦和余弦函數,如常見的三角關系所示:sin(a+b ) = sin(a) × cos(b) + cos(a) × sin(b),值得產生正交音。

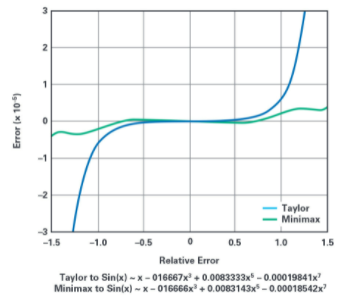

ADI 公司的 ADSP-21000 系列應用手冊第 1 卷描述了一種幾乎理想的(用于嵌入式系統)正弦逼近函數,該函數基于為第一個 ADI DSP 浮點處理器(即 ADSP-21020)編寫的優化冪級數,它基本上是一個SHARC核心。sin(x) 的這種實現依賴于 Hart 等人 4 發表并由 Cody 和 Waite5 改進的極小極大多項式近似,用于浮點運算,以減少舍入誤差并避免如前所述的取消的發生。minimax 方法依賴于 Chebyshev 多項式和 Remez 交換算法來確定所需最大相對誤差的系數。如圖 3 中的 MATLAB 所示,

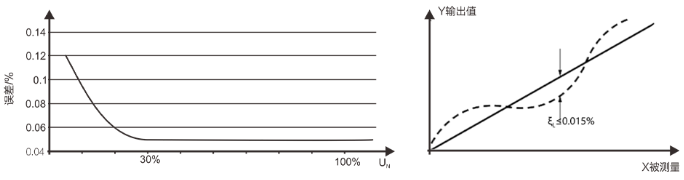

圖 3. 與定義在 0 附近的 Taylor-MacLaurin 方法不同,極小極大正弦近似方法在 [–π/2 到 +π/2] 區間內最小化和均衡最大相對誤差。

雖然所有計算都可以使用 32 位定點算術執行,但多年來,最常見和最方便的數學計算格式一直是 IEEE 754 浮點標準,尤其是在處理長數時。當時根本沒有單片浮點DSP處理器,只有ADSP-3212和ADSP-3222等簡單的浮點乘法器和ALU計算IC。這種格式取代了計算機行業的大多數專有格式,并成為所有 SHARC DSP 處理器的原生格式,包括單精度 32 位、擴展精度 40 位以及最近用于 ADSP-SC589 的雙精度 64 位和 ADSP-SC573。

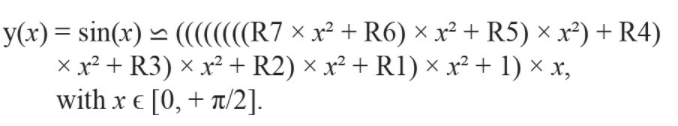

SHARC 40 位擴展單精度浮點格式及其 32 位尾數為該正弦波生成應用提供了足夠的精度 (u 2–32) 并保持相等,Cody 和 Waite 表明 15 階多項式是合適的對于 32 位的整體精度,在 [0 到 +π/2] 輸入域上具有均勻分布的誤差。最小化運算次數并保持準確性的最后調整是實現多項式計算的霍納規則,這是一種在一個點上計算多項式的快速取冪方法,例如:

R1 到 R7 是多項式級數的 Cody 和 Waite 系數,只需 8 次乘法和 7 次加法即可計算任何輸入參數 ε[0, π/2] 的正弦函數。以匯編子程序形式編寫的完整 sin(x) 近似代碼在 SHARC 處理器上大約需要 22 個內核周期執行。原始匯編子程序被修改為在獲取 40 位多項式浮點系數時同時執行雙內存訪問,以節省六個周期。

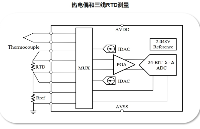

圖 4. 軟件 DDS 簡化框圖給出了數據算術格式和處理元件之間各種量化步驟的位置。

NCO 64 位相位累加器本身使用雙精度二進制補碼小數格式的 SHARC 32 位 ALU 來執行。具有內存更新的完整相位累加器執行需要 11 個內核周期,因此,每個 NCO 輸出樣本在大約 33 個內核周期內生成。

圖 4 中的圖表顯示了基于軟件 DSP 的 NCO 的功能塊實現,其中參考了每個階段的算術格式精度。此外,信號模擬重構還需要一個或兩個 DAC 及其模擬抗混疊濾波器電路,以實現完整的 DDFS。處理鏈的關鍵要素是:

64位相位累加器(SHARC ALU雙精度加法溢出);

64 位小數定點到 40 位 FP 轉換塊;

范圍縮減塊 [0 到 + π/2] 和象限選擇(Cody 和 Waite);

用于相位幅度轉換的正弦逼近算法 (Hart);

–1.0 到 +1.0 范圍內的 sin(x) 重建和歸一化階段;

必要時進行 LP FIR 濾波器和 sin(x)/x 補償;

以及 40 位 FP 到 D 位定點轉換和縮放功能,以適應 DAC 數字輸入。

可以在 NCO 的輸出端放置一個可選的數字低通濾波器,以消除可能折疊在感興趣頻帶中的任何雜散和噪聲。可選地,該濾波器可以根據為模擬重建選擇的 DAC 提供插值和/或逆 sin(x)/x 頻率響應補償。這種低通 FIR 濾波器可以使用 MATLAB 濾波器設計器工具來設計。例如,假設采樣頻率為 48 kSPS,直流至 20 kHz 帶寬,帶內紋波為 0.0001 dB,帶外衰減為 –150 dB,則可以使用 40 位浮點實現高質量等紋波濾波器系數。只有 99 個濾波器系數,它的總執行時間將在單指令、單數據 (SISD) 單計算單元模式下消耗大約 120 個 SHARC 內核周期。數字濾波后,DMA 使用其中一個 DSP 同步串行端口將計算的樣本對發送到 DAC。為了獲得更好的速度性能,鏈接 DMA 操作也可以與大型乒乓存儲器緩沖區一起支持按塊操作進行處理。例如,塊數據大小可以等于 FIR 數據延遲線的長度。

NCO 的最終調整以獲得最佳 SFDR

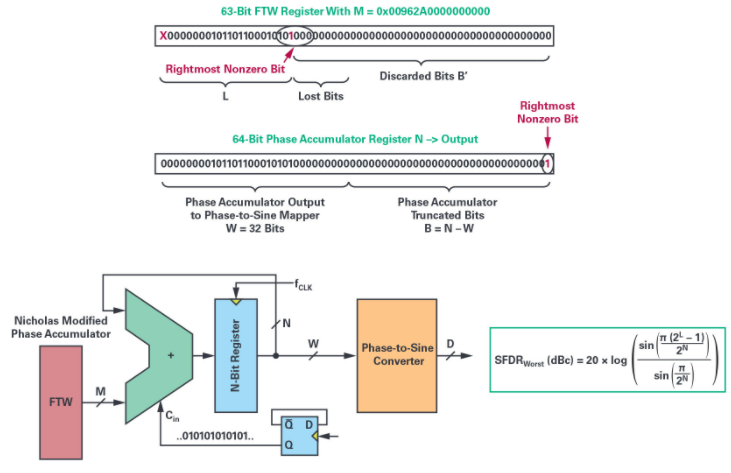

如前所述,NCO 受到雜散的影響主要是由于相位累加器輸出的截斷,并且在較小程度上是由于對通過計算或制表獲得的正弦值進行的幅度量化造成的。相位截斷導致的誤差通過相位調制(鋸齒波)在載波頻率附近產生雜散,而正弦幅度量化導致諧波相關的雜散,盡管長期以來被認為是隨機誤差和噪聲。今天,如 Henry T. Nicholas 和 H. Samueli 的技術論文 7 中所描述的,相位累加器的操作在數學上是眾所周知的。經過全面分析,提出了一個模型,將相位累加器視為離散相位樣本置換發生器,從中可以預測頻率雜散。

(其中 GCD 是最大公約數)由頻率調諧字 M 的最右邊位位置 L 確定,如圖 4 所示。因此,L 的值定義了序列類別,每個類別共享自己的一組相位組件,但根據排列

比率。在時域中生成的這些截斷相位樣本序列用于通過 DFT 確定頻域中每個雜散線的相應位置和幅度。這些序列還表明 M (FTW) 的奇數值表現出最低頻率雜散的幅度,并建議對相位累加器進行簡單修改,以滿足這些最小條件,只需將 1 LSB 添加到 FTW。這樣,無論 M 值和相位累加器的初始內容如何,相位累加器輸出序列都被迫始終具有相同的 2N 個相位元素。然后,最差雜散音幅度的電平降低 3.922 dB,等于 SFDR_min (dBc) = 6.02 × W。 Nicholas 改進的相位累加器為 NCO 帶來了幾個好處,

圖 5. FTW 最右邊的非零位的位置設置了理論上的 SFDR 最壞情況水平。Nicholas 改進的相位累加器解決了任何 N 值的問題,并使 NCO 的 SFDR 最大化。

因此,對于 32 位的輸出相位字 W,由于相位截斷而導致的最大雜散幅度被限制為 –192 dBc!正弦樣本值的有限量化也會導致另一組頻率雜散,通常將其視為噪聲,并通過眾所周知的關系 SNRq(dB) = 6.02 × D + 1.76 進行估計。由于相位到正弦幅度轉換算法階段的近似誤差,這必須添加到寄生元素中,但是,考慮到在選擇相位到正弦近似算法和計算的精度。

這些結果表明,我們的軟件正弦 NCO 的線性度和噪聲都處于理論水平,遠遠超出了測試市場上大多數高精度 ADC 所需的閾值。仍然需要找到信號鏈中最后但最關鍵的元素:重建 DAC 及其互補模擬抗混疊濾波器和相關的驅動器電路,可以滿足預期的性能水平。

在本系列的第 3 部分中,我們將介紹如何選擇重構 DAC 并完成 DDFS 系統。

審核編輯:郭婷

-

濾波器

+關注

關注

162文章

8066瀏覽量

181000 -

adc

+關注

關注

99文章

6635瀏覽量

548233 -

dac

+關注

關注

43文章

2379瀏覽量

193014

發布評論請先 登錄

方案分享 | 高精度時間同步技術的實現與應用

如何實現高精度、高可靠性的隔離式電流/電壓測量?如何在緊湊布局中平衡性能與成本?如何應對EMI干擾與安

UWB高精度定位技術在智能倉儲中的應用

請問ADS1263能做到多高精度?實現高精度應該注意什么?

音頻信號采集為什么要用專用的CODEC來實現,普通高精度高采樣率ADC可以嗎?

數字振蕩器的實現要求有哪些

VS高精度電壓傳感器

探索UWB技術的獨特優勢:實現高精度定位

什么是高精度定位平板?

北斗高精度定位手持終端在哪些場景中應用

如何在軟件中實現高精度NCO

如何在軟件中實現高精度NCO

評論