IEEE 1149.1 標(biāo)準(zhǔn)于 1990 年被采用。基于聯(lián)合測試行動小組 (JTAG) 的工作,它提供了從一個(gè) IC 焊盤到另一個(gè) IC 焊盤的引腳視圖,以幫助測試工程師定位和發(fā)現(xiàn)有故障的 PC 板。1994 年增加了邊界掃描描述語言的描述。

隨著芯片功能的增加和設(shè)計(jì)從 PC 板轉(zhuǎn)向多芯片模塊和堆疊芯片封裝,復(fù)雜性出現(xiàn)了。這些困難包括處理片上系統(tǒng) (SoC) 設(shè)備的引腳數(shù)要求和多個(gè)測試訪問端口 (TAP) 控制器、測試多芯片模塊和堆疊芯片配置、提高調(diào)試性能以及改進(jìn)測試和調(diào)試邏輯斷電低功率條件。

移動行業(yè)處理器接口聯(lián)盟和 NEXUS 5001 論壇等組織接受了挑戰(zhàn),以解決其行業(yè)特有的問題。他們的工作為 IEEE 1149.7 標(biāo)準(zhǔn)奠定了基礎(chǔ),該標(biāo)準(zhǔn)有望在明年初獲得批準(zhǔn)。

增加測試系統(tǒng)功能

新的 IEEE 1149.7 標(biāo)準(zhǔn)并沒有取代 IEEE 1149.1,而是通過減少使用的引腳數(shù)量來擴(kuò)展其功能。這提供了有利于堆疊裸片和多芯片模塊配置的新掃描拓?fù)洌⑻峁└呒壒δ芤詭椭M(jìn)行軟件調(diào)試。

IEEE 1149.7 目標(biāo)

與現(xiàn)有的 IEEE 1149.1 系統(tǒng)兼容

使用更少的引腳操作

使用相同的引腳提供后臺儀表功能

提供 TAP 電源管理機(jī)制

用于調(diào)試半導(dǎo)體錯(cuò)誤/缺陷的保留網(wǎng)關(guān)

提高選定調(diào)試用例的性能

保留對半導(dǎo)體 IP、軟件 IP 以及現(xiàn)有調(diào)試和測試工具的投資

為其他調(diào)試引腳協(xié)議提供框架以訪問引腳

IEEE 1149.7 標(biāo)準(zhǔn)具有兩組功能:T0 到 T3 類,擴(kuò)展 IEEE 1149.1 并啟用新操作,以及 T4 和 T5 類,專注于高級雙引腳操作。

T0 級

T0 類通過設(shè)置 IEEE 1149.7 設(shè)備以使其與 IEEE 1149.1 兼容,從而確保符合行業(yè)測試基礎(chǔ)設(shè)施。這些技術(shù)包括使用 N 位 IR、1 位 DR 用于旁路指令、強(qiáng)制性 IDCODE(32 位路徑)和行為如 IEEE 1149.1 規(guī)范中指定的強(qiáng)制性指令。啟動測試邏輯復(fù)位后,所有多 TAP 設(shè)備必須符合強(qiáng)制性 IEEE 1149.1 指令行為,并對旁路指令執(zhí)行 1 位 DR 掃描。

T1 級

T1 類實(shí)例化了一個(gè)對 IEEE 1149.1 設(shè)備透明的 IEEE 1149.7 標(biāo)準(zhǔn)的控制系統(tǒng),為在 T1 到 T5 類中實(shí)現(xiàn)的高級功能提供了基礎(chǔ),而無需更改 IEEE 1149.1 狀態(tài)機(jī)。除了創(chuàng)建控制系統(tǒng)外,該課程還解決了具有四種斷電模式的功率敏感設(shè)備的需求。

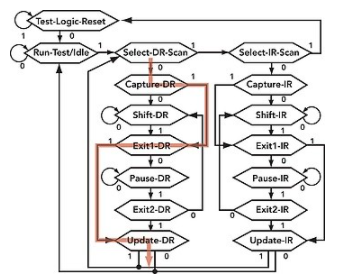

關(guān)鍵創(chuàng)新是 IEEE 1149.1 兼容的 TAP 狀態(tài)序列和移位狀態(tài)監(jiān)視的組合,它創(chuàng)建了一個(gè) IEEE 1149.7 控制系統(tǒng),該系統(tǒng)利用旁路或 IDCODE 指令以及一系列稱為零位 DR 掃描的 IEEE 1149.1 兼容序列( ZBS),如圖 1 所示。

圖1

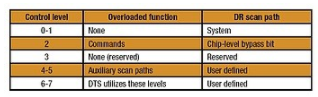

從零開始,ZBS 計(jì)數(shù)隨著 ZBS 的每次連續(xù)出現(xiàn)而遞增,而不會遇到 Shift-DR TAP 控制器 (TAPC) 狀態(tài)。當(dāng)包含 Shift-DR 的 DR 掃描發(fā)生并且 ZBS 計(jì)數(shù)大于零時(shí),ZBS 計(jì)數(shù)被鎖定,激活相應(yīng)的控制級別(如表 1 所示)。

表格1

命令通常是 10 位值,由兩個(gè)連續(xù)的 DR 掃描組成,同時(shí)控制器鎖定在控制級別 2。命令部分 1 (CP1) 提供 5 位操作碼,命令部分 2 (CP2) 提供立即操作數(shù),這是命令的低 5 位。該命令指定的功能在 CP2 完成時(shí)執(zhí)行。

可以通過在 CP1 和 CP2 之后附加第三個(gè) DR 掃描(控制寄存器或 CR 掃描)并傳輸數(shù)據(jù)值來創(chuàng)建三部分命令。這三個(gè)三部分命令中的每一個(gè)都有一個(gè)特殊的用途。

T2 級

為了讓參與測試高芯片數(shù)應(yīng)用的工程師獲得更高的性能,T2 類提供了一種縮短掃描鏈的芯片級旁路機(jī)制和另一種提供熱連接能力的機(jī)制。T2 類添加了三種掃描格式來實(shí)現(xiàn)這些新功能:

JSCAN0:提供符合 IEEE 1149.1 的操作。

JSCAN1:提供熱連接和斷開保護(hù)。上電時(shí),旁路可以是默認(rèn)設(shè)置(JSCAN1 格式)。這可以保護(hù) TAP 免受虛假信號的影響,并防止熱連接期間的內(nèi)核損壞。

JSCAN2:實(shí)施旁路以提高串聯(lián)設(shè)備的性能。該機(jī)制還起到防火墻的作用,只有在啟動預(yù)定序列后才能訪問芯片 TAP。這種安全措施確保一旦運(yùn)行的通電目標(biāo)具有穩(wěn)定的電氣連接,只有調(diào)試測試控制器才能訪問系統(tǒng)。

T3 級

雖然包括使用星形拓?fù)溥M(jìn)行邊界掃描測試的規(guī)定,但 IEEE 1149.1 并未提供足夠的細(xì)節(jié)來使這種測試模式可行。IEEE 1149.7 中包含了一種新的掃描格式“?ì JSCAN3”,以糾正這一遺漏。用于指定掃描格式的只寫寄存器和星型配置的設(shè)備地址分配也已添加到新標(biāo)準(zhǔn)中。

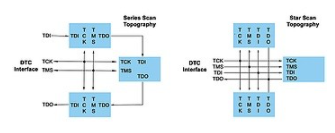

IEEE 1149.7 支持串聯(lián)和星型拓?fù)洌笳吒m合測試堆疊芯片配置。由于調(diào)試連接的位置是一致的,因此星型拓?fù)鋵τ诙询B管芯配置是可取的。圖 2a 顯示了串聯(lián)掃描拓?fù)洌瑘D 2b 顯示了 Star-4 或 Wide Star 配置。

圖 2

IEEE 1149.7 通過在一組選定的支持 IEEE 1149.7 的 TAP 控制器中使用 Capture-xR 和 Update-zR TAPC 狀態(tài)使所有操作看起來是系列掃描,從而保持與 IEEE 1149.1 標(biāo)準(zhǔn)的兼容性。要在這種模式下運(yùn)行,必須為星型配置的芯片分配控制器標(biāo)識 (CID) 編號。使用迭代仲裁系統(tǒng)分配 CID,并使用控制級別 2 執(zhí)行操作。

T4 級

為了解決 SoC 器件中引腳數(shù)量不斷增加的問題,T4 類增加了掃描格式以支持使用兩個(gè)引腳而不是四個(gè)引腳的事務(wù),從而減少了芯片封裝所需的總引腳數(shù)。這也有助于堆疊裸片配置,因?yàn)榉浅OM诙询B裸片時(shí)具有盡可能少的連接器數(shù)量。

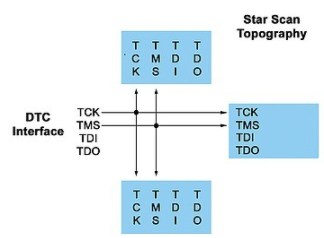

雙引腳操作的關(guān)鍵是消除原始數(shù)據(jù)線并通過測試模式選擇 (TMS) 線發(fā)送雙向串行數(shù)據(jù),該線更名為 TMS 計(jì)數(shù)器 (TMSC)。為實(shí)現(xiàn)此功能,使用了 T3 類的無縫星形配置,這次沒有測試數(shù)據(jù)輸入 (TDI) 和測試數(shù)據(jù)輸出 (TDO)。這是圖 3 中所示的 Star-2 配置。

圖 3

除了減少引腳數(shù)之外,T4 類還定義了優(yōu)化的下載特定掃描模式,其中只下載有用的信息。為了提高引腳操作性能,時(shí)鐘頻率也可以加倍。這些功能與優(yōu)化的事務(wù)相結(jié)合不會導(dǎo)致性能損失,而是在某些情況下提高了性能。

T5 級

T5 類功能主要有利于利用 JTAG 進(jìn)行調(diào)試的軟件設(shè)計(jì)人員。此類使測試端口能夠同時(shí)執(zhí)行調(diào)試和儀表操作(數(shù)據(jù)在空閑時(shí)間傳輸),這減少了專用于儀表的引腳數(shù)量,并使自定義協(xié)議能夠使用引腳,這是許多供應(yīng)商在非標(biāo)準(zhǔn)中提供的功能方法。T5 類標(biāo)準(zhǔn)化了訪問引腳的過程。

審核編輯:郭婷

-

處理器

+關(guān)注

關(guān)注

68文章

19813瀏覽量

233615 -

芯片

+關(guān)注

關(guān)注

459文章

52205瀏覽量

436456 -

JTAG

+關(guān)注

關(guān)注

6文章

403瀏覽量

72942

發(fā)布評論請先 登錄

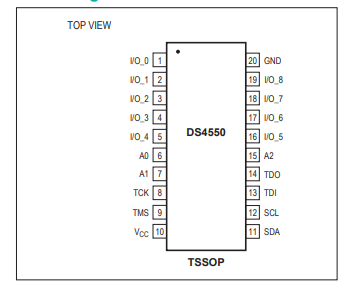

DS4550 I2C和JTAG、非易失、9位、輸入/輸出擴(kuò)展器與存儲器技術(shù)手冊

FPGA的Jtag接口燒了,怎么辦?

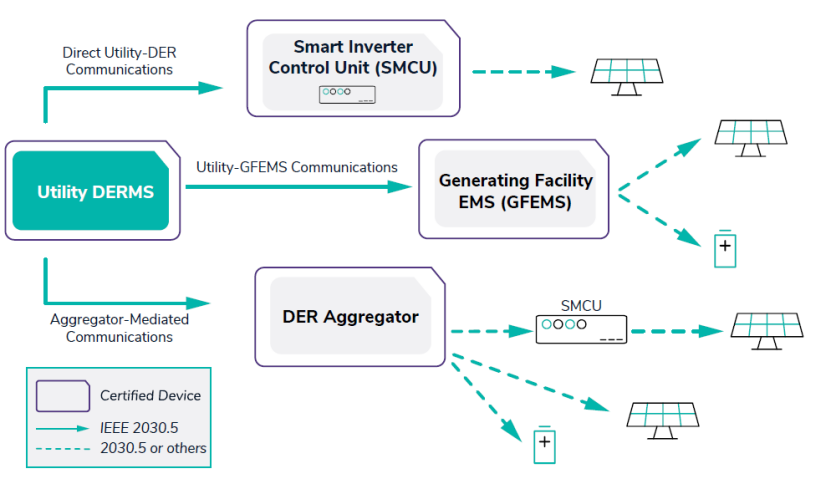

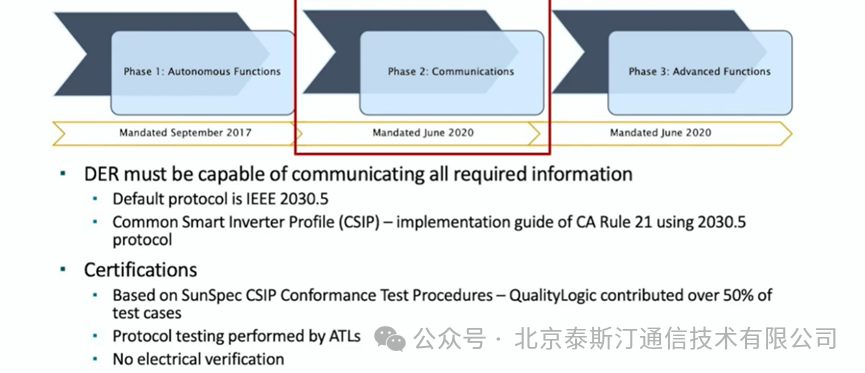

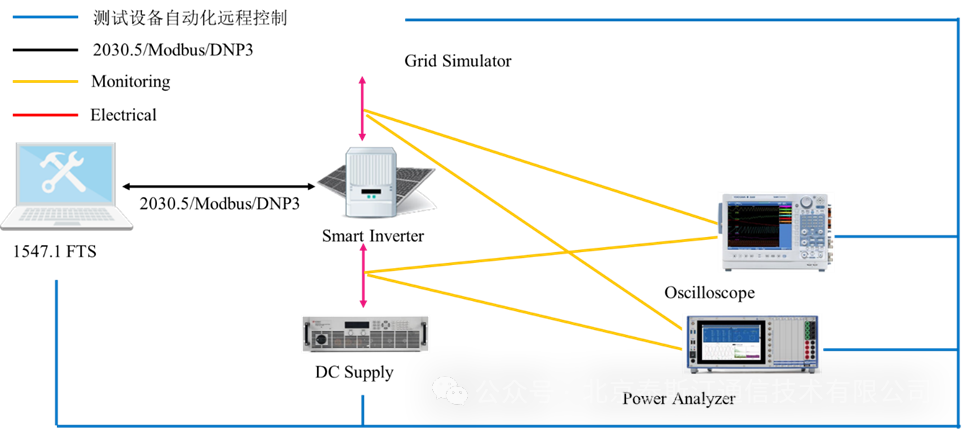

IEEE 2030.5協(xié)議演進(jìn)、應(yīng)用、培訓(xùn)

EE-68: JTAG仿真技術(shù)參考

JTAG/MPSD仿真技術(shù)參考

IEEE2030.5概要

IEEE 1547 發(fā)展背景

JTAG的基礎(chǔ)知識

通過JTAG接口對MSP430進(jìn)行編程

C2000 MCU JTAG 連接調(diào)試

SPI、UART、RGMII、JTAG接口的低電壓轉(zhuǎn)換

Samtec小課堂 | 兩分鐘了解JTAG連接器

SN74LVT8996-EP 多點(diǎn)可尋址IEEE標(biāo)準(zhǔn)1149.1(JTAG)TAP收發(fā)器數(shù)據(jù)表

SCANSTA111增強(qiáng)型掃描橋多點(diǎn)可尋址IEEE 1149.1(JTAG)端口數(shù)據(jù)表

SCANSTA112 7端口多點(diǎn)IEEE 1149.1(JTAG)多路復(fù)用器數(shù)據(jù)表

IEEE 1149.7擴(kuò)展和改進(jìn)JTAG

IEEE 1149.7擴(kuò)展和改進(jìn)JTAG

評論