1,reg與wire的區別:

相同點:

都能表示一種類型類型。

不同點:

wire

連線型數據,線網類型;

表示元件間的物理連線,不能保存數據;

線網是被驅動的,可以用連續賦值語句或把元件的輸出連接到線網等方式進行驅動;

給線網提供驅動的賦值元件就是“驅動源”,線網的值由驅動源來決定;

如果線網沒有連接到驅動源,線網的缺省值為“Z”。

reg:

寄存器型數據類型,通常用于對存儲單元進行描述;

這種變量可以保持它們自身的數值,直到該變量被指定了新的值為止 ;在過程被賦值的變量必須定義為reg型;

只能存放無符號數;

有符號數寄存器變量:integer 。

2,$stop:

表示停止命令,常用格式為,位于initial語句中:

#時間(N) $stop;

表示在(N)個時間單位后,停止仿真。

3,參數聲明parameter:

在程序中需要多次使用同一個數字時,可以考慮采用參數來提高代碼的簡潔度,降低代碼的設計量。

參數一經聲明,就視其為一個常量,在整個過程中值不在改變。

其定義方式如下:

《變量名》=《變量定義》;

例如:

parameter SET_TIME_1S=27‘b50_000_000;

//把常量50000000用標識符SET_TIME_1S來代替。

用同一個 parameter 同時定義多個參數時,各個參數之間用“ , ”來隔開。

使用參數可以提高代碼的可讀性,也便于修改。

4,仿真時的端口定義

與模塊輸入端口相連的信號端口是產生仿真信號的端口,需定義為reg類型;

與模塊輸出端口相連的信號端口是被輸出信號所驅動的端口,需要定義為wire類型;

5,阻塞與非阻塞賦值語句

1,非阻塞賦值語句

用操作符“《=”來標識“非阻塞賦值語句”;

在begin-end串行語句中,一條非阻塞賦值語句的執行不會阻塞下一條語句額執行,也就是說,在本條非阻塞型過程賦值語句對應的賦值操作執行完之前,下一條語句也可以開始執行。

仿真過程在遇到非阻塞型過程賦值語句后,首先計算其右端賦值表達式的值,然后等到仿真時間結束時將該計算結果賦值變量。也就是說,這種情況下的賦值操作是在同一時刻上的其他普通操作結束后才得以執行。

2,阻塞賦值語句

用操作符“=”來標識“阻塞賦值語句”;

在begin-end串行語句中的各條阻塞型過程賦值語句將它們在順序快中的排列次序依次得以執行。

阻塞型賦值過程賦值語句的執行過程:首先計算右端賦值表達式的值,然后立即將計算結果賦值給“=”左端的被賦值變量。

原文標題:verilog的一些技巧

文章出處:【微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

-

Reg

+關注

關注

0文章

20瀏覽量

11622 -

端口

+關注

關注

4文章

1044瀏覽量

32704 -

代碼

+關注

關注

30文章

4886瀏覽量

70221 -

Wire

+關注

關注

0文章

23瀏覽量

16041

原文標題:verilog的一些技巧

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

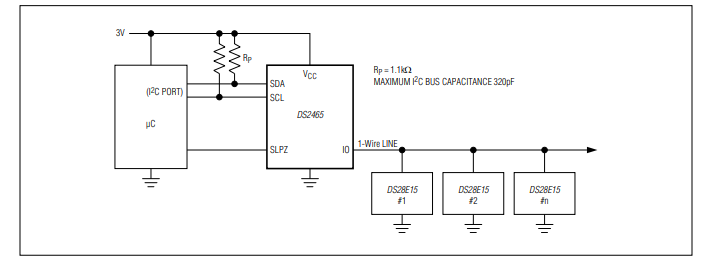

DS2465 DeepCover安全認證器具有SHA-256協處理器和1-Wire主機功能技術手冊

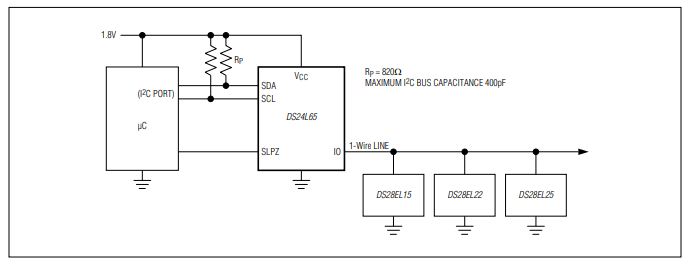

DS24L65 DeepCover安全認證器,具有SHA-256協處理器和1-Wire主機功能技術手冊

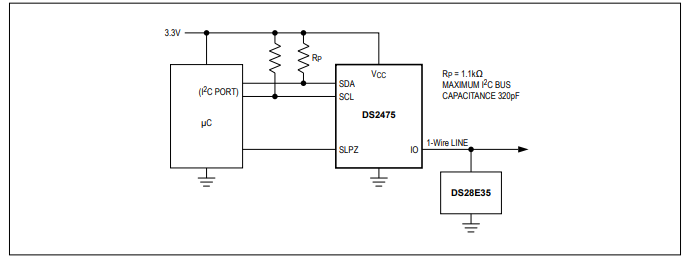

DS2475帶1-Wire主機的DeepCover ECDSA協處理器技術手冊

DS28E16 1-Wire SHA-3安全認證器技術手冊

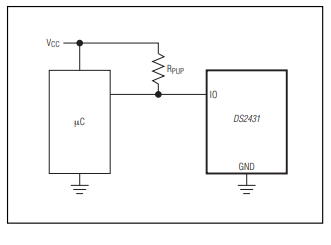

DS2431 1024位1-Wire EEPROM技術手冊

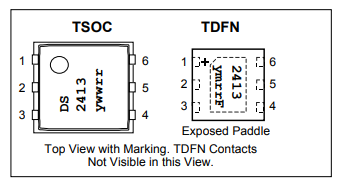

DS2413系列雙通道可編程1-Wire芯片技術手冊

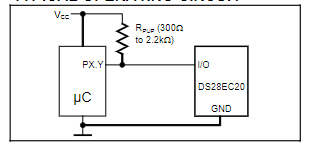

DS28EC20 20Kb 1-Wire EEPROM技術手冊

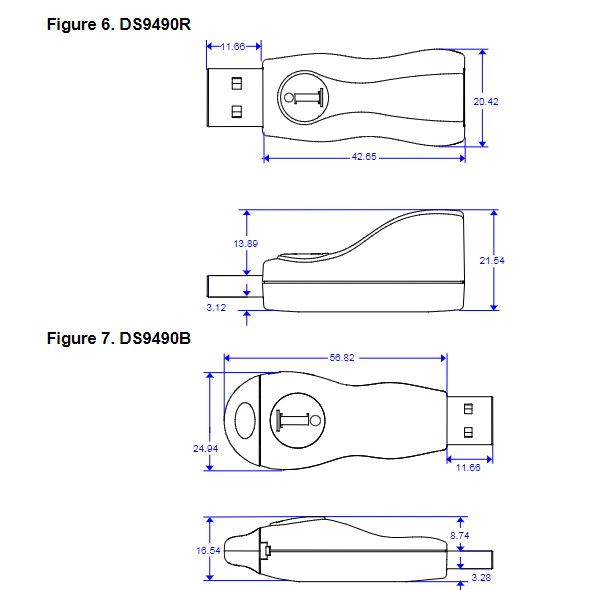

DS9490 USB至1-Wire/iButton適配器技術手冊

reg與wire的區別

reg與wire的區別

評論