現(xiàn)今,在低端數(shù)字通信應(yīng)用領(lǐng)域,我們隨處可見(jiàn)IIC(Inter-Integrated Circuit)和 SPI(Serial Peripheral Interface)的身影。原因是這兩種通信協(xié)議非常適合近距離低速芯片間通信。Philips(for IIC)和Motorola(for SPI)出于不同背景和市場(chǎng)需求制定了這兩種標(biāo)準(zhǔn)通信協(xié)議。

IIC開(kāi)發(fā)于1982年,當(dāng)時(shí)是為了給電視機(jī)內(nèi)的CPU和外圍芯片提供更簡(jiǎn)易的互聯(lián)方式。電視機(jī)是最早的嵌入式系統(tǒng)之一,而最初的嵌入系統(tǒng)是使用內(nèi)存映射(memory-mapped I/O)的方式來(lái)互聯(lián)微控制器和外圍設(shè)備的。要實(shí)現(xiàn)內(nèi)存映射,設(shè)備必須并聯(lián)入微控制器的數(shù)據(jù)線(xiàn)和地址線(xiàn),這種方式在連接多個(gè)外設(shè)時(shí)需大量線(xiàn)路和額外地址解碼芯片,很不方便并且成本高。

為了節(jié)省微控制器的引腳和和額外的邏輯芯片,使印刷電路板更簡(jiǎn)單,成本更低,位于荷蘭的Philips實(shí)驗(yàn)室開(kāi)發(fā)了“Inter-Integrated Circuit”,IIC或I2C ,一種只使用二根線(xiàn)接連所有外圍芯片的總線(xiàn)協(xié)議。最初的標(biāo)準(zhǔn)定義總線(xiàn)速度為100kbps。經(jīng)歷幾次修訂,主要是1995年的400kbps,1998的3.4Mbps。

有跡象表明,SPI總線(xiàn)首次推出是在1979年,Motorola公司將SPI總線(xiàn)集成在他們第一支改自68000微處理器的微控制器芯片上。SPI總線(xiàn)是微控制器四線(xiàn)的外部總線(xiàn)(相對(duì)于內(nèi)部總線(xiàn))。與IIC不同,SPI沒(méi)有明文標(biāo)準(zhǔn),只是一種事實(shí)標(biāo)準(zhǔn),對(duì)通信操作的實(shí)現(xiàn)只作一般的抽象描述,芯片廠(chǎng)商與驅(qū)動(dòng)開(kāi)發(fā)者通過(guò)data sheets和application notes溝通實(shí)現(xiàn)上的細(xì)節(jié)。

SPI總線(xiàn)介紹

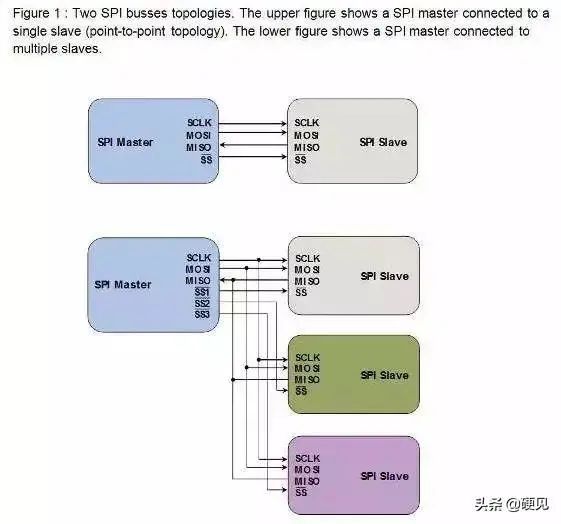

對(duì)于有經(jīng)驗(yàn)的數(shù)字電子工程師來(lái)說(shuō),用SPI互聯(lián)兩支數(shù)字設(shè)備是相當(dāng)直觀的。SPI是一種四根信號(hào)線(xiàn)協(xié)議(如圖1):

SCLK:Serial Clock (output from master);

MOSI;SIMO:Master Output,Slave Input;

MISO;SOMI:Master Input,Slave Output;

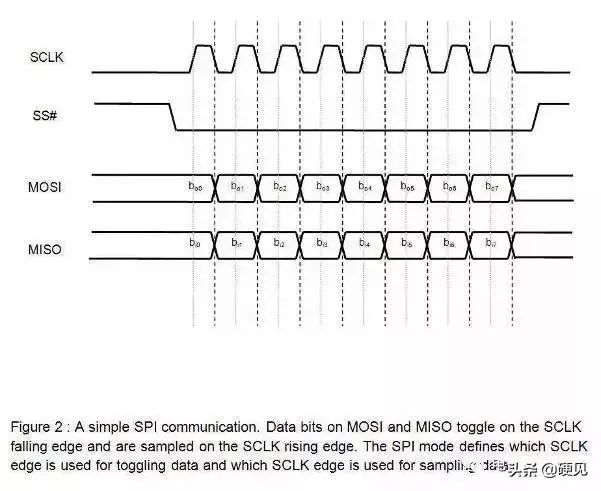

圖1 SPI是單主設(shè)備(single-master)通信協(xié)議,這意味著總線(xiàn)中的只有一支中心設(shè)備能發(fā)起通信。當(dāng)SPI主設(shè)備想讀/寫(xiě)從設(shè)備時(shí),它首先拉低從設(shè)備對(duì)應(yīng)的SS線(xiàn)(SS是低電平有效),接著開(kāi)始發(fā)送工作脈沖到時(shí)鐘線(xiàn)上,在相應(yīng)的脈沖時(shí)間上,主設(shè)備把信號(hào)發(fā)到MOSI實(shí)現(xiàn)“寫(xiě)”,同時(shí)可對(duì)MISO采樣而實(shí)現(xiàn)“讀”,如圖2:

圖2 SPI有四種操作模式:模式0、模式1、模式2和模式3.它們的區(qū)別是定義了在時(shí)鐘脈沖的哪條邊沿轉(zhuǎn)換(toggles)輸出信號(hào),哪條邊沿采樣輸入信號(hào),還有時(shí)鐘脈沖的穩(wěn)定電平值(即時(shí)鐘信號(hào)無(wú)效時(shí)是高還是低)。每種模式由一對(duì)參數(shù)刻畫(huà),它們稱(chēng)為時(shí)鐘極(clock polarity)CPOL與時(shí)鐘期(clock phase)CPHA。 主從設(shè)備必須使用相同的工作參數(shù)——SCLKCPOL和CPHA,才能正常工作。如果有多個(gè)從設(shè)備,并且它們使用了不同的工作參數(shù),那么主設(shè)備必須在讀寫(xiě)不同從設(shè)備間重新配置這些參數(shù)。 SPI不規(guī)定最大傳輸速率,沒(méi)有地址方案;SPI也沒(méi)規(guī)定通信應(yīng)答機(jī)制,沒(méi)有規(guī)定流控制規(guī)則。事實(shí)上,SPI主設(shè)備甚至并不知道指定的從設(shè)備是否存在。這些通信控制都得通過(guò)SPI協(xié)議以外自行實(shí)現(xiàn)。例如,要用SPI連接一支“命令-響應(yīng)控制型”解碼芯片,則必須在SPI的基礎(chǔ)上實(shí)現(xiàn)更高級(jí)的通信協(xié)議。 SPI并不關(guān)心物理接口的電氣特性,例如信號(hào)的標(biāo)準(zhǔn)電壓。在最初,大多數(shù)SPI應(yīng)用都是使用間斷性時(shí)鐘脈沖和以字節(jié)為單位傳輸數(shù)據(jù)的,但現(xiàn)在有很多變種實(shí)現(xiàn)了連續(xù)性時(shí)間脈沖和任意長(zhǎng)度的數(shù)據(jù)幀。 IIC總線(xiàn)介紹 與SPI的單主設(shè)備不同,IIC是多主設(shè)備的總線(xiàn),IIC沒(méi)有物理的芯片選擇信號(hào)線(xiàn),沒(méi)有仲裁邏輯電路,只使用兩條信號(hào)線(xiàn)——serial data(SDA)和serial clock(SCL)。

IIC協(xié)議規(guī)定:

每一支IIC設(shè)備都有一個(gè)唯一的七位設(shè)備地址。

數(shù)據(jù)幀大小為8位的字節(jié)。

數(shù)據(jù)(幀)中的某些數(shù)據(jù)位,用于控制通信的開(kāi)始、停止、方向(讀寫(xiě))和應(yīng)答機(jī)制。

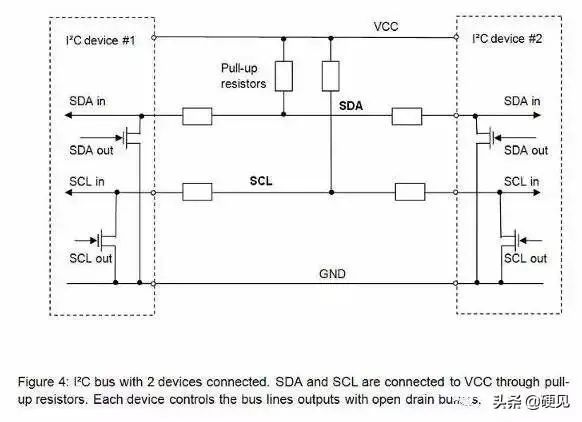

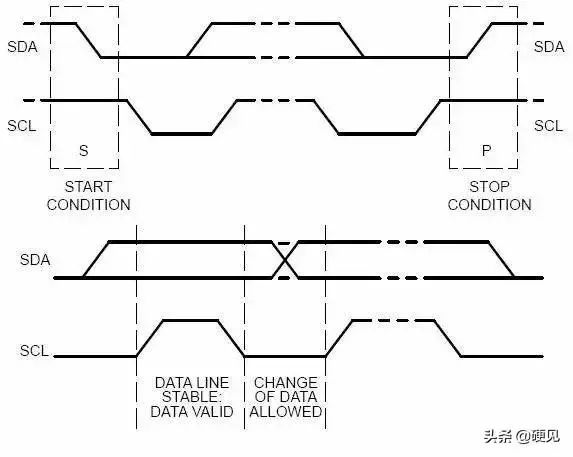

IIC數(shù)據(jù)傳輸速率有標(biāo)準(zhǔn)模式(100kbps)、快速模式(400kbps)和高速模式(3.4Mbps),另外一些變種實(shí)現(xiàn)了低速模式(10kbps)和快速+模式(1Mbps)。 物理實(shí)現(xiàn)上,IIC總線(xiàn)由兩根信號(hào)線(xiàn)和一根地線(xiàn)組成。兩根信號(hào)線(xiàn)都是雙向傳輸?shù)模瑓⒖紙D3。IIC協(xié)議標(biāo)準(zhǔn)規(guī)定發(fā)起通信的設(shè)備稱(chēng)為主設(shè)備,主設(shè)備發(fā)起一次通信后,其它設(shè)備均為從設(shè)備。

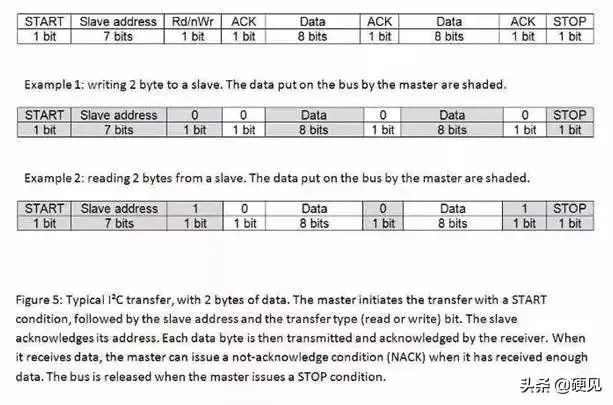

圖3 IIC通信過(guò)程大概如下。首先,主設(shè)備發(fā)一個(gè)START信號(hào),這個(gè)信號(hào)就像對(duì)所有其它設(shè)備喊:請(qǐng)大家注意!然后其它設(shè)備開(kāi)始監(jiān)聽(tīng)總線(xiàn)以準(zhǔn)備接收數(shù)據(jù)。接著,主設(shè)備發(fā)送一個(gè)7位設(shè)備地址加一位的讀寫(xiě)操作的數(shù)據(jù)幀。當(dāng)所設(shè)備接收數(shù)據(jù)后,比對(duì)地址自己是否目標(biāo)設(shè)備。如果比對(duì)不符,設(shè)備進(jìn)入等待狀態(tài),等待STOP信號(hào)的來(lái)臨;如果比對(duì)相符,設(shè)備會(huì)發(fā)送一個(gè)應(yīng)答信號(hào)——ACKNOWLEDGE作回應(yīng)。 當(dāng)主設(shè)備收到應(yīng)答后便開(kāi)始傳送或接收數(shù)據(jù)。數(shù)據(jù)幀大小為8位,尾隨一位的應(yīng)答信號(hào)。主設(shè)備發(fā)送數(shù)據(jù),從設(shè)備應(yīng)答;相反主設(shè)備接數(shù)據(jù),主設(shè)備應(yīng)答。當(dāng)數(shù)據(jù)傳送完畢,主設(shè)備發(fā)送一個(gè)STOP信號(hào),向其它設(shè)備宣告釋放總線(xiàn),其它設(shè)備回到初始狀態(tài)。

基于IIC總線(xiàn)的物理結(jié)構(gòu),總線(xiàn)上的START和STOP信號(hào)必定是唯一的。另外,IIC總線(xiàn)標(biāo)準(zhǔn)規(guī)定:SDA線(xiàn)的數(shù)據(jù)轉(zhuǎn)換必須在SCL線(xiàn)的低電平期,在SCL線(xiàn)的高電平期,SDA線(xiàn)的上數(shù)據(jù)是穩(wěn)定的。

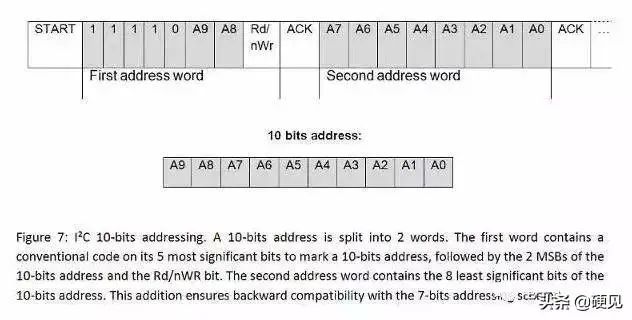

圖4 在物理實(shí)現(xiàn)上,SCL線(xiàn)和SDA線(xiàn)都是漏極開(kāi)路(open-drain),通過(guò)上拉電阻外加一個(gè)電壓源。當(dāng)把線(xiàn)路接地時(shí),線(xiàn)路為邏輯0,當(dāng)釋放線(xiàn)路,線(xiàn)路空閑時(shí),線(xiàn)路為邏輯1。基于這些特性,IIC設(shè)備對(duì)總線(xiàn)的操作僅有“把線(xiàn)路接地”——輸出邏輯0。 IIC總線(xiàn)設(shè)計(jì)只使用了兩條線(xiàn),但相當(dāng)優(yōu)雅地實(shí)現(xiàn)任意數(shù)目設(shè)備間無(wú)縫通信,堪稱(chēng)完美。我們?cè)O(shè)想一下,如果有兩支設(shè)備同時(shí)向SCL線(xiàn)和SDA線(xiàn)發(fā)送信息會(huì)出現(xiàn)什么情況。 基于IIC總線(xiàn)的設(shè)計(jì),線(xiàn)路上不可能出現(xiàn)電平?jīng)_突現(xiàn)象。如果一支設(shè)備發(fā)送邏輯0,其它發(fā)送邏輯1,那么線(xiàn)路看到的只有邏輯0。也就是說(shuō),如果出現(xiàn)電平?jīng)_突,發(fā)送邏輯0的始終是“贏家”。 總線(xiàn)的物理結(jié)構(gòu)亦允許主設(shè)備在往總線(xiàn)寫(xiě)數(shù)據(jù)的同時(shí)讀取數(shù)據(jù)。這樣,任何設(shè)備都可以檢測(cè)沖突的發(fā)生。當(dāng)兩支主設(shè)備競(jìng)爭(zhēng)總線(xiàn)的時(shí)候,“贏家”并不知道競(jìng)爭(zhēng)的發(fā)生,只有“輸家”發(fā)現(xiàn)了沖突——當(dāng)它寫(xiě)一個(gè)邏輯1,卻讀到0時(shí)——而退出競(jìng)爭(zhēng)。 十位設(shè)備地址 任何IIC設(shè)備都有一個(gè)7位地址,理論上,現(xiàn)實(shí)中只能有127種不同的IIC設(shè)備。實(shí)際上,已有IIC的設(shè)備種類(lèi)遠(yuǎn)遠(yuǎn)多于這個(gè)限制,在一條總線(xiàn)上出現(xiàn)相同的地址的IIC設(shè)備的概率相當(dāng)高。為了突破這個(gè)限制,很多設(shè)備使用了雙重地址——7位地址加引腳地址(external configuration pins)。IIC標(biāo)準(zhǔn)也預(yù)知了這種限制,提出10位的地址方案。 10位的地址方案對(duì)IIC協(xié)議的影響有兩點(diǎn):

第一,地址幀為兩個(gè)字節(jié)長(zhǎng),原來(lái)的是一個(gè)字節(jié)。

第二,第一個(gè)字節(jié)前五位最高有效位用作10位地址標(biāo)識(shí),約定是“11110”。

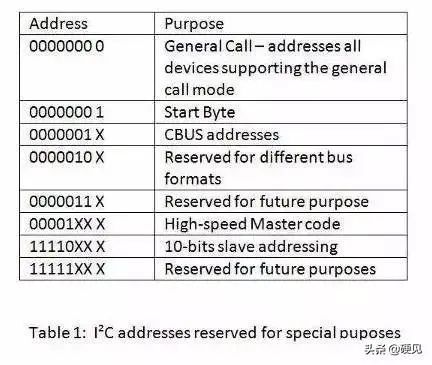

除了10位地址標(biāo)識(shí),標(biāo)準(zhǔn)還預(yù)留了一些地址碼用作其它用途,如下表:

時(shí)鐘拉伸 在IIC通信中,主設(shè)備決定了時(shí)鐘速度。因?yàn)闀r(shí)鐘脈沖信號(hào)是由主設(shè)備顯式發(fā)出的。但是,當(dāng)從設(shè)備沒(méi)辦法跟上主設(shè)備的速度時(shí),從設(shè)備需要一種機(jī)制來(lái)請(qǐng)求主設(shè)備慢一點(diǎn),這種機(jī)制稱(chēng)為時(shí)鐘拉伸。而基于IIC結(jié)構(gòu)的特殊性,這種機(jī)制得到實(shí)現(xiàn)。當(dāng)從設(shè)備需要降低傳輸?shù)乃俣鹊臅r(shí)候,它可以按下時(shí)鐘線(xiàn),逼迫主設(shè)備進(jìn)入等待狀態(tài),直到從設(shè)備釋放時(shí)鐘線(xiàn),通信才繼續(xù)。 高速模式 原理上講,使用上拉電阻來(lái)設(shè)置邏輯1,會(huì)限制總線(xiàn)的最大傳輸速度。而速度是限制總線(xiàn)應(yīng)用的因素之一。這也說(shuō)明為什么要引入高速模式(3.4Mbps)。在發(fā)起一次高速模式傳輸前,主設(shè)備必須先在低速的模式下(例如快速模式)發(fā)出特定的“High Speed Master”信號(hào)。為縮短信號(hào)的周期和提高總線(xiàn)速度,高速模式必須使用額外的I/O緩沖區(qū)。另外,總線(xiàn)仲裁在高速模式下可屏蔽掉。更多的信息請(qǐng)參與總線(xiàn)標(biāo)準(zhǔn)文檔。 IIC與SPI對(duì)比 我們來(lái)對(duì)比一下IIC和SPI的一些關(guān)鍵點(diǎn)。

1總線(xiàn)拓?fù)浣Y(jié)構(gòu)信號(hào)路由硬件資源耗費(fèi) IIC只需兩根信號(hào)線(xiàn),而標(biāo)準(zhǔn)SPI至少四根信號(hào),如果有多個(gè)從設(shè)備,信號(hào)需要更多。一些SPI變種雖然只使用三根線(xiàn)——SCLK、SS和雙向的MISO/MOSI,但SS線(xiàn)還是要和從設(shè)備一對(duì)一根。另外,如果SPI要實(shí)現(xiàn)多主設(shè)備結(jié)構(gòu),總線(xiàn)系統(tǒng)需額外的邏輯和線(xiàn)路。用IIC構(gòu)建系統(tǒng)總線(xiàn)唯一的問(wèn)題是有限的7位地址空間,但這個(gè)問(wèn)題新標(biāo)準(zhǔn)已經(jīng)解決——使用10位地址。從第一點(diǎn)上看,IIC是明顯的大贏家。

2數(shù)據(jù)吞吐傳輸速度 如果應(yīng)用中必須使用高速數(shù)據(jù)傳輸,那么SPI是必然的選擇。因?yàn)镾PI是全雙工,IIC的不是。SPI沒(méi)有定義速度限制,一般的實(shí)現(xiàn)通常能達(dá)到甚至超過(guò)10Mbps。IIC最高的速度也就快速+模式(1Mbps)和高速模式(3.4Mbps),后面的模式還需要額外的I/O緩沖區(qū),還并不是總是容易實(shí)現(xiàn)的。

3優(yōu)雅性 IIC常被稱(chēng)更優(yōu)雅于SPI。公正的說(shuō),筆者更傾向于認(rèn)為兩者同等優(yōu)雅和健壯。IIC的優(yōu)雅在于它的特色——用很輕盈的架構(gòu)實(shí)現(xiàn)了多主設(shè)備仲裁和設(shè)備路由。但是對(duì)使用的工程師來(lái)講,理解總線(xiàn)結(jié)構(gòu)更費(fèi)勁,而且總線(xiàn)的性能不高。

SPI的優(yōu)點(diǎn)在于它的結(jié)構(gòu)相當(dāng)?shù)闹庇^簡(jiǎn)單,容易實(shí)現(xiàn),并且有很好擴(kuò)展性。SPI的簡(jiǎn)單性不足稱(chēng)其優(yōu)雅,因?yàn)橐肧PI搭建一個(gè)有用的通信平臺(tái),還需要在SPI之上構(gòu)建特定的通信協(xié)議軟件。也就是說(shuō)要想獲得SPI特有而IIC沒(méi)有的特性——高速性能,工程師們需要付出更多的勞動(dòng)。另外,這種自定的工作是完全自由的,這也說(shuō)明為什么SPI沒(méi)有官方標(biāo)準(zhǔn)。IIC和SPI都對(duì)低速設(shè)備通信提供了很好的支持,不過(guò),SPI適合數(shù)據(jù)流應(yīng)用,而IIC更適合“字節(jié)設(shè)備”的多主設(shè)備應(yīng)用。

結(jié) 語(yǔ) 在數(shù)字通信協(xié)議簇中,IIC和SPI常稱(chēng)為“小”協(xié)議,相對(duì)Ethernet、USB、SATA、PCI-Express等傳輸速度達(dá)數(shù)百上千兆字節(jié)每秒的總線(xiàn)。但是,我們不能忘記的是各種總線(xiàn)的用途是什么。“大”協(xié)議是用于系統(tǒng)外的整個(gè)系統(tǒng)之間通信的,“小”協(xié)議是用于系統(tǒng)內(nèi)各芯片間的通信,沒(méi)有跡象表明“大”協(xié)議有必要取代“小”協(xié)議。IIC和SPI的存在和流行體現(xiàn)了“夠用就好”的哲學(xué)。回應(yīng)文首,IIC和SPI如此流行,它是任何一位嵌入式工程師必備的工具。

審核編輯 :李倩

-

微控制器

+關(guān)注

關(guān)注

48文章

7905瀏覽量

153689 -

通信協(xié)議

+關(guān)注

關(guān)注

28文章

999瀏覽量

40946 -

IIC

+關(guān)注

關(guān)注

11文章

306瀏覽量

39152

原文標(biāo)題:嵌入式系統(tǒng)中常用的IIC與SPI,這兩種通訊方式該怎么選?

文章出處:【微信號(hào):zhuyandz,微信公眾號(hào):FPGA之家】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

嵌入式應(yīng)用中常見(jiàn)的安全威脅

嵌入式開(kāi)發(fā)必備-RK3562演示Linux常用系統(tǒng)查詢(xún)命令(上)觸覺(jué)智能出品

新手怎么學(xué)嵌入式?

嵌入式系統(tǒng)開(kāi)發(fā)與硬件的關(guān)系 嵌入式系統(tǒng)開(kāi)發(fā)常見(jiàn)問(wèn)題解決

嵌入式系統(tǒng)與物聯(lián)網(wǎng)的結(jié)合

什么是嵌入式?一文讀懂嵌入式主板

嵌入式系統(tǒng)的原理和應(yīng)用

嵌入式系統(tǒng)的未來(lái)趨勢(shì)有哪些?

嵌入式常用總線(xiàn)有哪些

一種常用嵌入式開(kāi)發(fā)代碼庫(kù)

嵌入式系統(tǒng)中常用的IIC與SPI

嵌入式系統(tǒng)中常用的IIC與SPI

評(píng)論