DDR 接口在時鐘信號的上升沿和下降沿傳輸數(shù)據(jù)。該技術(shù)已被用作 DDR 同步動態(tài)隨機存取存儲器 (SDRAM)、微處理器前端總線、Ultra3 小型計算機系統(tǒng)接口 (SCSI) 和加速圖形端口總線的通信鏈路。在每個周期中,數(shù)據(jù)在時鐘的上升沿和下降沿進行采樣,最大數(shù)據(jù)頻率通常是時鐘頻率的兩倍。

DDR 技術(shù)的趨勢是朝著更高的數(shù)據(jù)速率和更低的電壓水平發(fā)展。為了使系統(tǒng)準(zhǔn)確運行,必須優(yōu)化其信號完整性性能并滿足某些最低要求。盡管 DDR2/DDR3 接口不如串行鏈路接口快,但信號完整性問題明顯更具挑戰(zhàn)性,DDR4 將成為更大的問題。這是由于這些接口的并行與串行性質(zhì)。串?dāng)_和電源噪聲等信號完整性問題在并行接口中占主導(dǎo)地位,并且隨著數(shù)據(jù)速率的提高而逐漸惡化。

隨著行業(yè)轉(zhuǎn)向 DDR3 和更高的數(shù)據(jù)速率,可以可靠地對數(shù)據(jù)進行采樣的數(shù)據(jù)有效窗口或單位間隔 (UI) 穩(wěn)步縮小,并且對信號完整性問題的敏感性急劇增加。在這些高數(shù)據(jù)速率下,封裝成為一個重要的考慮因素,尤其是在芯片互連方法方面。當(dāng)前的 IDT DDR3 封裝配置為引線鍵合芯片。以下討論將重點介紹將 DDR3 裸片更改為倒裝芯片類型的好處,并展示由此產(chǎn)生的性能優(yōu)勢。

DDR 接口挑戰(zhàn)

第一代 DDR 接口旨在以 400 Mtps 的最大數(shù)據(jù)速率發(fā)送和接收數(shù)據(jù),相應(yīng)的位周期或 UI 為 2.5 ns。這些接口通常使用 2.5 V 電源。當(dāng)前的 DDR3 接口運行速度為 1,600 Mtps,而基于 DDR4 的系統(tǒng)預(yù)計運行速度為 3,200 Mtps。在該數(shù)據(jù)速率下,每個 UI 僅約 312.5 ps,電源電壓降至 1.2 V。

DDR 技術(shù)的這種演變?yōu)槲锢砘ミB設(shè)計帶來了幾個挑戰(zhàn):

縮短位周期:更短的位周期導(dǎo)致更短的建立和保持時間幀,使得時鐘和數(shù)據(jù)信號之間的時序難以滿足。

快速信號邊沿:為了適應(yīng)不斷縮小的位周期,信號邊沿越來越尖銳,加劇了串?dāng)_和電源噪聲性能問題。

較低的電壓電平:對于 2.5 V 電源,5% 的噪聲容限導(dǎo)致芯片電源和接地節(jié)點的最大可接受噪聲電平為 125 mV。對于 1.2 V 電源,同樣 5% 的噪聲容限在相同的電源和接地節(jié)點上轉(zhuǎn)換為僅 60 mV 的可接受噪聲。互連設(shè)計和選擇成為滿足這些嚴(yán)格噪聲容限的關(guān)鍵組件。

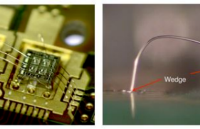

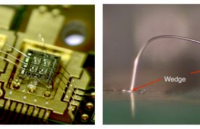

封裝是整個系統(tǒng)互連的關(guān)鍵組成部分,不理想的封裝互連選擇會顯著降低器件性能。當(dāng)前的 IDT DDR3 器件使用引線鍵合將芯片連接到封裝基板。引線鍵合的 3D 特性使得控制由攻擊信號發(fā)出的電磁場極其難以管理。一般來說,引線鍵合本質(zhì)上是電感性的,兩條相鄰導(dǎo)線之間的互感是信號間串?dāng)_的主要貢獻者。感應(yīng)焊線還會導(dǎo)致電源阻抗增加,從而導(dǎo)致芯片上的電源噪聲增加。

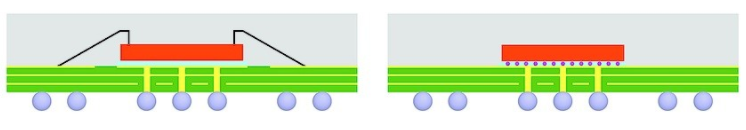

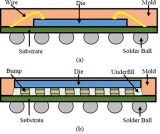

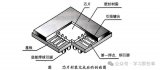

移除這些引線鍵合并將芯片到封裝互連轉(zhuǎn)換為倒裝芯片將消除信號完整性問題的一個關(guān)鍵來源,而不會影響整體封裝形狀因數(shù)。圖 1 顯示了兩種芯片到封裝互連類型的橫截面,所有其他特性都相同。

圖 1:兩種類型的芯片到封裝互連包括引線鍵合(左)和倒裝芯片(右)。

了解串?dāng)_

串?dāng)_是由于電磁信號能量通過互電容(電場耦合)和互感(磁場耦合)從一個導(dǎo)體泄漏到另一個導(dǎo)體而引起的。

電容串?dāng)_

在受害者-入侵者情況下,電容串?dāng)_將電流從入侵者線路注入到受害者線路上,串?dāng)_幅度與電壓變化率和兩條線路之間的互電容量成正比。注入的能量將分裂并流向受害線路的兩端——兩端是近端(靠近驅(qū)動器側(cè))和遠端(靠近接收器側(cè))。

感應(yīng)串?dāng)_

由于互感耦合引起的串?dāng)_會在受擾線上感應(yīng)出電壓,該電壓與驅(qū)動線上的電流變化率和兩個導(dǎo)體之間的互感大小成正比。由感應(yīng)電壓引起的電流從遠端流向近端(根據(jù)楞次定律),與驅(qū)動線的方向相反。

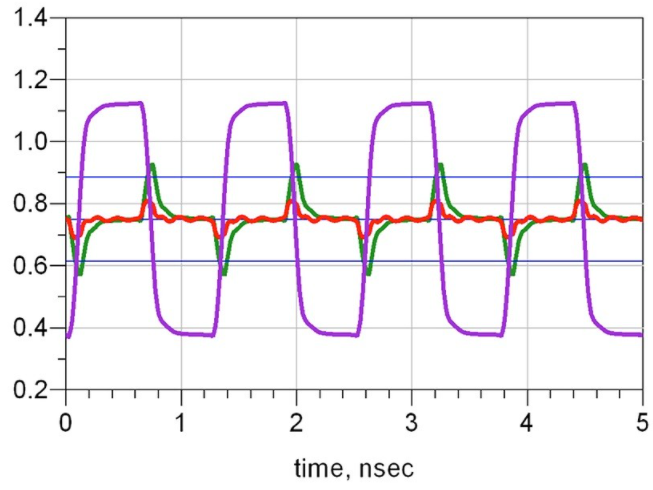

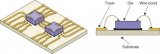

在基于基板的封裝中,串?dāng)_可分為封裝互連的傳輸線部分的串?dāng)_和封裝互連的 3D 結(jié)構(gòu)中的串?dāng)_,例如通孔、引線鍵合和焊球。在封裝結(jié)構(gòu)的傳輸線部分,串?dāng)_主要是電磁的,而在 3D 部分則主要是感應(yīng)的。對于大多數(shù)封裝應(yīng)用,遠端串?dāng)_幾乎總是負面的,將來自封裝 3D 部分的感應(yīng)串?dāng)_確定為主要的串?dāng)_機制。由于消除了引線鍵合(互感降低),封裝的倒裝芯片版本顯示的遠端串?dāng)_比引線鍵合版本少得多,如圖 2 所示。

圖 2:倒裝芯片封裝(紅線)在干擾線切換時在受擾線上產(chǎn)生的串?dāng)_比引線鍵合封裝(綠線)要小。

對模態(tài)延遲的串?dāng)_效應(yīng)

信號通過導(dǎo)體的飛行時間取決于相鄰耦合導(dǎo)體的切換方式。隨著導(dǎo)體之間的串?dāng)_增加,這種飛行時間的差異會加劇。在多導(dǎo)體系統(tǒng)中,有三種可能的開關(guān)模式:靜音模式、奇數(shù)模式和偶數(shù)模式:

靜默模式:如果受擾信號的上升和下降時間與相鄰耦合的干擾信號不一致,或者受擾信號保持靜默,這種切換模式稱為靜默模式。

奇模式:如果相鄰耦合干擾源的上升和下降時間與受擾信號一致,并且如果干擾源與切換信號異相 180° 切換,則這種切換模式稱為奇模式。

偶數(shù)模式:當(dāng)相鄰入侵者的開關(guān)與受害信號同相且同時,這種切換模式稱為偶數(shù)模式。

在耦合系統(tǒng)中,經(jīng)歷奇模式切換的信號總是最早到達接收器,其次是處于安靜模式的信號,最后是經(jīng)歷偶模式的信號。隨著串?dāng)_的增加,I/O 組中的切換信號之間的信號飛行時間擴展也會增加。在使用公共時鐘對多個并行信號位進行采樣的 DDR 類型系統(tǒng)中,這種由串?dāng)_引起的偏移的擴展會對可用于正確時鐘的建立和保持時間窗口產(chǎn)生不利影響。并且隨著數(shù)據(jù)速率隨著 UI 中的相關(guān)縮小而增加,減少串?dāng)_以改善建立/保持時間窗口將變得至關(guān)重要。

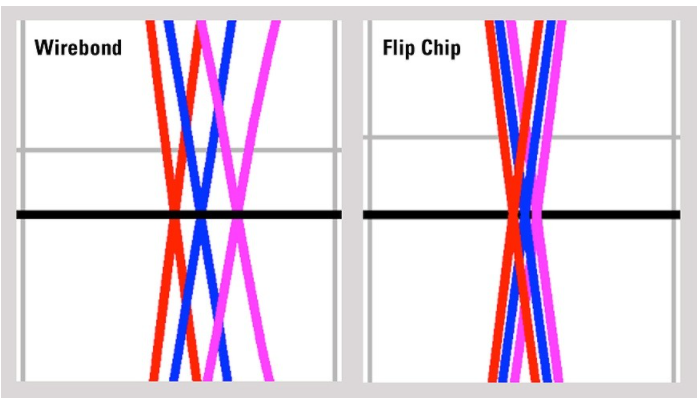

圖 3 比較了兩種封裝類型的模態(tài)延遲擴展。引線鍵合延遲更加分散,總模態(tài)延遲擴展為 41 ps,而倒裝芯片變化僅為 15 ps。由于 DDR4 應(yīng)用程序的 UI 預(yù)計將是 DDR3 的一半,引線鍵合封裝的封裝偏差增加將使時序難以滿足,因此倒裝芯片將成為首選的互連選項。

圖 3:在模態(tài)延遲擴展的比較中,引線鍵合封裝比倒裝芯片封裝顯示出更大的延遲擴展,紅色為奇數(shù)模式,藍色為安靜模式,粉紅色為偶數(shù)模式。

向芯片供電

有效地向芯片供電需要降低從芯片電源和接地節(jié)點向外看的供電網(wǎng)絡(luò)的輸入阻抗。封裝類型和芯片到封裝基板互連技術(shù)是整個系統(tǒng)供電網(wǎng)絡(luò)的關(guān)鍵組成部分。封裝阻抗很大程度上取決于由電源和接地互連形成的環(huán)路面積以及所使用的芯片到封裝互連方法的類型。從該環(huán)路中消除引線鍵合可降低環(huán)路電感,從而將阻抗降低 50% 以上,從而降低芯片上的電源噪聲。降噪幅度將是最佳 DDR4 接口性能的要求。

由于采用 DDR4 將需要更嚴(yán)格的噪聲和時序預(yù)算,倒裝芯片將成為芯片到封裝互連的首選技術(shù)。在這些高數(shù)據(jù)速率下,固有的電感性引線鍵合會影響串?dāng)_、時序和電源噪聲性能。通過提供優(yōu)于引線鍵合互連的關(guān)鍵優(yōu)勢,倒裝芯片顯著提高了 DDR 接口的重要性能指標(biāo)。

審核編輯:郭婷

-

電源

+關(guān)注

關(guān)注

185文章

18262瀏覽量

254967 -

芯片

+關(guān)注

關(guān)注

459文章

52145瀏覽量

436000 -

DDR

+關(guān)注

關(guān)注

11文章

731瀏覽量

66366

發(fā)布評論請先 登錄

引線鍵合替代技術(shù)有哪些

芯片封裝中的四種鍵合方式:技術(shù)演進與產(chǎn)業(yè)應(yīng)用

銅線鍵合IMC生長分析

引線鍵合檢測的基礎(chǔ)知識

倒裝芯片的優(yōu)勢_倒裝芯片的封裝形式

通過從引線鍵合切換到倒裝芯片來提高DDR性能

通過從引線鍵合切換到倒裝芯片來提高DDR性能

評論