FPGA 可以支持具有超過 2000 萬個等效門、處理器平臺和一系列通信、數字信號處理 (DSP) 和其他功能塊的設計。這些設備與過去的簡單可編程芯片相去甚遠,過去設計人員可以快速將幾千個邏輯門加載到 FPGA 中并立即看到它們運行。今天的設備需要一個全面的驗證策略,就像 ASIC 一樣詳盡。

傳統FPGA驗證

早期的 FPGA 設計流程包括輸入門級原理圖設計,將其下載到測試板上的設備上,然后使用真實測試數據驗證整個系統。即使只有幾千個門,很明顯,在下載之前對設計進行某種形式的仿真提供了一種通過早期檢測解決問題的更簡單、更快捷的方法。

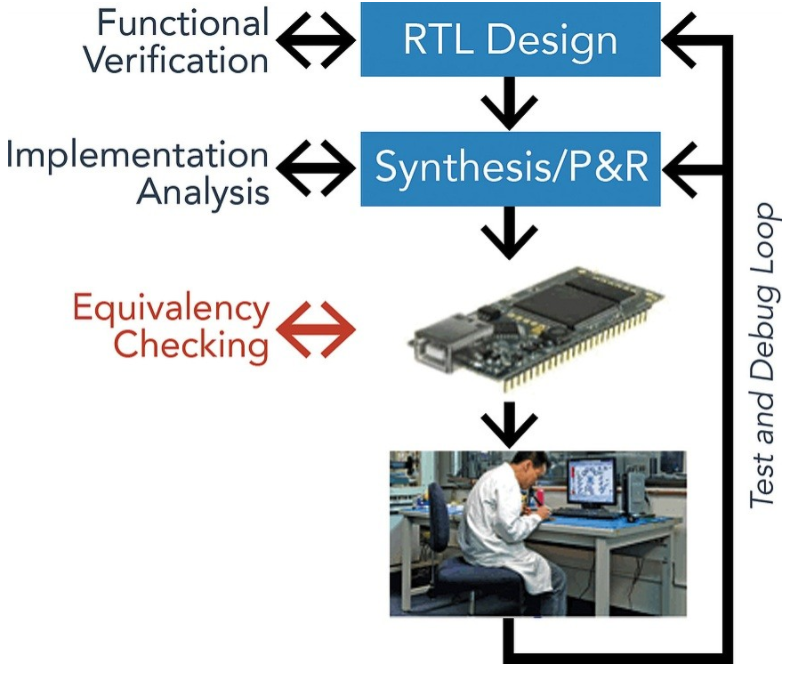

隨著 FPGA 技術的改進,更先進的設計技術是不可避免的。與 ASIC 設計類似,硬件描述語言 (HDL) 的使用變得司空見慣,并且設計的黃金表示從門轉移到了寄存器傳輸級 (RTL) 代碼。高級仿真用于在綜合之前對設計進行徹底的功能驗證,如今,所有高級 ASIC 功能驗證技術也用于 FPGA RTL 代碼。

然而,綜合后的 FPGA 驗證是另一回事。

依賴于制造的驗證

ASIC 和定制 IC 制造成本高、耗時且風險大。這導致了嚴格的簽核過程,最終設計以多種方式進行測試,以確保其正確性。此外,硬件仿真通常用于大型 IC,以使用真實數據和/或將在生產中運行的軟件進一步測試設備。

當然,FPGA 是不同的。由于 FPGA 可能會根據需要多次快速更新新設計代碼以使其正確,因此似乎沒有必要進行詳盡的簽核和單獨的仿真。

FPGA 的一個特別有用的特性是快速原型設計的能力。事實證明,這對于高速驗證非常寶貴,FPGA 甚至被用于針對其他 IC 類型的原型設計。事實上,由于這一特性,一些仿真器將 FPGA 作為其核心技術。

過去,假設對于大型 FPGA,對 RTL 代碼進行功能測試并對原型設備本身進行最終檢查就足夠了。然而,現在正在使用具有數百萬個等效門的 FPGA,新的設計流程要求改變了這種情況。

大型 FPGA 設計流程問題

可以將兩種類型的硬件錯誤引入 IC,包括 FPGA。在功能驗證期間消除了人為錯誤造成的設計錯誤。另一方面,系統性問題是由自動化設計改進工具鏈引入的,通常不會通過功能驗證過程進行檢查。如果它們進入最終設備,它們可能很難被發現和損壞。

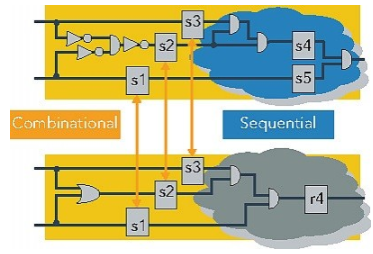

高質量的 FPGA 解決方案依賴于工具鏈的有效性,尤其是綜合和布局布線 (P&R) 功能提供的優化。寄存器與可用寄存器間邏輯的比率是固定的,如果該比率在設計代碼中不平衡,則允許浪費矩陣的部分。因此,觸發器位置相對于邏輯門發生變化的順序優化是重要的 FPGA 綜合和 P&R 能力(圖 1)。

圖 1:基本 FPGA 設計。

這些要求促使 FPGA 供應商投資于復雜的、最先進的綜合技術。為了設計出最高質量的設計,在這些工具中采用了極其積極的優化,這是整個 FPGA 設計結果質量 (QoR) 的關鍵驅動因素。

對于較小的 FPGA,由 RTL 代碼細化過程導致的系統性錯誤相對不常見,并且會在硬件內 FPGA 的最終測試期間發現。對于利用現代設計流程的大型 FPGA,這種假設已被證明是有缺陷的,并可能導致嚴重的設計問題。

系統性錯誤的等價檢查解決方案

采用積極優化的綜合和 P&R 工具的組合容易出現系統錯誤。因為這些工具對 RTL 代碼中看似微小的差異很敏感,所以不可能測試每個設計和工具優化組合。因此,通過提高優化級別并檢查以確保不會為特定設計引入系統錯誤,可以獲得最佳結果。

由于系統設計問題的性質,在大型 FPGA 中測試門級設計表示已成為一項關鍵要求。系統性問題可能發生在 FPGA 中與正在開發的設計部分幾乎沒有關系的任何地方。它們通常會產生意外行為或由不尋常的極端情況觸發,從而使驗證測試的創建變得復雜且耗時。它們對調試很煩人,因為通常必須在幾乎沒有關于問題根源的信息的情況下檢查整個設計。最糟糕的是,他們可以輕松地將其制成最終產品,從而導致后期制作重新旋轉。

用于 ASIC 設計的基于形式驗證的等效檢查 (EC) 將 RTL 代碼與派生的門級等效代碼進行了詳盡的比較,特別針對系統問題(圖 2)。由于 RTL 代碼已經過全面驗證,因此整體解決方案代表了保證設計功能的最有效方式。

圖 2:等價檢查必須支持順序優化。

對于 FPGA 設計,需要一種能夠支持最新 FPGA 綜合工具利用的高級順序優化的新型 EC。由于 FPGA 設計流程在邏輯設計空間內移動鎖存器,標準等效性檢查無法輕松地將 RTL 寄存器映射到門觸發器。這可以通過利用更常見的與屬性檢查相關的高級形式技術來解決,例如,OneSpin 的 360 EC-FPGA 中使用的 EC 工具的一項新的重要功能。這是從 FPGA 設計中有效消除系統錯誤的絕對要求。

在 FPGA 流程中使用 EC 有以下好處:

確信在最終 FPGA 測試中觀察到的任何問題都與設計相關,并且不是系統性的,從而推動了更快、更輕松的調試過程。

消除了創建一系列復雜測試以針對系統錯誤或嘗試預測系統錯誤故障條件的耗時需求。

確信最終設計中不存在系統性、極端情況錯誤,確保經過驗證的 RTL 代碼和門級最終設計之間的一致性。

有信心利用可用的最激進的優化,而不必擔心引入錯誤,從而實現最高質量的設計。

EC 的使用直接關系到最終設計質量、可靠性、設計進度和工程效率。毫不奇怪,全球許多使用大型 FPGA 的電子公司都在使用它。

FPGA實現驗證

隨著 FPGA 變得越來越大和越來越復雜,它們的設計和功能驗證趨向于 ASIC。在現代 FPGA 設計流程的先進性的推動下,這種趨勢現在正在擴展到實現驗證領域。EC 現在是該流程的必要組成部分,保留了 FPGA 生產過程中的固有效率。

審核編輯:郭婷

-

FPGA

+關注

關注

1643文章

21963瀏覽量

614078 -

asic

+關注

關注

34文章

1242瀏覽量

121985

發布評論請先 登錄

極端溫度下的守護者:BMS測試儀如何驗證電池熱失控防護策略?

工程碩士論文——基于FOC的永磁同步電機全速域無位置傳感器控制策略

AMD技術賦能西門子FPGA原型設計解決方案

芯華章發布FPGA驗證系統新品HuaProP3

芯華章推出新一代高性能FPGA原型驗證系統

國產EDA公司芯華章科技推出新一代高性能FPGA原型驗證系統

什么是回歸測試_回歸測試的測試策略

數字芯片設計驗證經驗分享文章 實際案例說明用基于FPGA的原型來測試、驗證和確認IP——如何做到魚與熊掌兼

基于場景的自動駕駛驗證策略

FPGA在圖像處理領域的優勢有哪些?

FPGA算法工程師、邏輯工程師、原型驗證工程師有什么區別?

優化 FPGA HLS 設計

大規模 SoC 原型驗證面臨哪些技術挑戰?

驗證FPGA設計的策略

驗證FPGA設計的策略

評論